13.6 АЦП I: Параллельные

==903

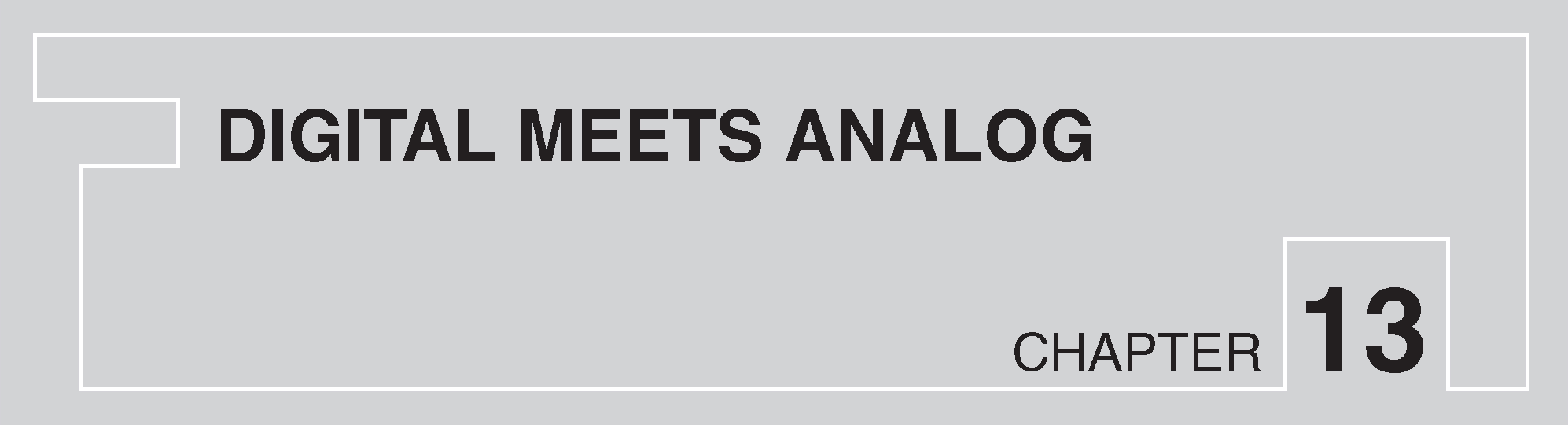

Это, возможно, самый простой принцип построения АЦП, и одновременно самый быстрый ( см. табл. 13.4 ). Входное напряжение подаётся одновременно на вход 2n одинаковых компараторов. В качестве опорных напряжений выступают потенциалы с 2n-стадийного делителя напряжения. Выходы компараторов образуют «термометрический» ( линейный ) код. Номер самого старшего сработавшего компаратора превращается приоритетным шифратором в n-разрядный выходной код. Рис. 13.25 даёт концептуальное изображение данного метода. Здесь он реализован на дискретных компараторах и стандартной жёсткой логике. Собирать в «железе» именно эту схему не стоит, пусть этим занимаются производители кремния. В такой простой одностадийной схеме время задержки от входа до выхода равно сумме задержек компаратора, шифратора и выходного буфера ( если он есть ). Примером промышленной реализации именно такой схемы может служить MAX1003 - двухканальный 6-разрядный преобразователь, делающий 90 миллионов выборок в секунду ( Msps ) и имеющий задержку от входа до выхода один такт.

Рис. 13.25 АЦП с параллельным кодированием ( «флэш» )

13.6.1 Модифицированная параллельная схема

В жизни простая параллельная архитектура была вытеснена модифицированными схемами: «полупараллельной» , «субдиапазонной» , «с интерполяцией» и «конвейерной» . Новые варианты предполагают наличие шагов последовательного приближения или частичные преобразования, таким образом имеется некоторая задержка ( или латентность ) с момента выборки входного напряжения до появления выходного кода. Данное свойство не обязательно снизит максимальную скорость измерения. На самом деле обычно происходит ровно обратное явление: разделение общего процесса на несколько задач меньшей разрядности серьёзно повышает общую скорость. Частично оцифрованные аналоговые остатки ещё движутся по конвейеру на основе конденсаторов, а АЦП уже начинает новое измерение. В таких преобразователях первая грубая прикидка ( например, до двух старших разрядов ) продолжается в каскадах последовательного приближения, работающих с остатками ( разницей между входным напряжением и первым грубым 2-разрядным результатом ). Так устроен ADC10D1500 - сдвоенный преобразователь на 1.5 Gsps в каждой секции ( их можно включить попеременно и получить одино 10-разрядное АЦП со скоростью 3.6 Gsps ). Его латентность - 35 тактов.

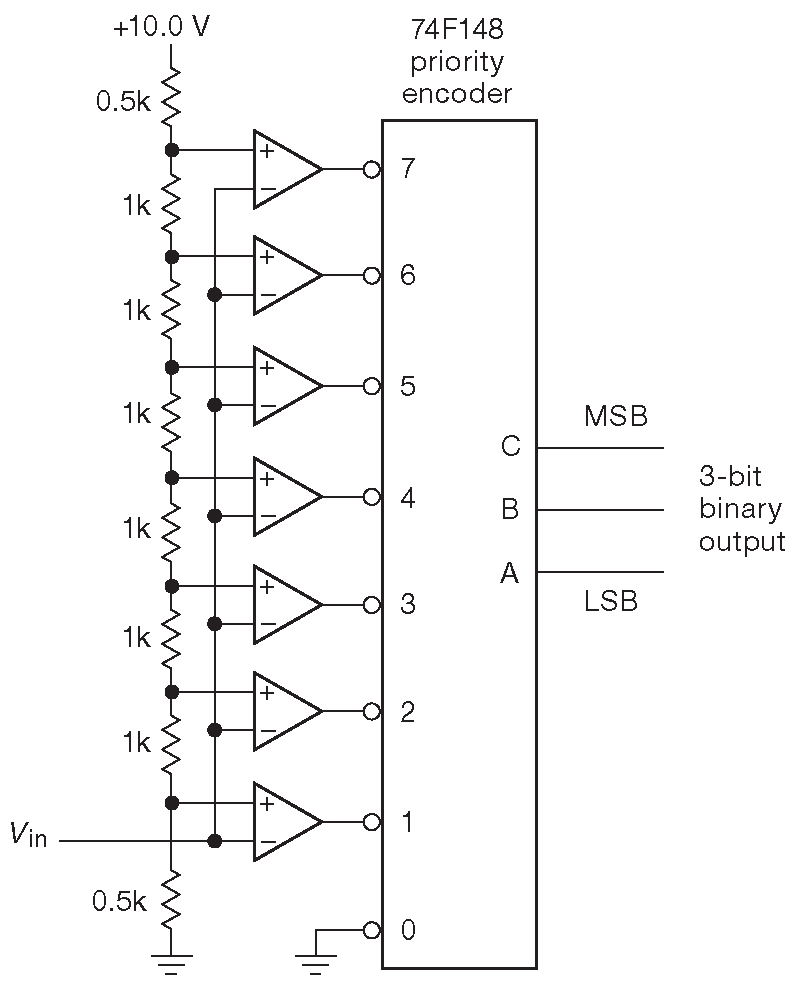

Возможно, самым простым вариантом такой конструкции является АЦП с частичным параллельным преобразованием полу-флэш . В нём измерение распадается на два участка: предварительная грубая параллельная дискретизация до половинной итоговой точности, получение из этого результата с помощью внутреннего ЦАПа промежуточного аналогового напряжения и второй этап параллельного преобразования «ошибки» между входным напряжением и промежуточным потенциалом с выхода ЦАПа, на котором появляется младшая половина разрядов ( рис. 13.26 ). С помощью такого приёма можно получить недорогой АЦП с относительно низким потреблением энергии. Примерами могут служить TLC0820 и TLC5540 фирмы TI и AD7820 производства ADI. Это недорогие 8-разрядные АЦП с латентностью два-три цикла тактирования и умеренными скоростями преобразования ( у TLC5540 - 40 Msps ).

Рис. 13.26 АЦП с частичным параллельным преобразованием

==904

Как уже упоминалось выше, более сложные АЦП используют схемы конвейерного типа, в которых аналоговые «остатки» от предыдущих этапов последовательно проходят цепочку относительно грубых преобразований. Скажем, AD9244 ( ADI ) использует 10-стадийный конвейер, чтобы получить 14-разрядов на 65 Msps с задержкой 8 тактов. AD9626 той же фирмы разменял точность на скорость: 12 разрядов, 250 Msps, 6 тактов задержки. Приведём цитату из его справочных данных:

«Конвейерная архитектура позволяет первому каскаду заняться новым преобразованием, в то время как другие каскады ещё обрабатывают предыдущие выборки. Каждый измерительный каскад, кроме последнего, состоит из грубого параллельного АЦП, подключённого к ЦАПу на переключаемых конденсаторах и межкаскадному усилителю. Усилитель масштабирует разницу между восстановленным напряжением на выходе ЦАПа и входным напряжением и передаёт её на вход следующего каскада конвейера.... Последний каскад состоит только из АЦП.»

Такой же подход наблюдается в ADS5547 ( TI ) - 14-стадийный конвейерный АЦП, выполняющий 14-разрядные измерения на скорости 210 Msps с латентностью 14 тактов ( этим ребятам нравится число 14 ). На момент написания книги самые быстрые результаты были у ADS5474 ( 14 разрядов, 400 Msps ) и ADC16DX370 ( 16 разрядов, 370 Msps ).

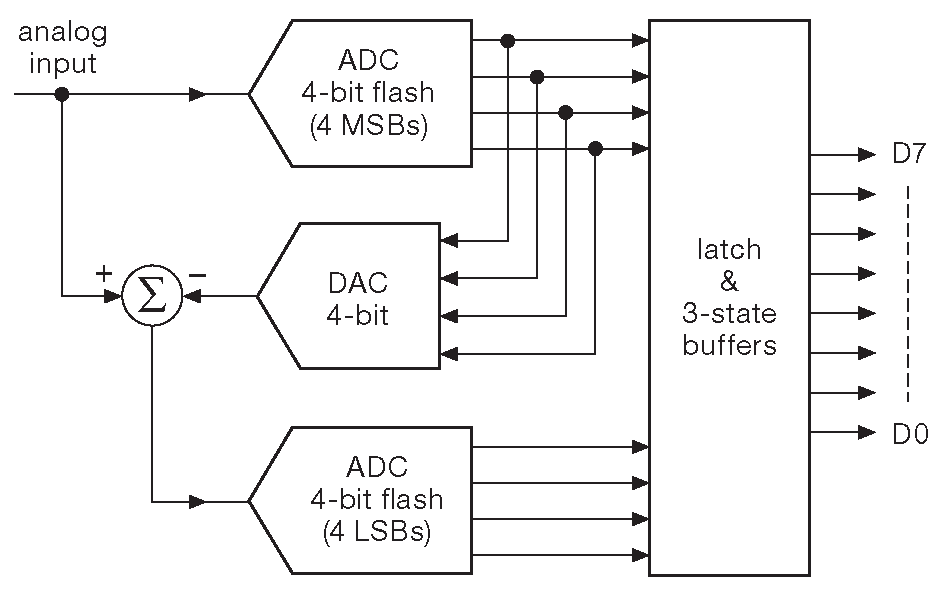

Архитектура с многодиапазонной параллельной дискретизацией достигает тех же целей ( т.е. точного результата из грубых и уточняющих промежуточных значений ), но более интересным методом. Он не требует конвейера и последовательных действий. Вместо этого входное напряжение проходит сквозь аналоговую схему размножения входного сигнала, выполненную на цепочке перекрёстно включённых дифференциальных усилителей, которая отображает полное входное напряжение на множество одинаковых повторяющихся и соприкасающихся диапазонов. Грубая схема выбирает нужный диапазон ( старшие биты ), который затем оцифровывается с помощью параллельного АЦП ( младшие биты ). Выходное значение собирается из этих двух групп битов, см. рис. 13.27 . Такую технику использует серия «сверхскоростных АЦП» фирмы National Semiconductor/TI. На данный момент получены 12 разрядов на 3.6 Gsps ( ADC12D1800 ). Нужно изрядно попотеть, чтобы заставить всё это хорошо работать, но, как говорится, «это выходит за рамки данной публикации».

Рис. 13.27 Параллельный АЦП с многодиапазонной ( folding ) архитектурой

Параллельные преобразователи используются в основном в дискретизации меняющихся сигналов, даже если общая скорость преобразования невелика, потому что их высокая скорость ( а точнее, малое апертурное время - длительность интервала выборки ) гарантирует отсутствие изменения сигнала в ходе преобразования. Альтернативой им служат медленные АЦП, которые будут описаны дальше. Они обычно нуждаются в схеме выборки-хранения, чтобы «замораживать» сигнал на время преобразования. Заметим, что будет или не будет латентность АЦП влиять на результат, зависит от конкретной схемы: что подходит осциллографу, то убьёт цепь обратной связи.

13.6.2 Входные схемы для параллельных АЦП

Современные АЦП несколько отличаются от первых простых преобразователей. Их возможности гораздо выше, но они капризные, их нельзя включать только на время измерений, и они очень зависимы от качества питания и цифровых линий связи. Теперь нельзя просто взять ОУ и подключить его к АЦП.

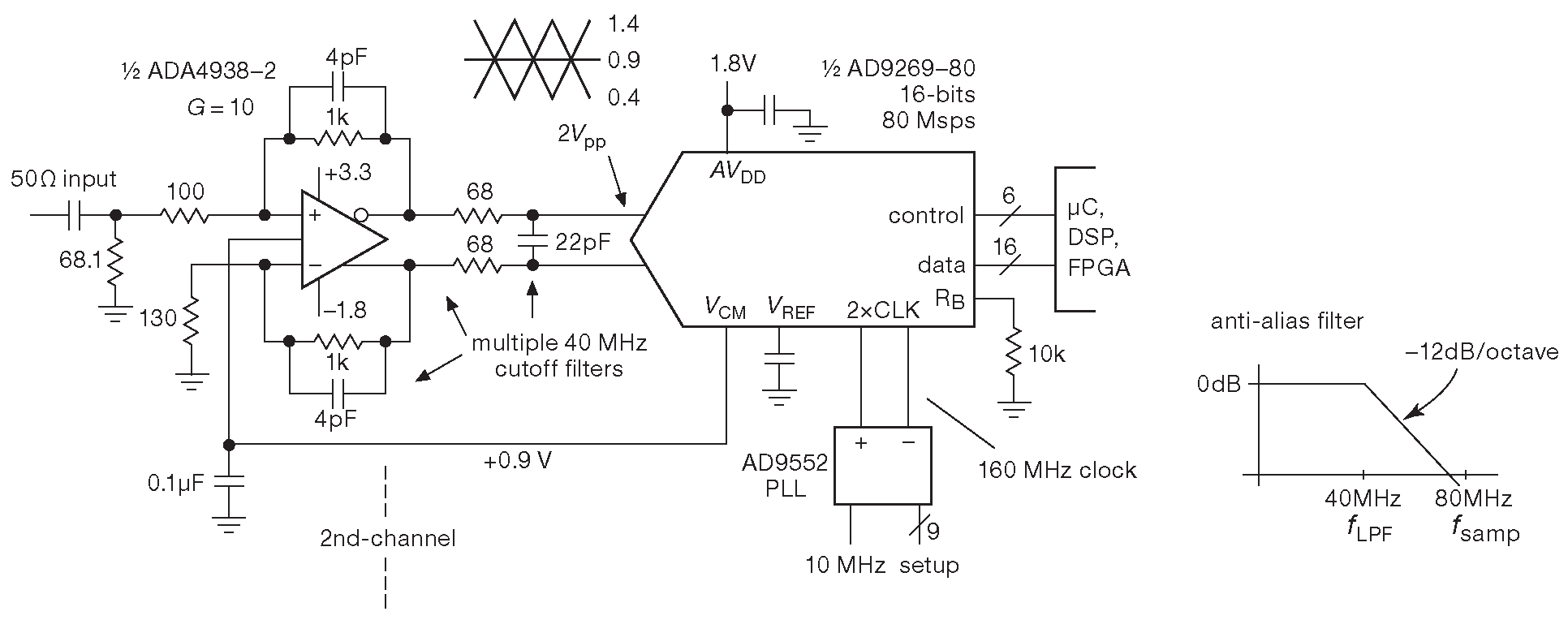

Покажем это на примере. На рис. 13.28 изображён двухканальный 16-разрядный параллельный АЦП, способный работать на радиочастотах и идеально подходящий для оцифровки I- и Q-сигналов для радиосистем с программируемыми параметрами. На схеме имеется дифференциальный усилитель ( §5.17 ), выполняющий задачи, которые аналогичны упомянутым на рис. 5.102 и 5.103 . В ходе разработки выяснилось, что первоначальная схема очень похожа на окончательное решение, но очень много времени было потрачено на всякие мелочи, изучение справочных данных и рекомендаций, рассмотрение альтернативных вариантов, имеющих иной набор требований и ограничений, и на доводку схемы.

Рис. 13.28 Быстрые АЦП часто имеют дифференциальную схему включения как у этого двухканального 16-разрядного 80 Msps ( 40 MHz ) RF АЦП. Радиочастотные схемы, подобные этой, требуют точного и стабильного источника тактовых импульсов, здесь используется генератор с фазовой автоподстройкой ( §13.13 )

AD9269 32 - параллельный АЦП, но многие его проблемы свойственны и другим типам преобразователей. Некоторые сигма-дельта и схемы последовательного приближения требуют ставить на вход изолирующую цепочку из двух последовательных резисторов и параллельного конденсатора, причём некоторые АЦП последовательного приближения, из которых пытаются выжать всё возможное, оказываются очень чувствительны к выбору номиналов этой троицы.

==905

Table 13.4 Selected Fast A-to-D Converters® Notes: (a) listed in order of increasing sample rate, for the fastest member of a family; unless noted otherwise, inputs are differential, with sampling capacitors at the inputs introducing switching transients that require low drive impedance and RC input networks; all guarantee no missing codes, (m) min or max. ( t ) typical, (y ) includes int ref. Comments: A: input buffer, isolates sampling transients. B: both. C: n-line parallel CMOS. D: n/2-lane DDR LVDS /ch. F: 1024-lane LVDS at 440 MHz/ch. G: 1, 2, or 4 LVDS lanes/ch. I: interleave for 2x sampling rate. J: non-interleaved. K: fastest ADC; 320 interleaved 175 Msps SARs. L: n-lane LVDS /ch. N: negative only. O: one LVDS lane. P: programmable operating parameters, usually via SPI. R: resistor ladder and comparators. 8: single-ended input. VI: 3.3 V and 5V. V2: 1.8 V and 3.3 V.

==906

У 80-мегагерцовых АЦП предел Найквиста составляет 40 MHz и именно на такую частоту настроен входной дифференциальный 2R+C фильтр. Резисторы и конденсатор фильтра играют двоякую роль: во-первых, АЦП отлично реагирует на любой шум ( и белый, и прочие виды ) в полосе вплоть до 700 MHz , поэтому выше 40 MHz выход буферного усилителя должен быть чист и тих. Во-вторых, входной схеме выборки-хранения преобразователя для нормальной работы требуется небольшая порция заряда, которая вытягивается из входного конденсатора. Два резистора, кроме того, изолируют выход усилителя от конденсатора, что очень важно, потому что 1000-мегагерцовый ОУ не переносит непосредственную емкостную нагрузку. Таковы три задачи для трёх вспомогательных компонентов, которых не было в старые добрые времена.

Зачем нужен усилитель c дифференциальным выходом ? В общем случае на устройство с дифференциальными входами можно подавать однополярный сигнал на один вход и землю на другой, но в современных АЦП такое включение заметно увеличивает искажения и уполовинивает рабочий диапазон [* т.е. минус один разряд, а их и так мало ] . Зато выбор дифференциального усилителя превращается в увлекательное времяпрепровождение. Если смотреть в высокочастотную ( 500...1500 MHz ) группу в табл. 5.10 ( стр. 375 ), то не удаётся найти микросхему с высоким входным дифференциальным импедансом «\(Z_{in}( diff )\)». Нужен дополнительный 40-мегагерцовый спектральный фильтр, который отсекает очень интересные варианты с внутренними резисторами установки усиления, потому что средние точки их делителей недоступны. И, наконец, требуется усиление не меньшее 10 или 20 dB . Поэтому в итоге был выбран ADA4938 ( Analog Devices ) с заявленной полосой 1000 MHz 33 . Согласно графику его АЧХ величина GBW составляет 800 MHz , следовательно, \( f_{3db}\) = GBW/G =80 MHz , а значит, на 40 MHz ещё останется запас по усилению.

Усилители конфигурации _D ( рис. 5.96D ), подобные выбранному, имеют довольно низкий входной импеданс, особенно это касается высоких усилений, потому что \(Z_{in}\) =2\(R_g\) , а \(R_g=R_f/G\) . Итак, с высоким входным импедансом дело не выгорело. А как насчёт вездесущих 50-омных источников широкополосных сигналов? Если выбрать \(R_g\) =100 Ω , то тепловой шум 34 двух таких резисторов составит 1.8 mV/\(\sqrt{Hz}\) , т.е. будет гарантированно ниже, чем заявленный шум усилителя \(e_n\) =2.6 nV/\(\sqrt{Hz}\) .

Если поставить на входе 50-омный нагрузочный резистор, \(Z_{in}\) не будет равен в точности \(R_g\) 35 . В справочных данных приводится формула \[ Z_{in}=\cfrac{R_g}{\left(1-\cfrac{R_f}{2(R_g+R_f)}\right)} , \] в соответствии с которой найден нагрузочный резистор 68 Ω . Затем с помощью резистора 130 Ω выравнивается импеданс на инвертирующем входе. Мероприятия по подгонке входного импеданса изменили коэффициент усиления \(R_f=GR_g\) , поэтому, чтобы сохранить G =10 , приходится увеличивать \(R_f\) на 11% ( процесс поясняется в §5.17.4 ). Наконец, последний аккорд. Для перевода однополярного входа в дифференциальный требуется проверить полосу для «Vocm». По справочным данным частота «-3dB» для этого вывода усилителя равна 230 MHz , значит, с учётом ослабления в цепи обратной связи частота «-3dB» для полного дифференциального диапазона АЦП сократится до 24 MHz 36 .

==907

АЦП AD9269 требует внешнего тактирования, и в схему добавлен совместимый генератор с фазовой автоподстройкой AD9552 ( см. §13.13.6.H и табл. 13.13 ). Преобразователь позволяет поделить входную частоту пополам, чтобы получить внутренний тактовый сигнал с 50%-скважностью, чем стоит воспользоваться. Таким образом, для выборки с частотой 80 Msps требуется частота 160 MHz . Для опорной частоты 10 MHz требуется множитель 16 . Сигма-дельта модулятор в AD9552 поможет при необходимости получить и дробные частоты, а у АЦП есть и другие коэффициенты пересчёта тактового сигнала.

Последнее предупреждение ( если вам ещё мало ): джиттер . Графики в паспортных данных AD9269 сообщают, что для достижения самых лучших цифр отношения сигнал/шум ( 75...78 dB ) джиттер тактового сигнала должен составлять ( не падайте со стула! ) не более 0.2 ps ( или около 15 ppm за период измерения ). Для PLL AD9552 этот параметр равен 0.11 ps , т.е. в данном случае условия выполнены ( но запаса на вырост нет ). [* Джиттер разбирается в §7.1.10 ] .

13.6.3 Пример параллельного преобразователя с субдискретизацией

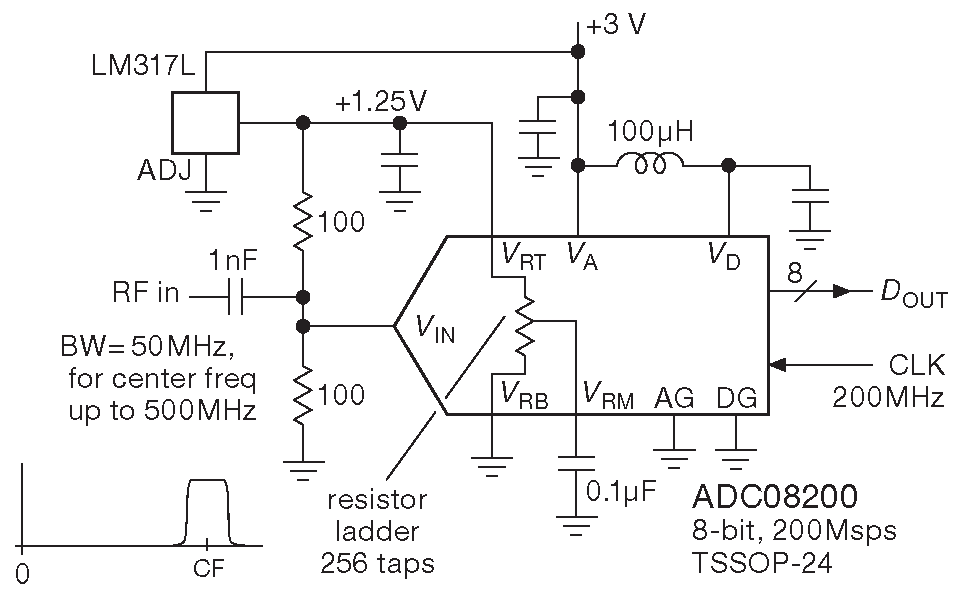

На рис. 13.29 показана чуть упрощённая схема преобразователя с «субдискретизацией». Интересующий сигнал группируется возле некоторой достаточно высокой частоты ( скажем 500 MHz ), а оцифровывается на скорости, которая значительно ниже, чем требуется по теореме Найквиста ( например, 200 Msps ). Такая схема будет работать, если выполнены два условия.

- Полоса сигнала должна удовлетворять критерию Найквиста, т.е. частота опроса должна как минимум вдвое превышать ширину рабочей полосы сигнала; и

- полный спектр сигнала на входе АЦП ( включая самые высокие его частоты ) должен укладываться в рабочую полосу преобразователя по аналоговому сигналу.

Рис. 13.29 Недорогой параллельный АЦП может оцифровывать ограниченный по полосе сигнал на частоте сильно превышающей предел Найквиста. Такой приём называют переносом частоты и выполняют с помощью генератора промежуточной частоты ( «LO» ) и умножителя

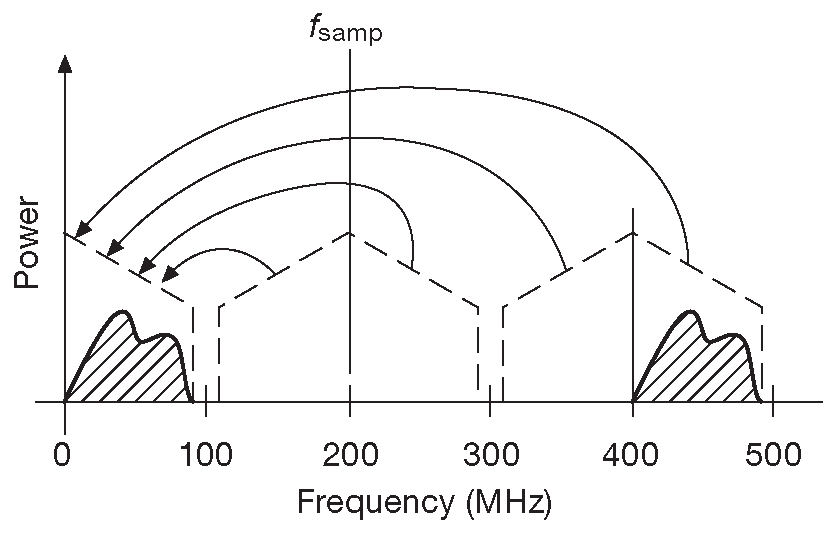

Первое условие требует наличия чётких границ полосы сигнала, задаваемых обычно полосовым фильтром. Второе требование подразумевает, что АЦП изначально проектировался в расчёте на такое применение. ADC08200 на схеме имеет полную полосу пропускания по мощности 500 MHz , притом что максимальная скорость измерения составляет 200 Msps ( а значит, подходит только для сигналов до 100 MHz ). Описываемая схема дискретизации использует факт появления фантомных копий спектра в его цифровом представлении. Подход нормальный, но необходимо учитывать, что в рабочей области частот, куда происходит перенос спектра в ходе оцифровки, не должно быть никаких посторонних сигналов ( см. рис. 13.30 ) 37 .

Рис. 13.30 Перенос частоты: система со скоростью опроса 200 Msps с успехом оцифровывает сигналы в основной полосе, простирающейся до границы 100 MHz . Но в цифровом представлении присутствуют фантомные копии и последовательности таких 100-мегагерцовых полос. Это обычно нежелательное свойство можно использовать, если вычистить с помощью фильтра спектр вне полосы сигнала, занимающего участок, к примеру, от 400 до 500 MHz . Тогда сигнал в этой области отлично оцифруется, как если бы он занимал полосу 0...100 MHz

В данном примере использовался относительно низкочастотный параллельный преобразователь фирмы National Semiconductor/TI. Он работает от +3V , проводит измерение с частотой до 200 Msps , выводит 8-разрядные данные через простой параллельный порт 38 и стОит менее $15 в единичных количествах. Его шкала преобразования состоит из 256 последовательных резисторов и требует внешней привязки потенциалов своих концов ( здесь земля для нижнего и +1.25 V для верхнего ) и обязательной развязки средней точки. Катушка индуктивности на 100 μH отвязывает аналоговое питание «Va» от цифрового шума на выводе «Vd». С учётом строго положительного рабочего диапазона преобразования входной сигнал надо привязывать к его средней точке шкалы преобразования, как на схеме, а пара 100-омных резисторов служит стандартной нагрузкой для радиочастотных сигналов.

==907

32 AD9269, который присутствует в табл. 13.4 - двойной АЦП с обычными КМОП выходами, но уже чуть более быстрые модели имеют параллельные дифференциальные LVDS выходы - 32 линии для 16-разрядного результата. <-

33 Можно было выбрать LMH6552 или LMH6553 фирмы TI. <-

35 Часть выходного дифференциального напряжения вернётся на вход в виде синфазного сигнала, увеличивая напряжение на резисторе \(R_g\) . <-

36 Если такая ситуация недопустима, то придётся снизить усиление раза в два или поискать ОУ чуть быстрее, например, ADA4937 с частотой по выводу «Vocm» 440 MHz . <-

37 Такую технику называют ещё «супер-Найквист режим». См., например, ##AN-939 фирмы Analog Devices. <-

38 Есть такой же преобразователь ADC08B200 с буфером на 1024 отсчёта, который очень удобен, если требуется быстрая оцифровка с последующим неторопливым считыванием результатов. <-