13.7 АЦП II: Последовательного приближения

==908

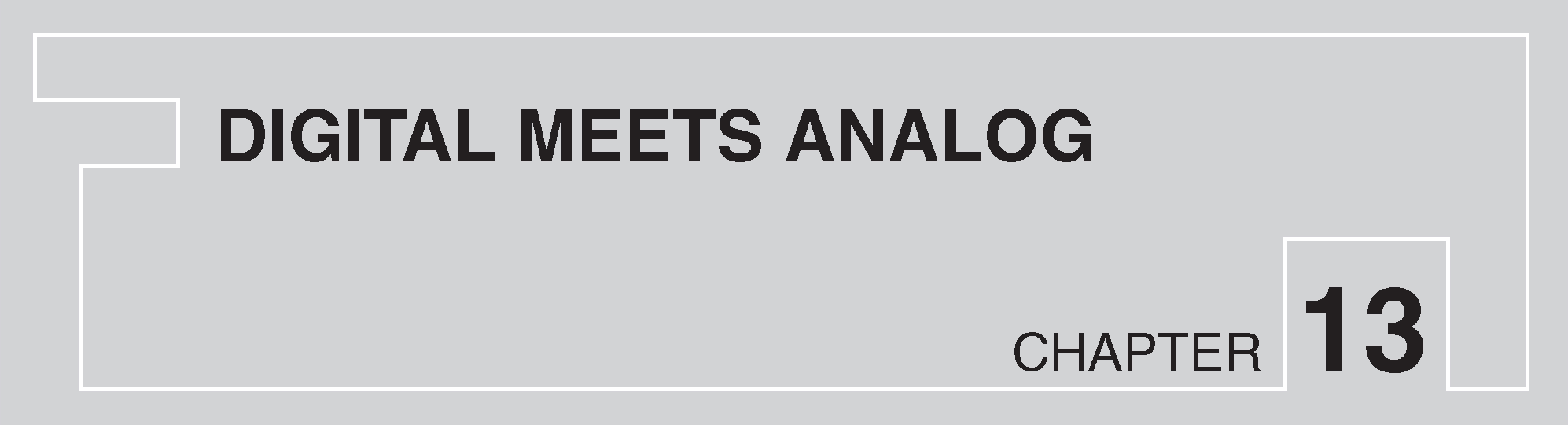

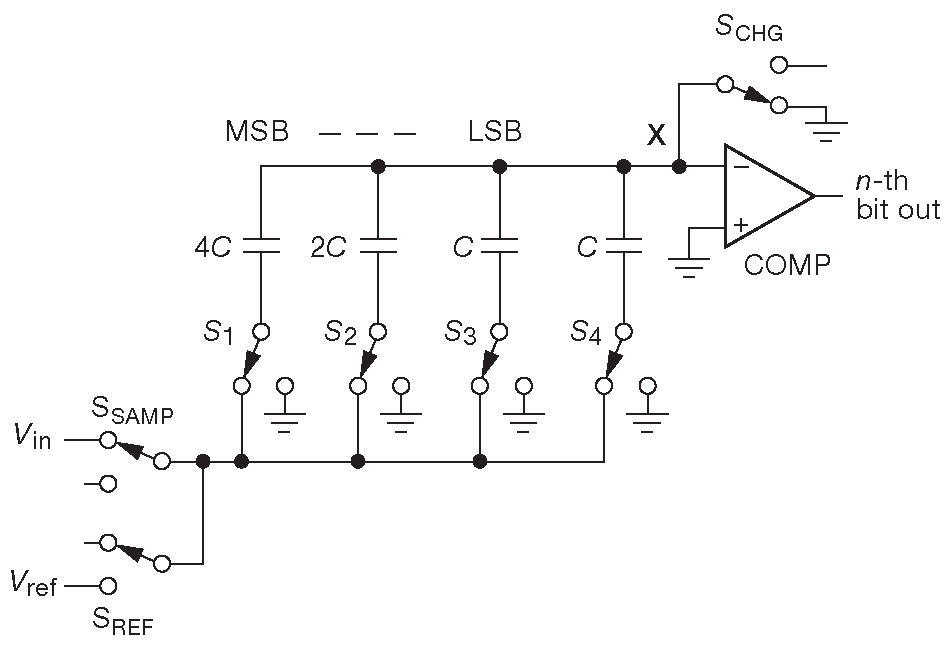

В классической технике последовательного приближения схема заводит текущий выходной код на ЦАП и сравнивает его выход со входным сигналом с помощью компаратора ( рис. 13.31 ). Процесс запускается с нулями во всех разрядах. Затем, начиная со старшего бита, очередной разряд временно переключается в единицу. Если выход ЦАПа при этом не дотягивает до входного сигнала, то данный разряд так и остаётся в единичном состоянии, в противном случае разряд сбрасывается, и цикл повторяется для следующего бита. Для n-разрядного АЦП требуется n тактов. В математике данная процедура носит имя двоичный поиск 39 . АЦП последовательного приближения имеют вход «BEGIN CONVERSION» и выход «CONVERSION DONE». Результат может выдаваться параллельно ( все разряды одновременно, каждый на своём выводе ) или последовательно ( n разрядов один за другим, начиная со старшего, через единственный вывод ) или в обоих форматах одновременно.

Рис. 13.31 АЦП последовательного приближения

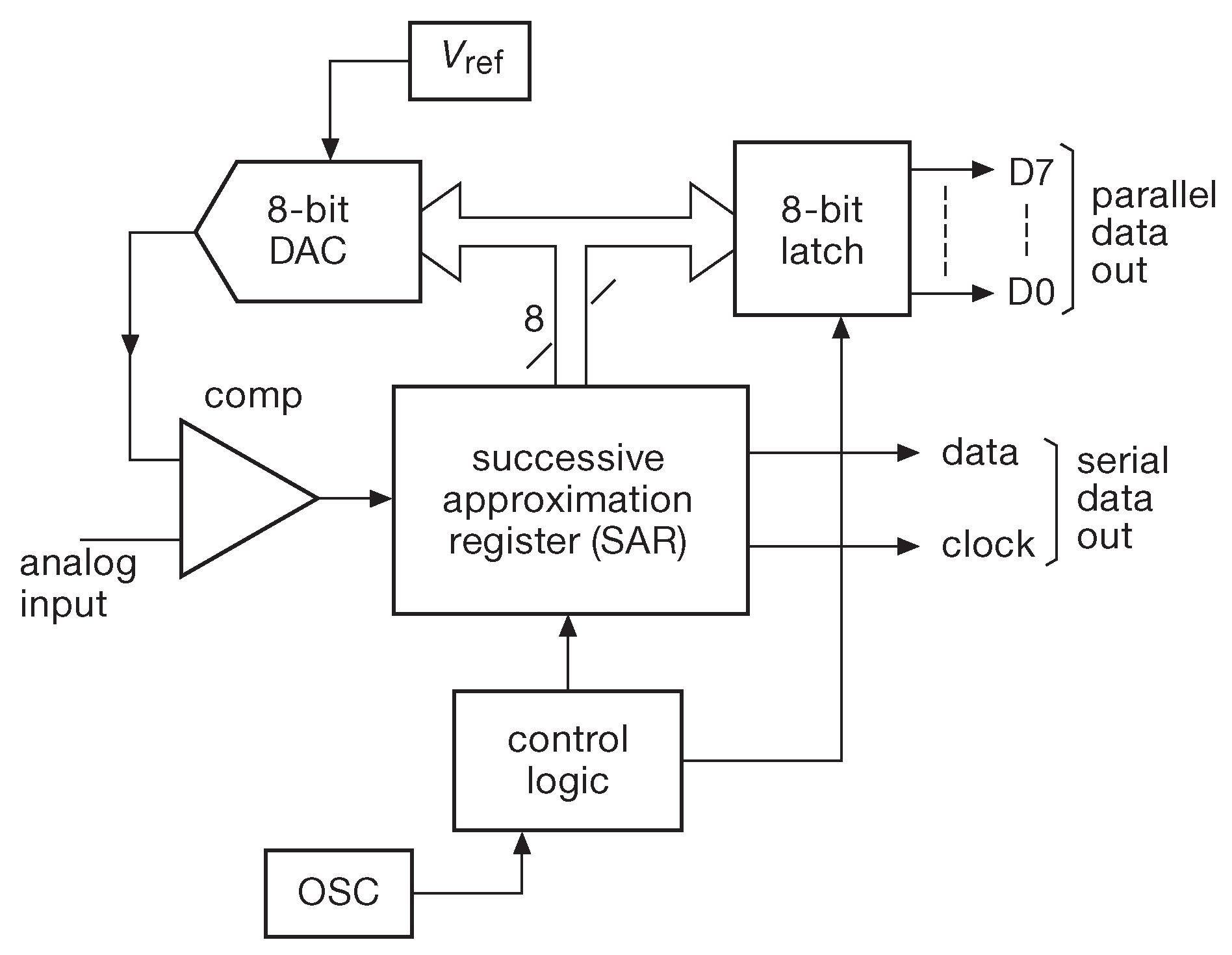

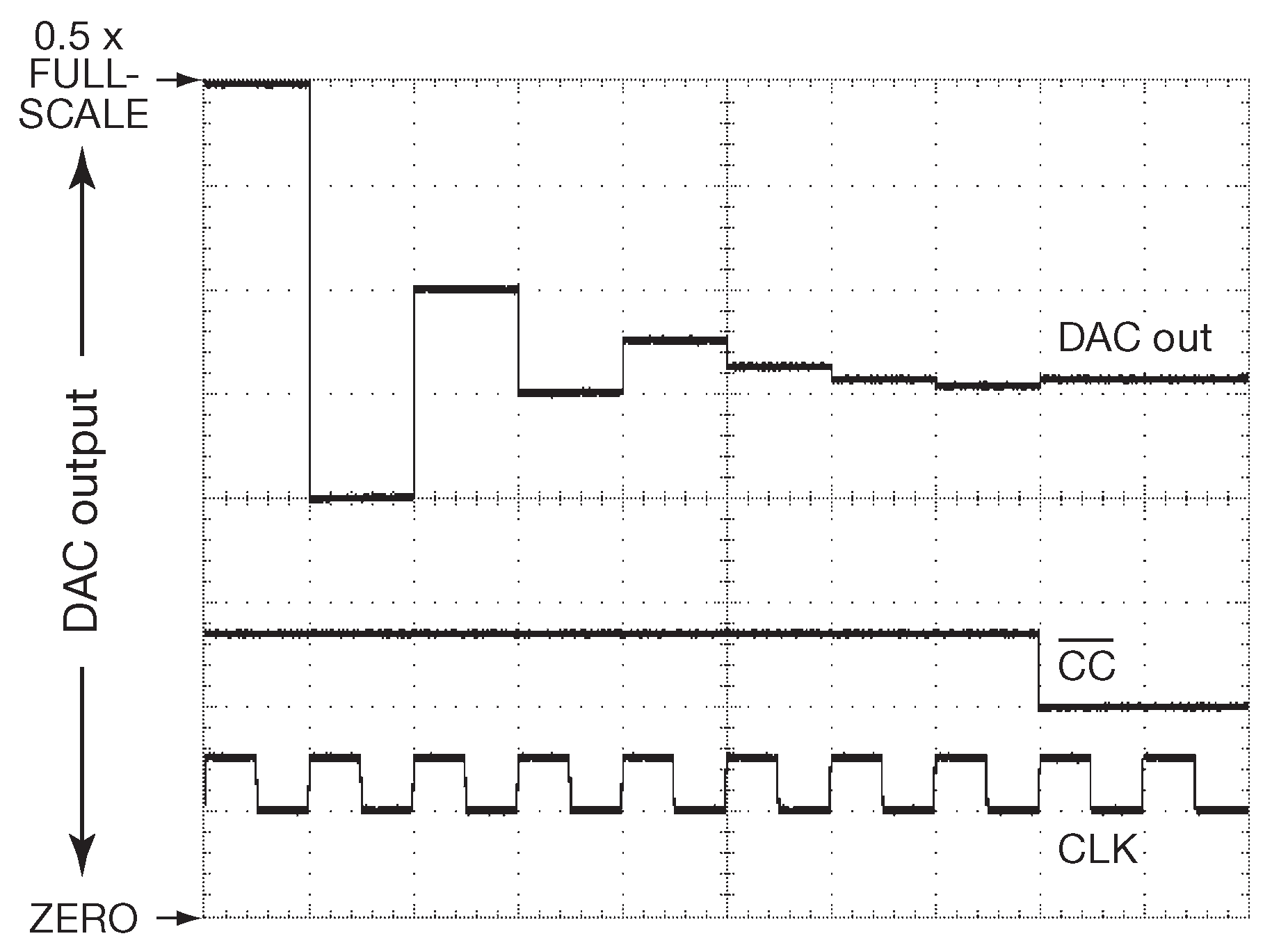

На университетских занятиях по электронике студенты собирают из ЦАПа, компаратора и логических микросхем законченный АЦП последовательного приближения. На рис. 13.32 показан выход ЦАПа, тактовые сигналы и признак окончания преобразования, а на рис. 13.33 - полное 8-разрядное «дерево» выбора, которое можно построить, наблюдая за выходом ЦАПа, когда на вход преобразователя подаётся линейно возрастающее напряжение, пробегающее весь входной диапазон АЦП.

Рис. 13.32 Выходной сигнал ЦАПа из состава 8-разрядного АЦП последовательного приближения, включающий момент завершения формирования кода. Это картина типичного двоичного поиска, начинающегося с первого предположения, равного половине полной шкалы. Виден тактовый сигнала системы и признак завершения счёта Рис. 13.33 Экран осциллографа, накопившего полное «дерево» преобразования 8-разрядного АЦП последовательного приближения

АЦП последовательного приближения занимают промежуточное положение по сочетанию скорости и точности ( если сравнивать с быстрыми параллельными и точными, но медленными, «сигма-дельта» и интегрирующими вариантами ). См. табл. 13.5 и 13.6 . SAR модели требуют n периодов тактовой частоты для получения n-разрядной точности. Типичное время преобразования 1 μs , точность - от 8 до 18 разрядов. Преобразователи делают быструю выборку входного напряжения и ошибка от его изменения [* апертурная погрешность ] может появиться только в этот момент, но импульсы на входе совершенно недопустимы. АЦП этого типа изначально достаточно точны, но требуют хорошо согласованных резисторных сборок и часто болеют странными нелинейностями и «пропущенными кодами». Одним из способов недопущения появления таких кодов является использование цепочки из 2n резисторов и ключей для создания промежуточных напряжений на манер ЦАПов на цепочке резисторов ( §13.2.1 ). Так работают 8-разрядные АЦП серии ADC0800 фирмы NSC/TI.

==909

В современных АЦП последовательного приближения обычный резистивный ЦАП ( цепочка R-2R резисторов ) заменяется на ЦАП с перераспределением заряда ( рис. 13.34 ) 40 . Такая схема требует набора конденсаторов с двоично взвешенными емкостями, которые научились делать в кремнии и точно подстраивать. ( Таким образом, в 18-разрядном АЦП AD7641 имеется примечательный сам по себе набор 41 из 18 конденсаторов номиналами \( C_0\) , 2\( C_0\) , 4\( C_0\)...131072\( C_0\) . Конденсаторы на самом деле очень небольшие: \( C_0\) имеет номинал порядка фемтофарад ( fF ) или 0.001 pF ).

Рис. 13.34 Схема «перераспределения заряда» заменяет обычный резистивный R-2R делитель во многих АЦП последовательного приближения. Конденсатор между ёмкостью LSB и ОУ используется в качестве второго плеча емкостного делителя

Чтобы понять принцип работы, рассмотрим функционирование 3-разрядного преобразователя с рис. 13.34 .

- На рисунке ключи находятся в положении выборка, в котором напряжение на конденсаторах повторяет ( отслеживает ) входной сигнал.

- Ключ \( S_{SAMP}\) размыкается, а конденсаторы продолжают хранить полученный заряд, т.е. копию входного напряжения.

- Размыкается ключ \( S_{CHG}\) , и потенциал на входе компаратора теперь может меняться в соответствии с промежуточными цифровыми кодами, приложенными к \( S1-S3\) . Если, например, все ключи замкнуты на землю, то на входе «X» будет напряжение \(-V_{in}\) .

- Теперь, чтобы измерить значение хранимого напряжения \( V_{in}\) , зарядные ключи начинают переключаться один за другим. Сначала старший \( S1\) подключается к \(+V_{REF}\) ( потенциал полной шкалы АЦП ), а \( S2\) , \( S3\) и \( S4\) подключаются к земле. Такое действие добавляет на вход «X» смещение \( V_{REF}\)/2 к уже имеющемуся \(-Vin\) ( это емкостной/зарядовый делитель, который часто называют «делителем с перераспределением заряда» ).

- На выходе компаратора в этот момент появляется старший разряд - HIGH, если \( V_{in}>V_{REF}\)/2 , LOW в противном случае.

- Как в классической процедуре последовательного приближения ключ или возвращается к потенциалу земли или остаётся замкнутым на \( V_{REF}\) , соответственно. После чего начинает проверяться следующий ключ. Для выяснения полного n-разрядного кода процесс повторяется n раз ( здесь n=3 ).

13.7.1 Простой АЦП последовательного приближения

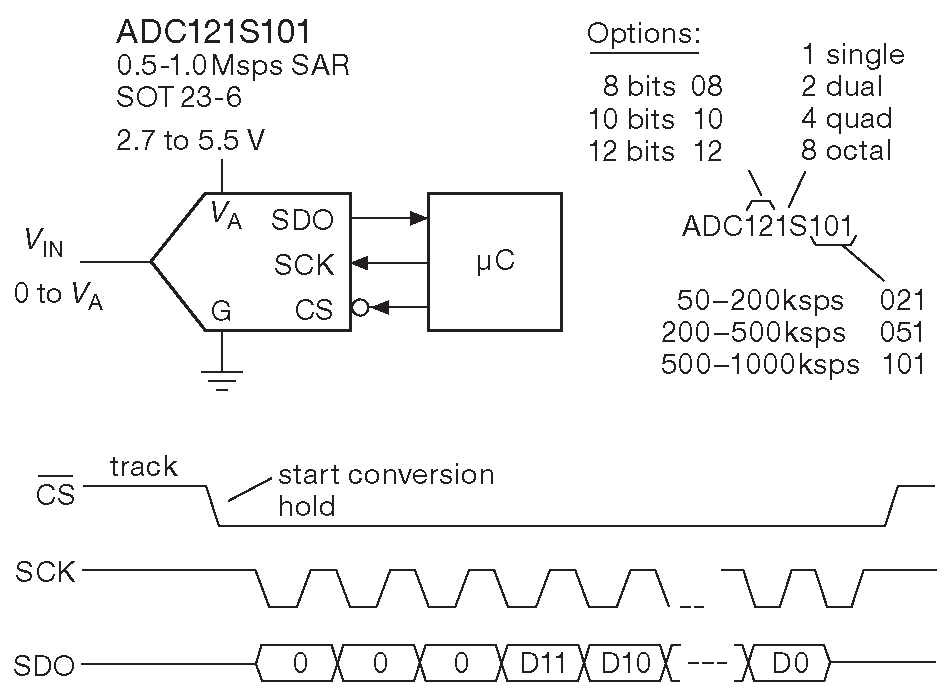

Использовать АЦП такого типа очень легко, как можно понять из рис. 13.35 . Последовательный интерфейс SPI сам по себе не сложен: перевод «/CS» в активное низкое состояние запускает преобразование, биты один за другим выводятся наружу по фронту сигнала «SCK», запуская одновременно преобразование для следующего бита. Такая схема позволяет держать линии последовательной связи в пассивном состоянии, минимизируя наведённый цифровой шум до момента активации «/CS». Указанные на схеме относительно низкочастотные преобразователи имеют внутреннюю схему выборки-хранения и три градации точности ( 8, 10 и 12 разрядов ) и четыре вида упаковки ( по одному, по паре, по четыре или по восьми АЦП в корпусе ), итого, 36 вариантов. Одиночный преобразователь 1 MHz , 12 разрядов, в корпусе SOT23-6 в единичных количествах обойдётся в $4.50 (8-разрядный - $2 ).

Рис. 13.35 Удобная линейка АЦП последовательного приближения с портом SPI ADC08/10/12S фирмы National Semiconductor/TI

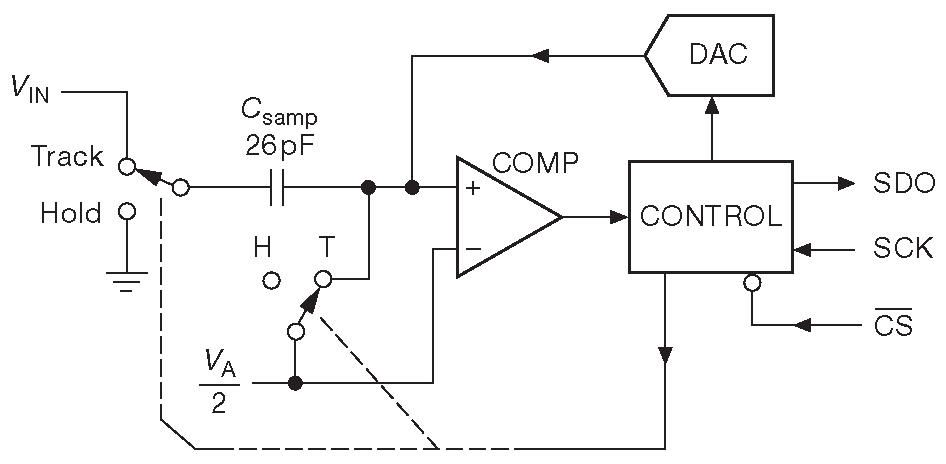

Вход АЦП часто совсем не похож на вход ОУ. Его импеданс может быть мал, а входная ёмкость наоборот довольно велика. На рис. 13.36 приведена эквивалентная схема входных цепей преобразователя, где отчётливо виден конденсатор выборки-хранения величиной 26 pF , который будет заряжаться от измеряемой схемы. Если частота относительно низкая, такая нагрузка не особо обременительна, но её следует иметь в виду, разбирая, например, схему 13.37 . Её разрешение гораздо выше ( 18 разрядов ), а скорость больше.

Рис. 13.36 Блок-схема АЦП с рис. 13.35 . Входной сигнал в момент захвата заряжает конденсатор \( C_{samp}\) схемы выборки-хранения

13.7.2 Варианты схемы последовательного приближения

==910

Схема, известная как «следящее АЦП» использует реверсивный счётчик, чтобы получать последовательные промежуточные коды, что замедляет реакцию на большие перепады сигнала, но зато отслеживает плавные изменения быстрее, чем схема последовательного приближения. Для большой разницы скорость нарастания пропорциональна тактовой частоте. Очередь реверсивных битов последовательна по своей природе и является упрощённой формой дельта-модуляции.

Ещё одним вариантом является дельта-модуляция с изменяемой крутизной ( CVSD ) - простой метод, который иногда используется для последовательного 1-битного кодирования речи, например, в беспроводных телефонах. В CVSD нули и единицы кодируют направление шага ( вверх или вниз ) формы выходного сигнала, но степень изменения текущего сигнала подстраивается в соответствии с его ближайшей историей. Например, величина шага, соответствующего 1 увеличивается, если несколько предшествующих битов также находились в состоянии 1 ( длина необходимой последовательности зависит от установленных правил). Декодер, зная правило кодировки, может восстановить исходный сигнал. Раньше этот способ кодировки выполняли в кремнии, но сейчас он реализуется почти исключительно в виде программ для микроконтроллеров и DSP.

13.7.3 Пример включения АЦП последовательного приближения

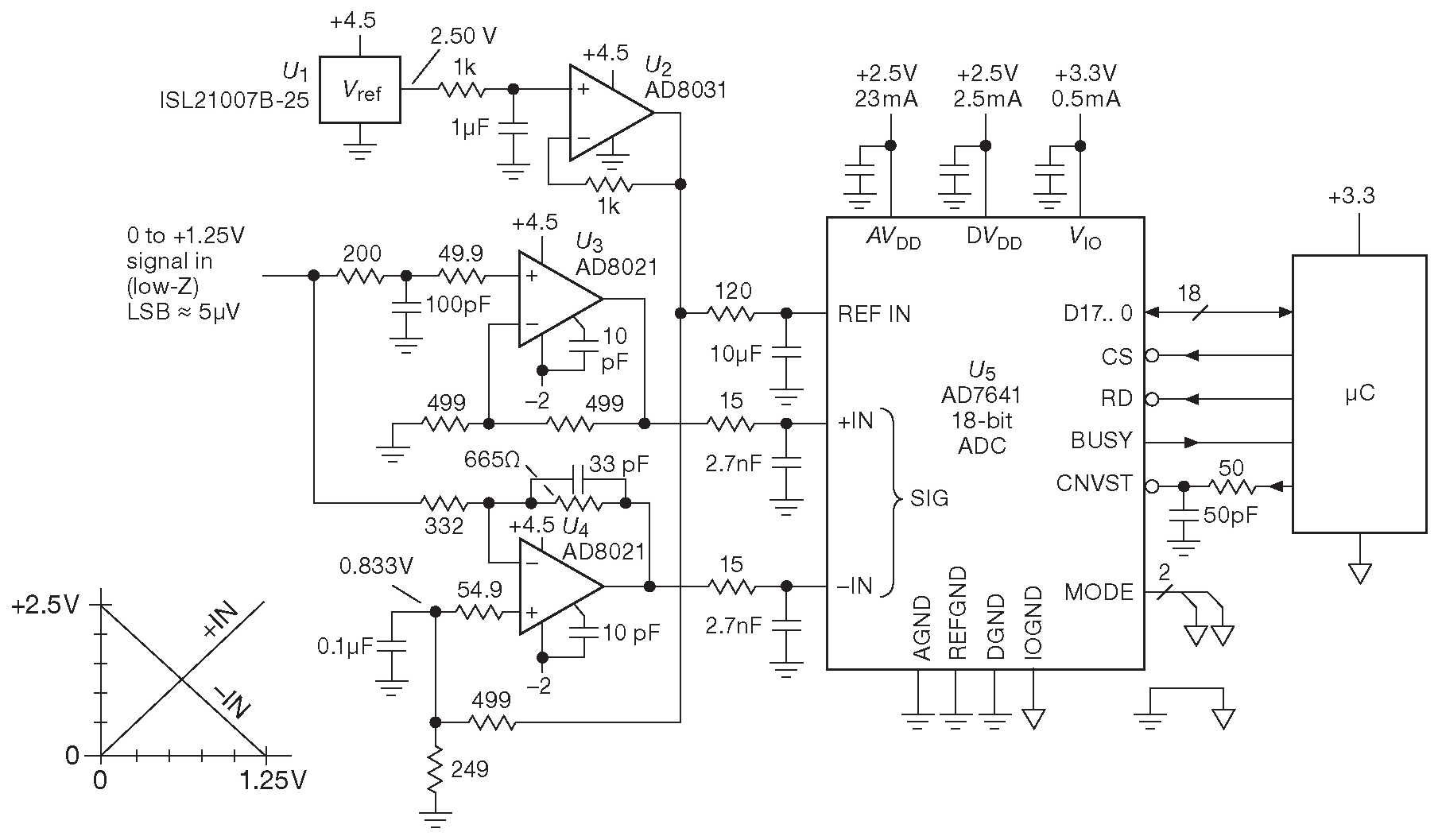

Прежде чем переходить к очень важным комплексным методам преобразований ( V-F, многостадийного интегрирования, «сигма-дельта» ), познакомимся с основными задачами для АЦП последовательного приближения: малошумящий 18-разрядный АЦП со стабильными параметрами и скоростью преобразования 2 MHz .

Table 13.5 Selected Successive-approximation A-to-D Convertersa Notes: (a) listed by accuracy and speed; all feature "no missing codes"; all permit external \( V_{REF}\) Input. (b) the ADS7946 Is the same, without diff’l Input. (c) power scales linearly with sample rate. (d) MAX1301 has half the number of inputs, in 20-pin TSSOP. (e) or to 2\( V_{REF}\) , see datasheet. ( f) with ext ref. ( g ) or 4.5-5.5 V. (h) supply current during shutdown, power-down, or quiescent. (k ) S=serial, P=parallel. ( p) pseudo-differential. Comments: A: sequencer; AD7928=1 Msps. B: 10-bits='67, 8-bits='68, $1.80; 280 ksps at Vs>1.6 V; 8 nA typ off, power-off after each conversion, 0.4?W at 100 per second, 44?W at 20 ksps and Vs=1.2 V. C: ADC121S051=500 ksps, ADC121S021=200 ksps. D: digital I/O supply 2.7 V-5.25 V. E: digital I/O supply 1.5 V-3.6 V. F: digital I/O supply 1.65V to Vs. G: digital I/O supply 2.3 V-5.25 V. H: digital I/O supply 1.8 V to Vs. J: digital supply 2.4 V-2.6 V; digital I/O supply 1.8 V-2.7 V. K: digital I/O supply 1.7 V-5.3 V. L: digital I/O supply 2.4 V-5.5 V. M: PGA, 7 gain choices; 8 singled-ended or 4 diff'l inputs; Vin up to ±3\( V_{REF}\) or 6\( V_{REF}\) , or up to ±16V with Vs=5V. N: charge-redistribution ( capacitive ) SAR; power scales linearly with sample rate. O: 8 independent ADCs, simultaneous sampling; 6-ch=MAX11045, 4-ch=MAX11044. P: true "Beyond-the-Rails" without input dividers, ±5V with single Vs=+5; int \( V_{REF}\) 17 ppm/°C max. Q: FIFO; averaging; 1, 2, 4, .. 32 channel sequencer. R: int ref 10 ppm/°C,typ; digital supply 2.4-2.6 V. S: 32x oversampling, on-chip FIR filter. T: 8x oversampling, on-chip FIR filter. U: 100 dB min SNR, 125 dB typ THD. V: digital I/O supply 1.65-3.6 V; ADS886x are 16-bit diff’l and single-ended versions; family includes slower versions, to 100 ksps.

==911

На схеме 13.37 показан типовой АЦП фирмы Analog Devices 18-разрядный 2 Msps AD7641 ( фирменная линейка PulSAR ). Он использует три положительных источника питания 42 , которые, к счастью, можно включать в любой последовательности.

Рис. 13.37 18-разрядный AD7641 и входной буфер, способные работать на скорости 2 Msps

Входной диапазон AD7641 составляет ±\( V_{REF}\) - это обычная величина для низковольнтых АЦП. Преобразование с минимальным шумом требует увеличения величины опорного напряжения и максимального соответствия входного сигнала полному диапазону измерения. Питание аналоговой части «AVdd» составляет +2.5 V , поэтому дифференциальный аналоговый сигнал ограничен величиной 0...+2.5 V . Если используется максимально допустимое опорное напряжение +2.5 V , то полная шкала будет ±2.5 V для дифференциального сигнала: когда «+IN» проходит путь от 0 до +2.5 V , «-IN» будет правильнее измениться от +2.5 V до 0 , а иначе останется только 17 разрядов. Для 18 разрядов вес младшего составит 19 μV . Столь малые напряжения требуют внимательного отношения, особенно если частота опроса составляет 2 Msps , а полоса по уровню «-3dB» равна 50 MHz . Без должного обращения в ней немедленно появится масса шума 43 от близлежащих цифровых цепей.

И входной сигнал, и опорное напряжение отлично воспринимают наводки от схемы перераспределения заряда, поэтому в схеме стоят стабилизирующие конденсаторы ( справочные данные рекомендуют 2.7 pF ), чтобы подавить шумы переключения 44 . Операционные усилители не любят емкостную нагрузку, которая вместе с индуктивностью цепи обратной связи ведёт к самовозбуждению и звону ( см. §4.6.2 и тему емкостной нагрузки в Части X4 ), отсюда и последовательный резистор 15 kΩ . Получившийся RC фильтр имеет частоту среза 4 MHz и давит внеполосный шум. В такой полосе требования по плотности шумов снижаются и составляют всего 9.6 nV/\(\sqrt{Hz}\) . Отметим заметное сопротивление ( 120 Ω ) последовательного резистора в цепи \( V_{REF}\) , призванного ограничивать бросок тока при включении питания, тем более, что здесь широкая полоса не нужна.

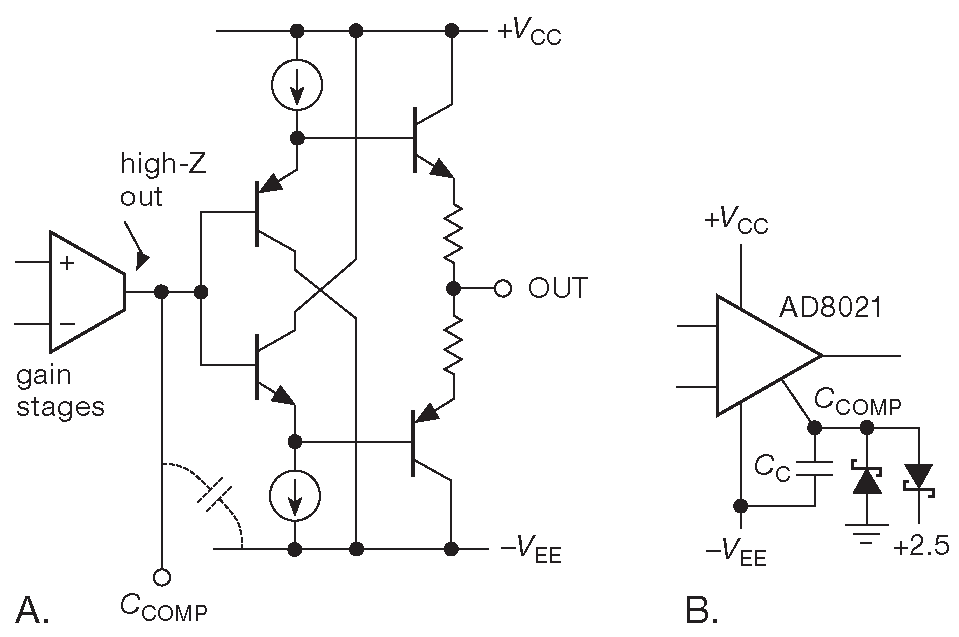

На схеме изображена обвязка, оптимизированная для работы в широком диапазоне частот с однополярным сигналом от 0 до +1.25 V . AD8021 - широкополосный малошумящий ОУ, рекомендованный в справочных данных на АЦП. Это, может, и не самый лучший компонент для использования 45 , но продолжим следовать рекомендациям производителя. Пара ОУ создаёт точный дифференциальный сигнал из однополярного. Верхний каскад имеет усиление +2 , а нижний -2 . Отметим небольшие номиналы резисторов, которые позволяют иметь широкую полосу и низкий тепловой шум. Параллельная, а не последовательная схема получения дифференциального сигнала используется, чтобы выровнять задержки в обеих ветвях. Ещё один приём: инвертирующий усилитель опирается на уровень \( V_{REF}\)/3 , чтобы получить требуемый диапазон от +2.5 V до 0 . Обе ветви имеют разное усиление по шуму, но AD8021 позволяет добавить компенсирующий конденсатор 10 pF на специальный вывод, чтобы подсократить отклик и добиться примерно равных рабочих частот. Из-за высокого входного тока \(I_b\) =7.5 μA приходится выравнивать сопротивление цепей на инвертирующем и неинвертирующем входах ОУ. В данном случае это очень эффективный приём, так как типовой ток смещения AD8021 в 75 раз меньше входного и составляет всего 0.1 μA .

==912

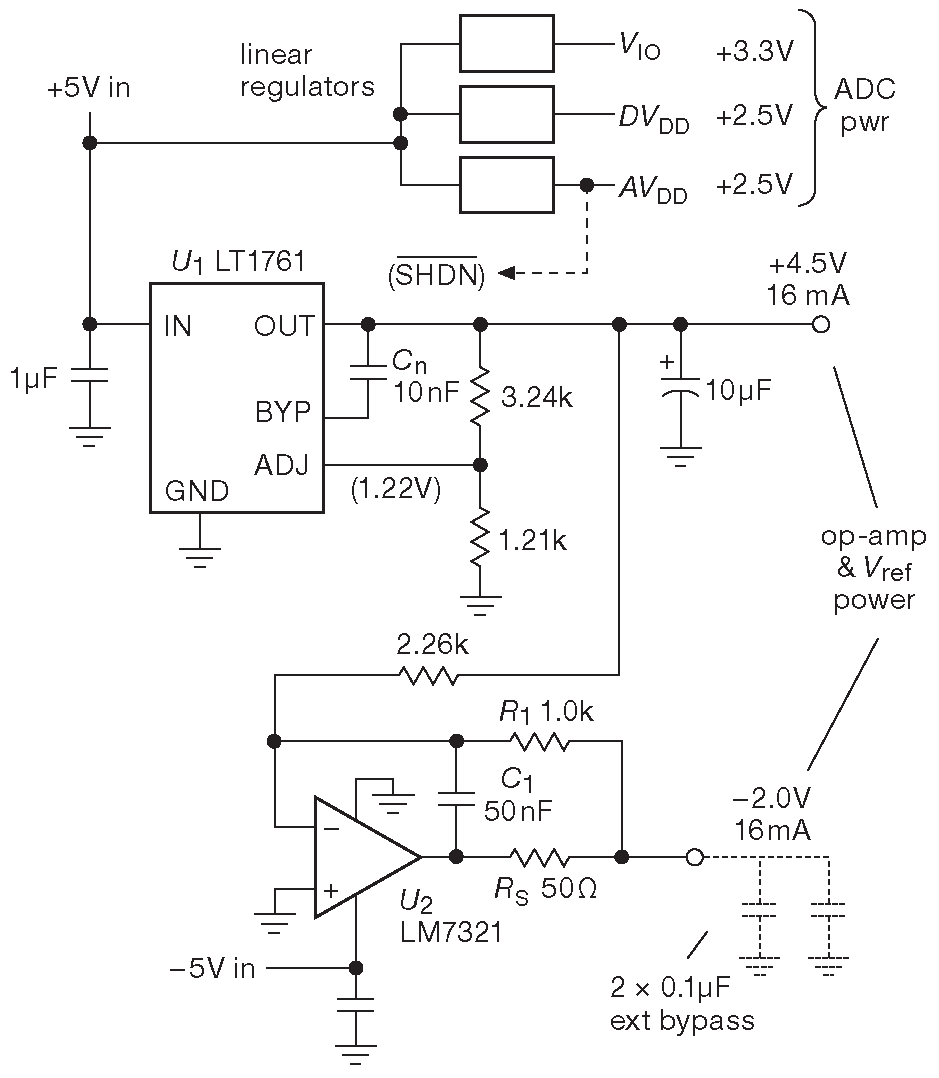

Опорный источник ISL21007/9BFB825 фирмы Intersil ( табл. 9.8 на стр. 678 ) использует технологию плавающего затвора ПТ ( т.е. заряд внутреннего конденсатора, см. §9.10.4 ), что позволяет получить необычно низкий дрейф по времени ( < 10 ppm/\(\sqrt{kHr}\) ) . У него отличная начальная точность ( 0.02% ) и низкий температурный коэффициент ( 3 ppm/°C ). Источник снабжён противошумовым фильтром и буферным ОУ, который изолирует 3.3 mA тока нагрузки, чтобы снизить разогрев опорного источника. Усилители питаются от +4.5 V и -2.0 V , получаемых из ±5V для АЦП ( рис. 13.38 ), поэтому усилители включаются одновременно с преобразователем, что минимизирует ток через ограничительные диоды на входе АЦП при подаче питания. Ещё один способ ограничить сигнал на входе АЦП - использовать специальный ОУ с ограничением AD8036, но его ошибка по постоянному току выше, чем у AD8021. К счастью, есть очень простое решение: поставить на вывод «Ccomp» микросхемы AD8021 два ограничительных диода Шоттки SD101 с малой ёмкостью ( 2 pF ), один на землю, другой - на +2.5 V , как показано на рис. 13.39 46 .

Рис. 13.38 Линейный стабилизатор, обеспечивающий питание АЦП и буферных ОУ. LM7321 - мощный усилитель, вполне подходящий для тока нагрузки 50 mA . Расщеплённая обратная связь ( со срезом ∼3 kHz ) позволяет обеспечить устойчивость на ёмкостной нагрузке ( конденсаторы, шунтирующие выводы питания ОУ ) и сохранить точность на постоянном токе

Рис. 13.39 Выводы компенсации некоторых ОУ можно использовать для ограничения выходного сигнала. (A) Выходной каскад AD8021 выполнен в виде симметричных эмиттерных повторителей «с нулевым смещением», а вывод «Ccomp» подключается к узлу с высоким импедансом на выходе предыдущего усилительного каскада. (B) Подключение диодов Шоттки в этой точке ограничивает сигнал на выходе ОУ уровнями опорных напряжений, в данном случае - входным диапазоном АЦП

На схеме АЦП включёно в параллельном 18-разрядном режиме ( выводы «MODE» заземлены 47 ). Сигнал «/CNVST» запускает цикл преобразования и включён с рекомендуемым Analog Devices RC фильтром ( 2.5 ns ), чтобы чуть затянуть время спада и предотвратить выброс по низкому уровню. «/CNVST» не должен возвращаться в высокое состояние до завершения цикла преобразования, т.е. около 400 ns в скоростном режиме.

==912

39 Исторически данный метод восходит к 1556 году, когда математик по имени Тарталья предложил использовать набор весов в 1 меру, 2 меры, 4 меры и так до 32 , чтобы измерять вес объекта за наименьшее число смены гирь на весах. <-

40 Существует также гибридная схема, в которой ЦАП с перераспределением заряда используется для уточнения потенциала, полученного с грубого ЦАПа на резистивном делителе. <-

41 На самом деле два набора, потому что входы дифференциальные. <-

42 Отдельные выводы +2.5 V для аналоговой и цифровой секции, плюс ещё один для выходного цифрового порта ( от +2.3 до +3.6 V ). Низковольтовые микросхемы часто используют несколько напряжений питания, требующих раздельных стабилизаторов. <-

43 В полосе 50 MHz уровню 19 μV соответствует плотность шума \(e_n\) всего 2.7 nV/\(\sqrt{Hz}\) . <-

44 Учтите, что при полной скорости 2 Msps компаратор в АЦП последовательного приближения принимает решение с точностью 19 μV каждые ∼20 ns . Суматошная работа. <-

45 Такой выбор несколько необычен, потому что усилитель не считается «прецизионным»: максимальное напряжение смещения ( до 1 mV ) смотрится плохо, а входной ток ( 7.5 μA ) достаточно велик, причём, всё это издержки высокой скорости работы ( 100 MHz и 20 ns времени установления ), которая здесь не нужна. <-

46 В справочных данных на AD8021 ничего о таком приёме не говорится, но там есть упрощённая схема усилителя, из которой видно, что сигнал на «Ccomp» приходит от высокоомного выхода каскада усиления, а дальше идёт на выходной комплементарный эмиттерный повторитель с нулевым смещением ( рис. 13.39 ), т.е. на этом выводе присутствует слаботочная высокоомная копия выходного сигнала, пригодная для ограничения. <-

47 Три остальных режима: параллельный 16-разрядный ( два цикла чтения ), параллельный 8-разрядный ( три цикла чтения ) и последовательный SPI ( 18 тактов на цикл ). <-