13.8 АЦП III: Интегрирующие

==912

13.8.1 Преобразователи напряжение-частота

Обзор принципов аналогово-цифровых преобразователей продолжат конверторы напряжение-частота ( V-to-F или V/F ). Здесь входной аналоговый сигнал преобразуется в непрерывный поток импульсов, чья частота пропорциональна уровню напряжения на входе. Импульсы можно получить, заряжая конденсатор током, пропорциональным входному напряжению, и разряжая затем до нулевого уровня. Для увеличения точности используется обратная связь. В одном варианте выход V/F-схемы сравнивается с уровнем на входе и поддерживается та частота, которая позволяет удерживать выход компаратора в нужном состоянии. В другой, более популярной схеме, используется метод «балансировки заряда», который разбирается позднее ( схема перекачки заряда специальным конденсатором ).

==913

Выходная частота преобразователей лежит в диапазоне от 10 kHz до 1 MHz для полного диапазона входных напряжений. Коммерческие преобразователи V/F имеют разрешение 13 разрядов ( точность 0.01% ) и являются примерами качественных генераторов, управляемых напряжением ( §7.1.4.D ). Например, отличный AD650 фирмы Analog Devices имеет в рабочем диапазоне 0...10 kHz типовую нелинейность 0.002% . Он недорог и удобен для передачи по кабелю, когда требуется частота, а не цифровой код. Если скорость не важна, можно получать усреднённое цифровое значение, считая импульсы в течение определённого времени. Такая техника используется в простых цифровых щитовых приборах на 3 десятичных разряда.

VCO , подобные AD650, являются асинхронными преобразователями напряжение-частота, т.е. внутри у них есть постоянно тикающий генератор, а вывода для внешней частоты нет. Но задачу можно решать иначе. Можно пропускать на выход часть входного потока импульсов, пропорциональную в среднем входному аналоговому сигналу. Для таких синхронных преобразователей V/F выходные импульсы появляются синхронно с внешней тактовой частотой. В каждом периоде тактовой частоты импульс может пропускаться на выход или блокироваться присутствовать или отсутствовать в зависимости от того, что требуется, чтобы средняя выходная частота была пропорциональна \( V_{in}\) . В общем случае расстояние между соседними импульсами постоянно меняется ( но всегда пропорционально целому числу периодов тактовой частоты ), т.е. на выходе нет какого-то регулярного сигнала. Выходная импульсная последовательность имеет «джиттер» . Где-то, где усреднение сигнала внутренне присущее схеме свойство, это нормально, например, так себя ведёт резистивный нагреватель с аналоговым датчиком температуры в контуре управления.

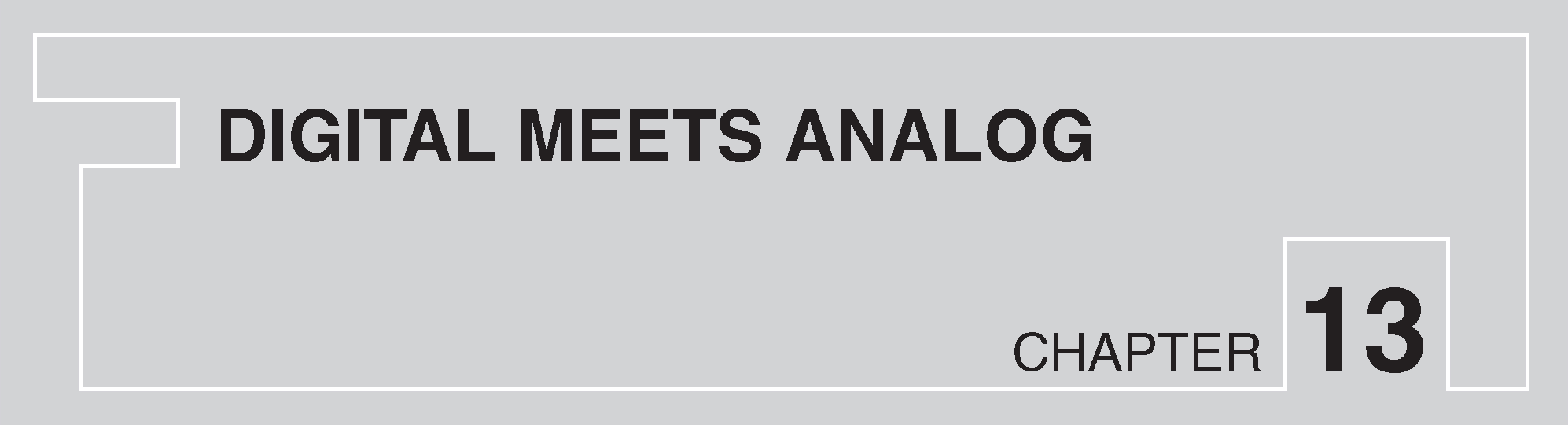

На рис. 13.40 показан усреднённый на промежутке длиной несколько секунд выходной сигнал, снятый на макете синхронного преобразователя V/F AD7741 с тактовой частотой 5 MHz . Линейность, как легко заметить, очень неплохая.

Рис. 13.40 Результаты измерения нелинейности выходной частоты синхронного преобразователя напряжение-частота AD7741 как функции входного напряжения. В паспорте стоит цифра ±0.015%

Синхронные преобразователи напряжение-частота являются простым примером «1-разрядного» АЦП. Есть и более удобные способы создания битовых последовательностей, пропорциональных среднему значению аналогового сигнала. А именно, сигма-дельта преобразователи делают подобную работу гораздо лучше. Но понять, как они этого добиваются, несколько сложнее. Они рассматриваются в §13.9 , где будет предпринята героическая попытка развеять туман непонимания и заблуждений ( и, как обычно, с неизвестным результатом ).

==914

13.8.2 Однократное интегрирование

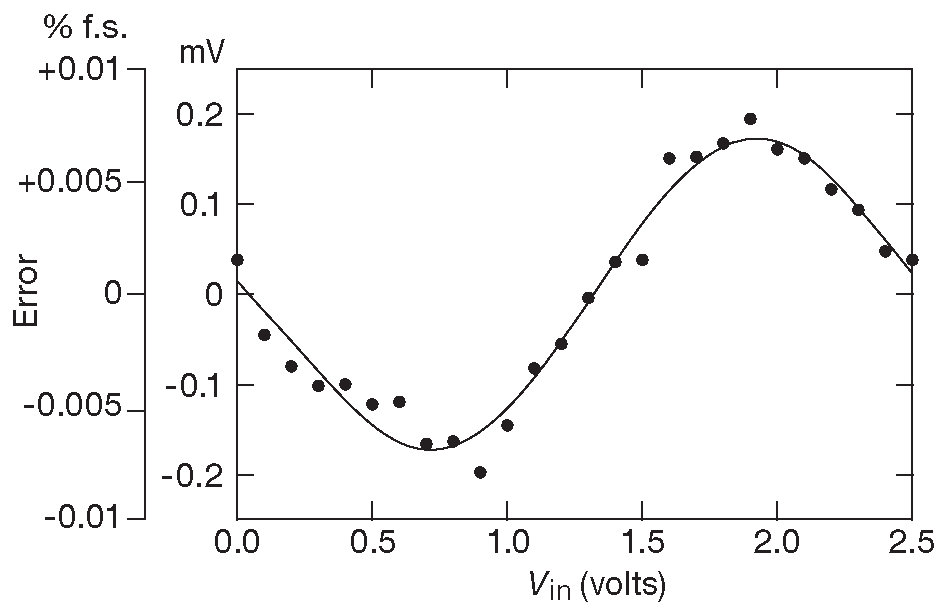

В этом методе однократного интегрирования внутренний генератор линейно возрастающего напряжения ( источник тока + конденсатор ) начинает цикл преобразования и одновременно запускается счётчик, который начинает накапливать импульсы стабильной тактовой частоты. Когда возрастающее напряжение сравняется со входным сигналом, компаратор остановит счёт. Полученная цифра и есть выходной код, пропорциональный входному напряжению. Блок-схема преобразователя показана на рис. 13.41 .

Рис. 13.41 АЦП однократного интегрирования

В конце цикла преобразования схема разряжает конденсатор и сбрасывает счётчик, после чего можно начинать новый цикл. Однократная интеграция проста, но не используется, когда нужна высокая точность, потому что накладывает жёсткие требования на стабильность и точность конденсатора и компаратора. Данное ограничение ( и некоторые другие ) отсутствует в методе «двойного интегрирования», который в настоящий момент используется везде, где нужны точные показания.

Однократные интеграторы живы и по-прежнему используются там, где абсолютная точность не требуется, но нужно равномерное разбиение диапазона по уровням. Примером может служить анализ амплитуды импульсов: пиковый детектор сохраняет максимальный уровень импульса, который затем преобразуется в адрес. Точное разделение по амплитуде является основным требованием для такой задачи, а метод последовательного приближения здесь совершенно не годится. Однократная интеграция используется также в преобразователях время-амплитуда .

13.8.3 Интегрирующие преобразователи

Есть несколько методов, использующих конденсатор для хранения соотношения между входным сигналом и опорным напряжением. Всё это - методы, усредняющие ( интегрирующие ) входной сигнал на фиксированном промежутке времени преобразования, что имеет два полезных свойства.

- Использование одного конденсатора для сигнала и опорного напряжения позволяет не обращать внимания ( до некоторой степени ) на точность и стабильность ёмкости. Снижаются и требования к компаратору. Результат: при сравнимом качестве деталей точность выше, или можно получить такую же точность за меньшие деньги.

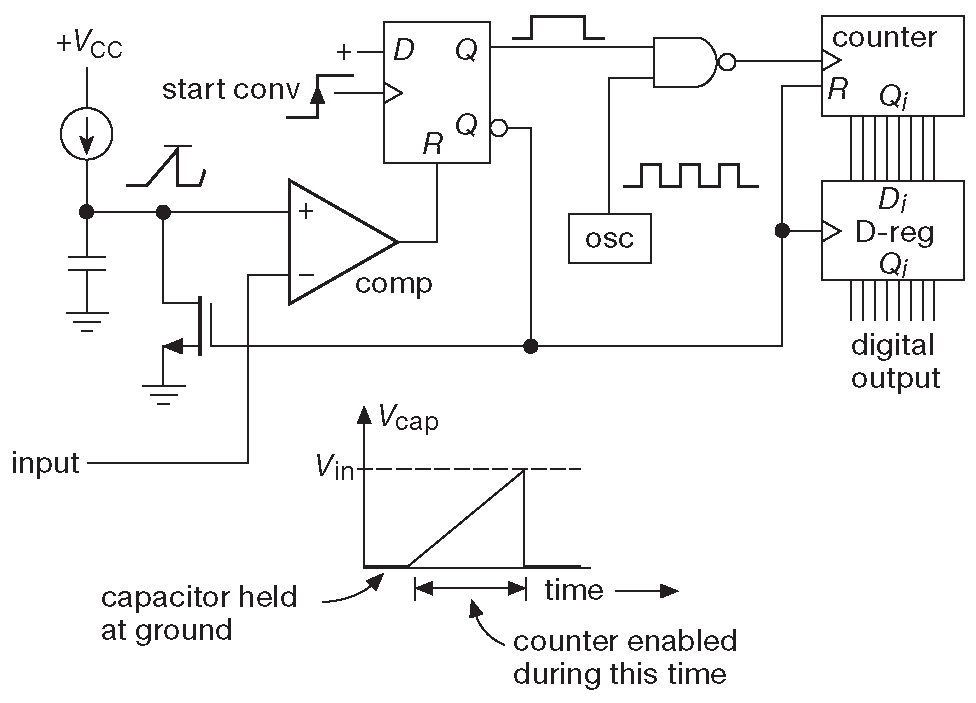

- Выход пропорционален входному напряжению, усреднённому по фиксированному промежутку времени интегрирования. Если проводить интегрирование на промежутке, кратном периоду сетевой частоты, то преобразователь станет нечувствителен к сетевой наводке и её гармоникам во входном сигнале ( рис. 13.42 ).

Рис. 13.42 Подавление сетевой наводки в зависимости от частоты преобразования в интегрирующих АЦП

Избавиться от сетевой интерференции можно, только точно соблюдая пропорциональность времени интегрирования сетевой частоте, т.к. ошибка от даже доли процента сетевого периода приведёт к неполной компенсации наводок. Один из выходов - использование кварцевого генератора. Красивым вариантом будет фазовая автоподстройка ( §13.13 ) для синхронизации рабочей частоты АЦП с сетевой частотой, снимающая все проблемы с подавлением наводок.

Недостатком интегрирующей техники является низкая по сравнению с последовательным приближением скорость преобразования. Достоинством - высокая точность, особенно в технике двойного или многостадийного интегрирования и сигма-дельта преобразования ( §13.9 ).

13.8.4 Двойное интегрирование

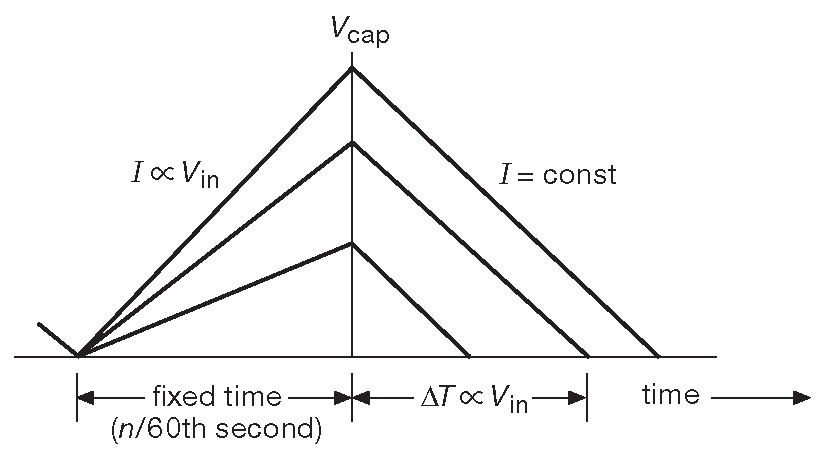

Двойное интегрирование - красивая и активно используемая техника, которая позволяет избавиться от большей части проблем с конденсатором и компаратором. Основная идея представлена на рис. 13.43 . Сначала ток, точно пропорциональный входному напряжению, заряжает в течение определённого времени конденсатор; затем конденсатор разряжается до нуля образцовым постоянным током. Время разряда пропорционально уровню входного напряжения и используется как сигнал разрешения счёта тактовых импульсов определённой частоты. Содержимое счётчика пропорционально входному напряжению.

Рис. 13.43 Цикл преобразования в методе двойного интегрирования

==915

Двойное интегрирование достигает очень высокой точности, не предъявляя жёстких требований к стабильности компонентов. В частности не обязательно иметь точную величину ёмкости конденсатора, потому что цикл заряда и цикл разряда идут со скоростью, пропорциональной 1/\( C \) [* и в уравнении взаимно компенсируются, т.е. сокращаются ] . Точно так же дрейф и смещение компаратора взаимно уничтожаются, т.к. конец цикла преобразования находится в той же точке и в тех же условиях, что и начало. В особо точных АЦП цикл измерения перемежается с циклом автоподстройки нуля, при котором на входе удерживается нулевое напряжение. Обе фазы проводятся одним и тем же интегратором и компаратором, поэтому вычитание результата «нулевого цикла» из результатов измерения полностью убирают все ошибки, связанные с нулевым уровнем, но не исправляют ошибок полной шкалы.

Отметим, что при двойном интегрировании не нужна даже особая стабильность и точность тактовой частоты. Время интегрирования в первой фазе формируется из целого числа циклов тактовой частоты, и если длительность цикла увеличится на 10% , то на столько же увеличится и уровень напряжения, которого достигнет напряжение на интеграторе, а значит, на столько же увеличится время полного разряда. Из-за того, что тактовая частота понизилась на 10% , число прошедших за время разряда циклов останется тем же! Единственная величина, требующая высокой стабильности в АЦП двойного интегрирования с автоподстройкой, - разрядный ток. Прецизионные источники напряжения и тока сделать относительно несложно, а уже он станет измерительным эталоном.

Преобразователи двойного интегрирования требуют высококачественных конденсаторов с наименьшей величиной диэлектрической абсорбции ( эффект «памяти», см. §5.6.2 и ##§X1.3 ). Наилучшими вариантами будут полипропиленовые, полистирольные и фторопластовые. Это неполярные конденсаторы, но внешнюю сторону фольги ( она обозначается полоской ) надо подключать к низкоимпедансной точке ( выход ОУ интегратора ). Чтобы минимизировать ошибки, значения \(R\) и \( C \) надо подбирать так, чтобы при измерении был задействован полный аналоговый диапазон интегратора. Высокая частота тактирования улучшает разрешение до тех пор, пока его период продолжает быть больше, чем время реакции компаратора.

При работе с АЦП двойного интегрирования ( и вообще любого типа точных преобразователей ) необходимо держать цифровой шум подальше от аналоговых цепей. В АЦП обычно имеется «аналоговая» и «цифровая» земля. Цифровые выводы АЦП очень полезно буферировать ( например, с помощью ’541 - 8-канальных шинных формирователей и выводить их из Z-состояния только в момент считывания данных ), отделяя от цифрового рёва микропроцессорной шины ( см. Часть X4 и 15 ). В некоторых случаях приходится использовать оптические изоляторы ( §12.7 ). АЦП требуют хорошей фильтрации питающих линий в непосредственной близости от микросхемы. Да и вообще, следует поменьше шуметь в ходе преобразования, особенно в самый важный момент - вблизи точки срабатывания компаратора. Некоторые АЦП будто нарочно предоставляют пользователю возможность узнавать об окончании преобразования читая слово состояния. Так делать не надо! 48 Используйте отдельную хорошо изолированную линию «BUSY».

Двойное интегрирование активно используется в цифровых мультиметрах. Этот метод недорог, точен и даёт хорошую повторяемость. Плюс он отлично подавляет сетевую наводку, да и другие виды интерференции тоже, а выходной код с ростом входного напряжения меняется строго монотонно. Но работает такой преобразователь медленно.

==916

В области точности альтернативой является сигма-дельта АЦП. Эта элегантная техника порождает много заблуждений, и в следующей главе ( §13.9 ) туман невежества будет рассеян. Стоит посмотреть на абсолютный рекорд среди интегрирующих АЦП - технику многостадийного интегрирования , придуманную фирмой Hewlett-Packard и реализованную в 8.5-разрядном вольтметре. Но сначала важный обзор методов использования аналоговых ключей.

13.8.5 Аналоговые ключи в измерительных устройствах ( краткий обзор )

Знакомство с аналоговыми ключами произошло в §3.4.1 . В измерительных задачах они приобретают особое значение в качестве деталей самих преобразователей ( см. рис. 13.2 , 13.9 , 13.34 и 13.36 ) и в качестве элементов внешних цепей. В своей исходной роли они стали необходимой частью точных преобразователей многостадийного интегрирования ( §13.8.6 ) и сигма-дельта АЦП ( §13.9 ). Здесь будут кратко рассмотрены некоторые направления использования ключей из числа стандартных логических КМОП микросхем.

13.8.5.A Аналоговые ключи из стандартных логических семейств

Широко распространённые ключи ’4051 и ’4053 из состава семейства КМОП логики особенно удобны в аналоговых схемах, потому что у них есть линия отрицательного питания для аналогового канала и встроенные схемы сдвига уровней. Благодаря этому, микросхемы могут работать во всём диапазоне от \(-V_{EE}\) до \(+V_{DD}\) , а фактически заходя на 0.25 V за оба эти потенциала. В табл. 13.7 перечисляются ключи из состава некоторых логических семейств. Всего имеется три типа: ’4053 - самый привлекательный - три независимых SPDT переключателя; ’4052 - пара мультиплексоров «4-в-1» и ’4051 - одиночный «8-в-1». Привлекают они не только низкой ценой ( менее $0.50 ) и большим числом производителей, но так же высоким быстродействием и низкой ёмкостью.

Скажем, 74HC4053 имеет типичное сопротивление открытого канала 40 Ω , переключается за 20 ns и имеет ёмкость 8 pF . Если сравнивать её с микросхемами, официально предназначенными для переключения аналоговых сигналов, у ’4053 чуть меньший размах входного напряжения и нет защиты от статических разрядов ( ESD ). Если сравнивать с мощными КМОП переключателями, у ’4053 больше сопротивление открытого канала, но меньше ёмкость. Данный ключ хорошо вписывается в задачи переключения сигналов внутри одной печатной платы.

Одиночные версии SPDT ключей доступны в SOT23 и других компактных корпусах. Некоторые такие компоненты, например, ’1G3157 ( «1G» означает одиночный ключ ) не имеют вывода отрицательного питания, поэтому не имеют обозначения «4053» в названии.

Table 13.6 Selected Micropower A-to-D Convertersa Notes: (a) sorted by resolution and maximum speed. (b) all SAR types have S/H or T/H, and no pipeline delay. (c) most SAR types have power proportional to sample rate. (d) I=I2C, S=SPI. (e) in 12-bit mode (10?A for 16-bits ). ( f) cheapest grade. ( g ) assuming linearity, and at same Vs as listed for Is. (h) other packages may be available, consult datasheets. (w) MCP3422 = 18 bits. (x) has digital gain compression, see datasheet. (y ) no latency, ping-pong channel selection. (z) four I/O bits, can use for external MUX.

==917

Рассмотрим парочку примеров, в которых ’4053 образует удобный мостик между цифровым и аналоговым миром. Второй пример с генератором пилообразного напряжения плавно переходит в тему преобразователей многостадийного интегрирования и сигма-дельта АЦП.

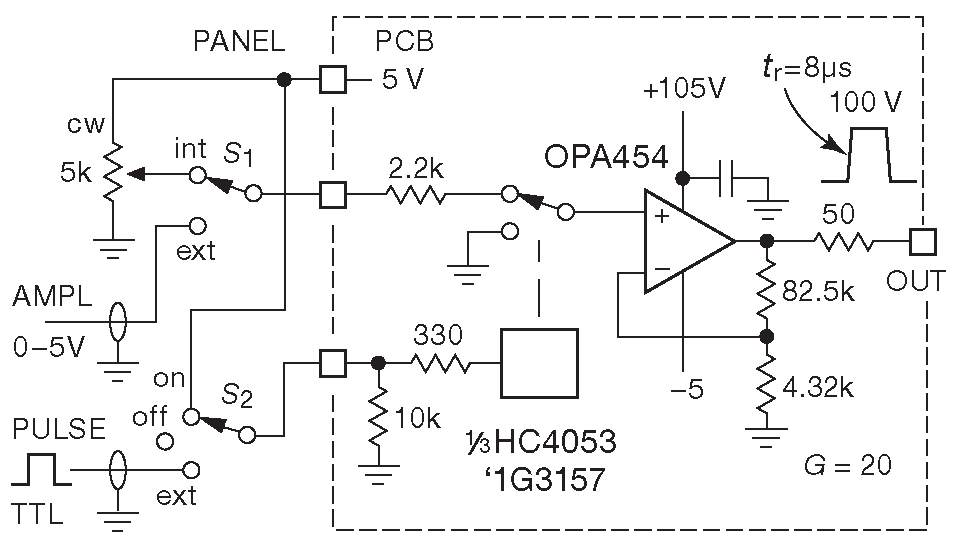

13.8.5.B Программируемый генератор высоковольтных импульсов

Довольно удобно иметь генератор импульсов, сигнал на выходе которого можно включать логическим уровнем, и иметь независимую регулировку амплитуды. Последнюю задачу можно решать ЦАПом под управлением компьютера или набора ручек на панели 49 . Простая схема 13.44 делает всё изложенное, создавая сигналы с амплитудой до +100 V .

Рис. 13.44 Простой генератор высоковольтных импульсов, с программируемой амплитудой и формой. В ключах ’4053 есть вывод отрицательного питания «Vee», позволяющий работать с биполярными сигналами ( ±5V ), а ’3157 - только с положительными

’4053 подаёт потенциал, выбираемый переключателем \( S_1\) , на высоковольтный OPA454, включённый здесь неинвертирующим усилителем с G =20 . ОУ не особо быстрый ( время переключения около 10 μs ), но зато недорог ( $5 ) и может давать 100 mA в емкостную нагрузку. Его можно заменить на что-нибудь пошустрее, чтобы реализовать скоростные возможности ’4053 ( ∼20 ns ) 50 . Переключатель со средней точкой \( S_2\) позволяет включать/выключать импульсы или подать на выход постоянный потенциал, чтобы проконтролировать амплитуду с помощью вольтметра. Сейчас можно найти удобные щитовые приборы, сочетающие функции вольтметра и переключателя.

Table 13.7 4053-style SPDT Switches Notes: (a) TTL logic levels, or TTL available. (b) OFF, common node to gnd. (c) Vtot = \( V_{CC}\)-Vee. (d) depends on manufacturer. (e) at 25? if shown, reflects ATE capability. ( f) delay time from logic input to switch ON, at Vtot; fd( OFF ) is slightly less. ( g ) in 16-pin QFN pkg; quad also available. (m) maximum. (na) no VEE pin. (o) ON Semi.

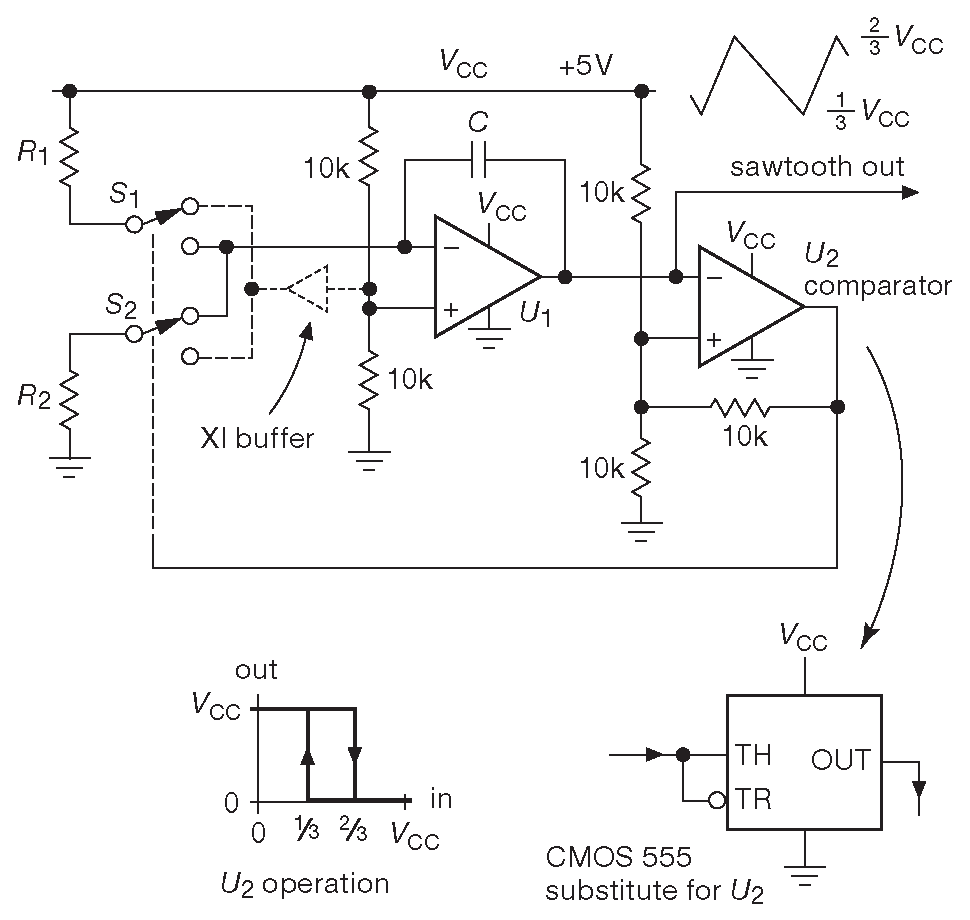

13.8.5.C Генератор пилообразного напряжения с переключаемым током

==918

Схема 13.45 использует очень хорошие характеристики аналоговых ключей ’4053. Предлагаемое переключение токов используется в АЦП многостадийного преобразования, который описывается в следующем параграфе. Суммирующая точка интегратора на \(U_1\) заводится на среднюю точку источника питания ( для работы от однополярного источника +5V ). Ключи \( S_1\) и \( S_2\) типа ’HC4053, подключённые к тем же +5V , задают с помощью резисторов \(R_1\) и \(R_2\) наклон характеристики. Замыкание \( S_1 \) включает источник \( V_{CC}/(2R_1) \) , вызывая спад напряжения интегратора \( dV_{ramp}\space/dt=I/C \) , а \( S_2 \) включает его рост. Пределы переключения компаратора равны 1/3 и 2/3 от \( V_{CC}\) , ограничивая размах пилы величиной \(Δ V=V_{CC}\)/3 . Время роста напряжения равно \( t_R \) =(2/3)\(R_2C\) , время спада - \( t_F \) =(2/3)\(R_1C\) , а частота - \( f \) =1.5/[\( C( R_1+R_2 ) \)] .

Рис. 13.45 Генерация пилообразного напряжения с помощью переключения токов. Триггер Шмитта на компараторе \(U_2\) имеет пороги переключения (1/3)\( V_{CC}\) и (2/3)\( V_{CC}\) . Подойдёт TLV3501 ( \( t_p \) =4.5 ns ) и КМОП 555, но он уже совсем не такой быстрый ( \( t_p \) =100 ns ).

Упражнение 13.4

Докажите данные формулы.

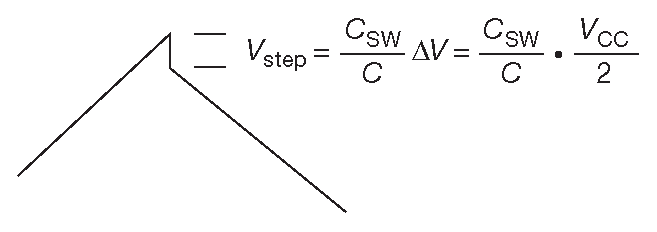

Скорости ключей и компаратора хватает для работы на частоте несколько мегагерц, для которой подойдут резисторы в килоомном диапазоне и конденсатор 100...500 pF . Такая ёмкость уже достаточно мала и заставляет думать об эффектах ёмкости ключей \( C_{SW}\) , которые лежат в пределах 5...10 pF . Рассмотрим работу \( S_1\) в состоянии, показанном на схеме. Его ёмкость заряжается до +5V , после чего передаёт порцию заряда \(Δ Q=C_{SW}·Δ V\) ( где \(Δ V=V_{CC}\)/2 ) в суммирующую точку, когда ключ перекидывается на нижний контакт. Такой перенос заряда вызывает скачок напряжения на выходе интегратора ( рис. 13.46 ). Средством борьбы с этим явлением будет удержание потенциала второго контакта на уровне суммирующей точки ( часть схемы, нарисованная пунктиром ).

Рис. 13.46 Перенос заряда вызывает скачок напряжения на выходе интегратора, когда на его входе замыкается ключ с ёмкостью \( C_{SW}\) , находящейся под иным потенциалом

13.8.6 Примеры для подражания: АЦП многостадийного преобразования фирмы Agilent

Учитывая предыдущий пример с аналоговым переключателем, разобраться с многостадийной техникой преобразования, применяемой в мультиметрах фирмы Agilent 51 34420 ( 7½ разрядов ) и 3458A ( 8½ разрядов ) 52 . Это старшие приборы инструментальных линеек Agilent, занимающие высшие ступени пьедестала уже более 20 лет. Текущая цена ( 2015 ) старшей модели составляет $9.5k. Упрощённый вариант схемы ( «Multislope III» ) используется в серии современных мультиметров, ставших промышленным стандартом - 34420 A ( 7½ разрядов ), 34401A ( 6½ разрядов ) и системе сбора данных 34970A ( 6½ разрядов ). Здесь подробно разбирается работа схемы Multislope III и слегка затрагивается следующее поколение, явленное миру в 2006 - Multislope IV.

==919

13.8.6.A Основные принципы

Если коротко, то многостадийное преобразование стало развитием метода двойного интегрирования, т.е. многоциклового интегрирования с уравновешиванием заряда. Такой подход малочувствителен к параметрам конденсатора и учитывает накопленный остаток в конце цикла преобразования. В многостадийной технике сочетаются приёмы двойного и сигма-дельта интегрирования, а сама она является прямым переходом к сигма-дельта АЦП.

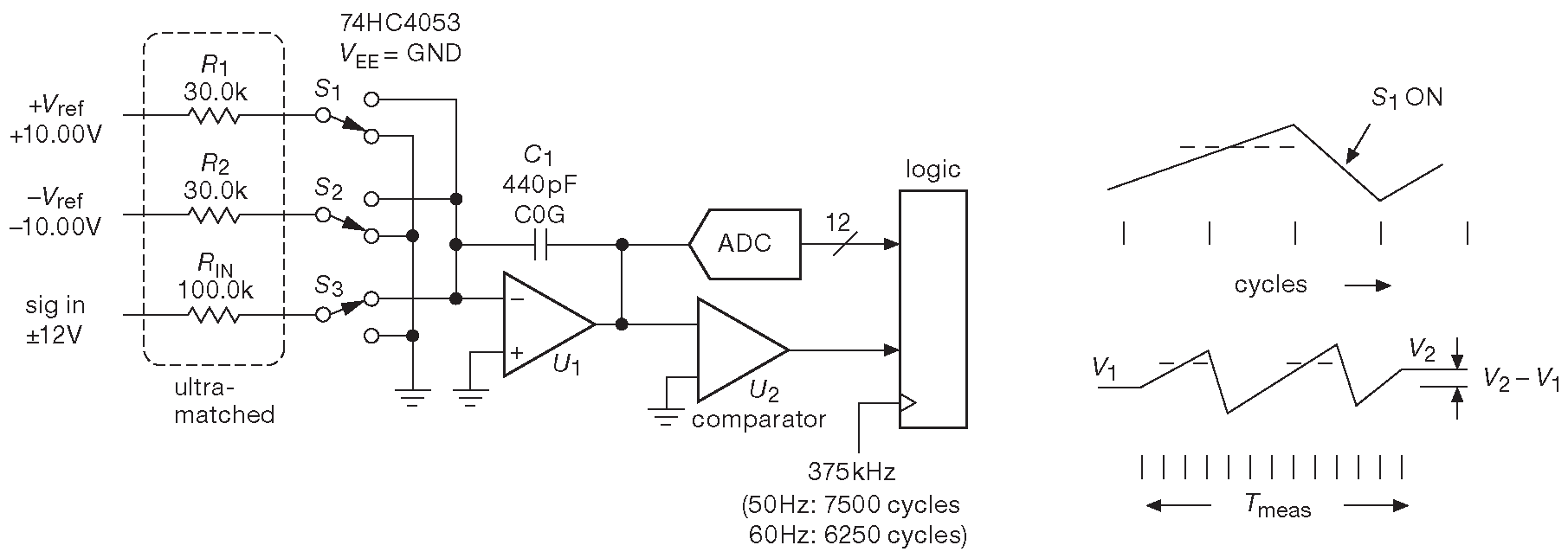

Блок-схема предельно проста ( рис. 13.47 ) и использует по большей части недорогие компоненты ( исключая источники опорного напряжения и прецизионные резисторы ). Схема включает интегратор \(U_1\) , логическую часть, которая через компаратор \(U_2\) смотрит за выходом интегратора в каждом из тактов частоты 375 kHz и два ключа \( S_1\) и \( S_2\) , балансирующие интегратор, закачивая и откачивая из него ток. АЦП с очень скромной точностью ( 12 разрядов ) используется для считывания выхода интегратора в начале и конце общего цикла измерения.

Рис. 13.47 Схема измерения Multislope III. Тактируемый интегратор с уравновешиванием заряда и коррекцией по конечным точкам с помощью вспомогательного АЦП малой разрядности

Теперь, как это в принципе работает. Чтобы начать измерение, надо замкнуть ключ \( S_3\) 53 , что вызовет изменение напряжения на выходе интегратора вверх или вниз в соответствии с соотношением \( dV/dt=-I_{in}/C_1=-V_{in}/(R_{in}·C_1) \) . В каждом последующем такте системной частоты схема замыкает ключ \( S_1\) или \( S_2\) ( согласно полярности напряжения на выходе интегратора ), добавляя или вычитая образцовый ток от соответствующего опорного источника ( ±10 V/30 kΩ ) и заставляя выход интегратора менять направление в сторону нулевого уровня. Это продолжается на протяжении достаточно большого числа тактов. Чтобы по максимуму подавить наводки от сетевой частоты желательно использовать в качестве системного времени какую-либо частоту, кратную сетевой, например, чтобы 6250 циклов соответствовало 1/60 или 1/50 секунды. В результате система получает число положительных ( \(n_P\) ) и отрицательных ( \(n_M\) ) циклов. Это даёт первое приближение среднего входного напряжения за время измерения \[ V_{sig}(1)≈ V_{REF}\frac{n_M-n_P}{N_{cycles}}\frac{R_{in}}{R_1}=V_{REF}\frac{n_M-n_P}{6250}\frac{100k}{30k}. \]

Всё это пока не поражает точностью: при максимальном входном сигнале ±12 V получается ( \(n_M – n_P\) ) или ±2250 отсчётов ( покажите почему ), что соответствует 12-разрядному разрешению. А теперь следите за руками: из-за того, что измерение продолжалось какое-то целое число тактов, не прерываясь событиями наподобие равенства нулю, как в двойном интегрировании, напряжение на интеграторе содержит дополнительные данные и позволяет провести уточнение дробной части результата, как это происходит в вереньерных шкалах. Именно для этого нужен 12-разрядный АЦП на блок-схеме 13.47 . Он используется для измерения уровня на интеграторе перед началом цикла измерения и по его окончании. Для 12-разрядного АЦП это даёт дополнительные 512 уровней разрешения внутри LSB исходной системы первого приближения, т.е. добавляет 9 бит к 12 , полученным на первом этапе. В итоге получаем результат с точностью 21 разряд 54 .

==920

Более точный ( и окончательный ) результат даёт выражение: \[ V_{sig}(2)=V_{sig}(1)+\frac{R_{in}C_1}{T_{meas}}( V_f-V_i )=V_{sig}(1)+0.00264( V_f-V_i ), \] где коэффициент, соответствующий «вереньерной» части, представляет вклад от коррекции по конечным точкам уменьшенный в степени удлинения времени измерения. [* Т.е. для десяти циклов один цикл, он же «вереньерная часть» составляет 1/10 , для ста - 1/100 и т.д ]. . Таким образом, легко показать, что для однотактного измерения ( \( T_{meas}=1/f_{clk}\) ) всю информацию о сигнале будет содержать «вереньерная часть» \(Δ V\) .

Упражнение 13.5

Покажите, что это утверждение верно.

13.8.6.B Некоторые подробности

Это только общий обзор техники непрерывного преобразования. Здесь много о чём можно говорить: в деталях прячется целый табун дьяволов. Метод можно улучшать множеством доступных способов, добиваясь наибольшей точности в рамках исходной идеи. Здесь авторы наступят друг другу на горло и сократят комментарии до краткой выжимки из наиболее интересных и поучительных подробностей.

- Некритичные компоненты

- В качестве \( S_1\) - \( S_3\) Agilent использовал обычные микросхемы 74HC4053 производства NXP, а в качестве \( C_1 \) - массовый керамический конденсатор для поверхностного монтажа со стабильным диэлектриком NP0/C0G фирмы AVX. Этот тип конденсаторов очень дёшев 55 , имеет малый температурный коэффициент ±30 ppm/°C и пренебрежимо малую диэлектрическую абсорбцию ( эффект «памяти», см. рис. 5.4 , §5.6.2 и подробное обсуждение в ##§X1.3 ), особенно при таких временах переключения. Высокая точность и стабильность компаратора и АЦП тоже не нужна.

- Критичные компоненты

-

Источник опорного напряжения устанавливает шкалу измерения и должен иметь высокую стабильность. В приборе используется один 7-вольтовый опорный источник на основе стабилитрона и два прецизионный операционных усилителя, чтобы получить ±10.0 V опорного напряжения 56 . Конкретная величина потенциала «10.0 V» неважна, т.к. будет учтена при калибровке, но это напряжение обязано быть стабильным, чтобы калибровочные значения как можно дольше отражали реальное положение вещей 57 .

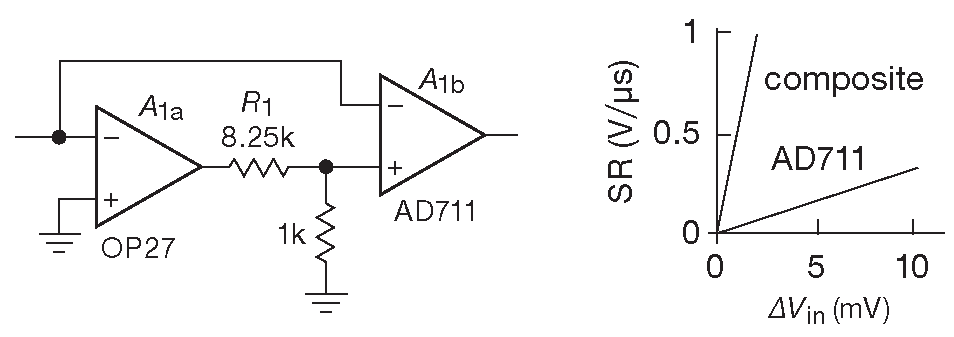

Ещё одним критичным компонентом является резисторная сборка \(R_1 – R_3\) ( масштабирующие резисторы в опорном источнике ) и ОУ, на котором собран интегратор. Последний представляет собой композитный усилитель ( OP27+AD711 ), имеющий высокое петлевое усиление в сочетании с низким напряжением смещения ( рис. 13.48 ). В качестве набора резисторов используется специальная точно подогнанная сборка, с хорошей стабильностью отношения. Здесь очень важен дрейф ( по времени и температуре ) отношения резисторов, потому что небольшое исходное расхождение также убирается заводской калибровкой.

Рис. 13.48 «Композитный усилитель» сильно увеличивает скорость нарастания. Номинал межкаскадного аттенюатора 8.25 kΩ выбирался, чтобы обеспечить стабильность \(U_1\) [* в схеме 13.47 ]

Не показанный, но тоже важный, входной усилитель с программируемым усилением. Его усиление должно иметь высокую точность и стабильность, чтобы сохранять параметры настройки и калибровки, см. §5.12 .

- Переключатели

- Ключи 74HC4053 используются в схеме распределения тока, подобной варианту на рис. 13.45 , и включены так, чтобы напряжения на всех выводах ключа поддерживались на близком к нулевому уровне. ’4053 используются только для переключения токов, чтобы повысить или снизить скорость роста напряжения на выходе интегратора, которая находится в точной зависимости от входного напряжения. Сопротивление открытого канала, конечно, оказывает на токи заметное влияние, но пока \(R_{on}\) ключей хорошо согласовано, стабильно и мало по сравнению с \(R_1 – R_3\) , его влияние можно учесть калибровочными циклами, которые прибор проводит в автоматическом режиме перед каждым измерением ( см. описание процесса калибровки ниже ). Для микросхем производства NXP, которые стоЯт в приборе, \(R_{on}\) имеет типовое значение 85 Ω и согласовано до 8 Ω . Очень важной особенностью является разрыв соединения перед переключением , благодаря чему выводы никогда не бывают закорочены ( что замкнуло бы внутреннюю суммирующую точку на землю и проявилось бы на входе как дифференциальный сигнал, равный напряжению смещения ОУ ). Одни производители упоминают данный факт в документации, другие - нет. Например, паспортные данные NXP указывают времена включения и выключения, разница между которыми и определяет время разрыва цепи 4 ns . Но прямо данное время не указывается, а, скажем, в справочных данных на DG4053 фирмы Siliconix есть параметр «Break-Before-Make Time Delay» \( t_D\)=6 ns (тип.) или 2 ns ( мин. ).

==921

- Калибровка

- Простая схема переключения токов очень удобна для калибровки и устранения эффектов неточного согласования резисторов, неточности опорного напряжения, смещений ОУ, задержек ключей и т.п. Например, когда \( S_3\) выключается ( т.е. входной сигнал отсутствует ), для \( S_1\) и \( S_2\) можно провести несколько последовательных циклов переключения. Накопившийся в результате этого действия потенциал \(Δ V\) на выходе интегратора отражает разницу положительного и отрицательного токов. По аналогии, подав на вход \( V_{REF}\) , вместо сигнала, и проведя измерение можно выяснить отклонение опорных токов от номинальной величины. Перед каждым измерением с наибольшей точностью, когда разница имеет значение, прибор проводит серию таких калибровок. Естественно, обнаружить таким методом дрейф опорного источника нельзя. Чтобы поверять его, нужен внешний источник образцового напряжения, и на этом делают деньги поверочные службы.

- Интервал измерений

- Ранее в примере мелькала цифра \( T_{meas}\) , равная одному периоду сетевой частоты или 6250 циклам частоты 375 kHz , или 1/60 ( 1/50 ) сек. Время измерения есть целое число циклов PLC ( NPLC ). Оно позволяет подавить наводку, а итоговая точность зависит от общей продолжительности цикла измерения, см. табл. 13.8 . Но, согласно данным таблицы, можно делать быстрые измерения, если несколько поступиться точностью и степенью подавления сетевых наводок 58 . Возможен также режим непрерывного измерения, при котором ключ \( S_3\) всегда замкнут ( в этом режиме время измерения регулируется извне ).

- «Многомногостадийное измерение»

- Вернёмся к исходному примеру - 8.5-разрядному мультиметру HP3458, в корне изменившему расклад сил. В нём есть четыре набора входных резисторов и ключей. Это позволяет очень сильно ( почти в 600 раз ) понизить скорость нарастания при приближении к моменту окончания измерения 59 . Причём необычен отказ от использования красивого приёма - измерения остатка напряжения на интеграторе с помощью АЦП, а вместо этого проводится его линейный разряд до 0V .

- Прочее

- Остаётся ещё масса деталей итоговой реализации этой методики, которые описаны в руководстве по обслуживанию, статьях из HP Journal, и патентах 60 . Например, данная техника предполагает только борьбу с насыщением интегратора, а значит, можно использовать больше одного компаратора и включать токовые ключи \( S_1\) и \( S_2\) , только чтобы удерживать интегратор от насыщения. Это уменьшает число циклов переключения и связанных с ними ошибок. Есть и необычные схемные решения: ферритовые бусины на аналоговых входах ’4053 и конденсатор между суммирующей точкой интегратора и землёй. Смотрите схему.

- Эволюция метода

- В 2006 году Agilent представил более быструю линейку «Multislope IV» 61 - модели 34410 A, 34411A и 34972A с USB и Ethernet на борту. СтОят они дороже, а цена на классические модели 34401A и 34970A была снижена. Заявлены модели 34460A и 34461A с графическими дисплеями и специальными интерфейсами для датчиков ( 34461A имеет такую же скорость измерения как и 34401A, табл. 13.8 ). 34420 A замены не получил и остался единственным 7.5-разрядным ( 20 ppm ) прибором в линейке.

Табл. 13.8 АЦП Multislope III фирмы Keysight Notes: (a) 34401A DMM, 34420 A MicroVolt, 34970A DAQ. (b) powerline cycles; selectable 50/60 Hz via setup menu. (c) when set for 60 Hz; clock rate is 375 kHz. (d) reported. (e) normal-mode rejection, at selected powerline freq. ( f) 7.5 digits for the 34420 A. ( g ) 34420 A only.

13.8.6.C От многостадийных к сигма-дельта

==922

Многостадийные АЦП плавно подводят нас к очень широко используемой технике сигма-дельта преобразования, с которой имеют много общего. Оба используют интегрирование, при котором входной сигнал на периодической основе сравнивается с выходным напряжением интегратора. Как будет видно чуть позднее, в глубине сигма-дельта техники таятся некоторые тонкие отличия, позволяющие достигать фантастических параметров.

==922

48 Хорошо, если вам так хочется, читайте, но только когда измерение гарантированно завершено. <-

49 В Части _5 был показан способ создания высоковольтных сигналов ( рис. 5.47 ), но без возможности стробирования выхода. <-

50 Cirrus/Apex PA85 имеет скорость 1000 V/μs ( при коэффициенте усиления с обратной связью G =100 ) и работает от источника питания с общим напряжением 450 V . В данном случае можно было бы подключить его к +400 и -15 V , но придется раскошелиться: стоит этот усилитель около $300 ( см. вывоковольтовые ОУ в табл. 4.2b ). Дешевле будет собрать что-нибудь своё в соответствии с идеями на рис. 3.111 . См. главу, посвящённую точным высоковольтным усилителям в Части X4 . <-

51 Hewlett-Packard или «HP» ( 1939-1999 ), Agilent ( 1999-2014 ), Keysight ( с 2014 и по настоящее время ). <-

52 3458A описывается на сайте Keysight в материале под названием «Recognized the world over as the standard in high performance DMMs» [* я его не нашёл ] . <-

53 Термин «замкнут» означает, что соответствующий ключ подключён к суммирующей точке. <-

54 Диапазон преобразования АЦП соответствует рабочему диапазону интегратора, и оба примерно в 8 раз больше, чем изменение напряжения на интеграторе за время одного такта для входного сигнала полной шкалы. Именно в этом состоит причина потери 3 разрядов результата ( при оцифровке остатка ( \( V_f-V_i\) ) . <-

55 $0.06 в партии 100 шт. Сегодня на DigiKey есть 50'000. [* Тип таки забыли указать ]. <-

56 Речь идёт о пресловутом LTZ1000, который использует Agilent §9.10.1.B . <-

57 Начальная точность стандартного настольного вольтметра 34401A лежит в пределах ∼2 ppm , обещан дрейф не более ±0.0015% за 24 часа, но ±0.0035% по прошествии года работы. <-

58 В современных моделях Keysight базовую технику многостадийного интегрирования улучшили и вольтметр 34411A может давать 1000 отсчётов в секунду с точностью 6.5 разрядов или 50'000 отсчётов в секунду при 4.5 разрядах. <-

59 Эта последовательность циклов с разным наклоном кривых разряда, возможно, послужила появлению приставки «multi» в «multislope». Торговая марка «Multislope III» используется в более поздней ( и простой ) схеме, которая описывалась ранее. <-

60 HP Journal, April 1989; Патенты США 4,357,600 и 4,559,521. <-

61 Если посмотреть сигналы в Multislope IV осциллографом, можно обнаружить нечто совершенно иное. \( A_{1b}\) ( рис. 13.48 ) был заменён на быстрый ОУ AD829 ( 120 MHz, 230 V/μs ), а ёмкость интегрирующего конденсатора \( C_1 \) ( рис. 13.47 ) уменьшена в пять раз. Интегратор имеет рабочий диапазон 10 Vpp и накапливает заряд от входного сигнала в течение 2 μs . Далее начинается разрядный цикл. Каждые 14 ns система получает грубое значение полного 10-вольтового диапазона с 80-мегагерцового 8-разрядного АЦП AD9283, и каждые 75 ns уточняющее значение 10-разрядного AD9200, который меряет выход интегратора в диапазоне 0...2 V [* пока напряжение на интегрирующем конденсаторе выше 2V AD9200 должен казать состояние «переполнения» и только ближе к моменту окончания разряда выдавать реальные цифры ] . Счётчик времени разряда накапливает число «75 ns»-интервалов [* я правильно понимаю, что это те самые интервалы, когда точный АЦП выдаёт «переполнение» ? ] , плюс по данным обоих АЦП строится график разряда. По этим данным становится возможен расчёт интересующего напряжения с точностью 0.02% . [* Т.е. меряем грубо и получаем несколько точек на графике выше 2V . Заряд-разряд ведётся источником тока, т.е. график - треугольник из прямых линий, положение которых можно весьма точно определить по нескольким грубым и нескольким точным ( ближе к концу разряда ) отсчётам ]. В итоге Multislope IV может делать измерения с точностью 4.5 разряда за 20 μs ( 0.001 PLC ), т.е. в 20 раз быстрее, чем Multislope III.

[* Я на самом деле не понял, что там написано и просто попытался реконструировать процесс по имеющимся данным. Или ешьте, что дают, или читайте оригинальный текст книги, который приводится ниже ].

«Looking at Multislope IV waveforms with a scope, you see a much different beast. \( A_{1b}\) has been replaced with a faster AD829 op-amp ( 120 MHz, 230 V/μs ), with the integrating capacitor \( C_1 \) reduced by 5×. A hardware engine forces the error integrator to produce consistent 10 Vpp ramps with a 2 μs period, using coarse data from an 80 MHz AD9283 converter digitizing the 10 V ramp at 14 ns intervals, and fine data from an AD9200 10-bit converter with a limited 2V range, clocked at 75 ns intervals near zero volts. Slope changes and the counter record are made at 75 ns intervals, and the AD9200 makes starting and ending readouts with 0.02% resolution. As a result, a Multislope IV converter can measure 4.5 digits in 20 μs ( 0.001 PLC ), or 20× faster than Multislope III.»<-