13.13 (I) Фазовая автоподстройка

==955

13.13.1 Введение в фазовую автоподстройку

Фазовая автоподстройка частоты или ФАПЧ - интересный и полезный электронный блок, доступный как в виде отдельного компонента, так и в составе более сложных микросхем. Содержит фазовый детектор, усилитель и генератор, управляемый напряжением , и сделан по смешанной цифро-аналоговой технологии ( называемой ещё «техникой смешанных сигналов» ). В число приложений входят синтез частоты, получение и восстановление несущей, декодирование тональных посылок, AM, FM и прочих модулированных сигналов.

==956

В прежние времена распространение PLL сдерживалось сложностью конструкции и ненадёжностью работы. По мере появления недорогих и удобных схем автоподстройки в интегральном исполнении исчез первый барьер, а правильный подход к проектированию превратил PLL в столь же обычный элемент, как и D-триггер.

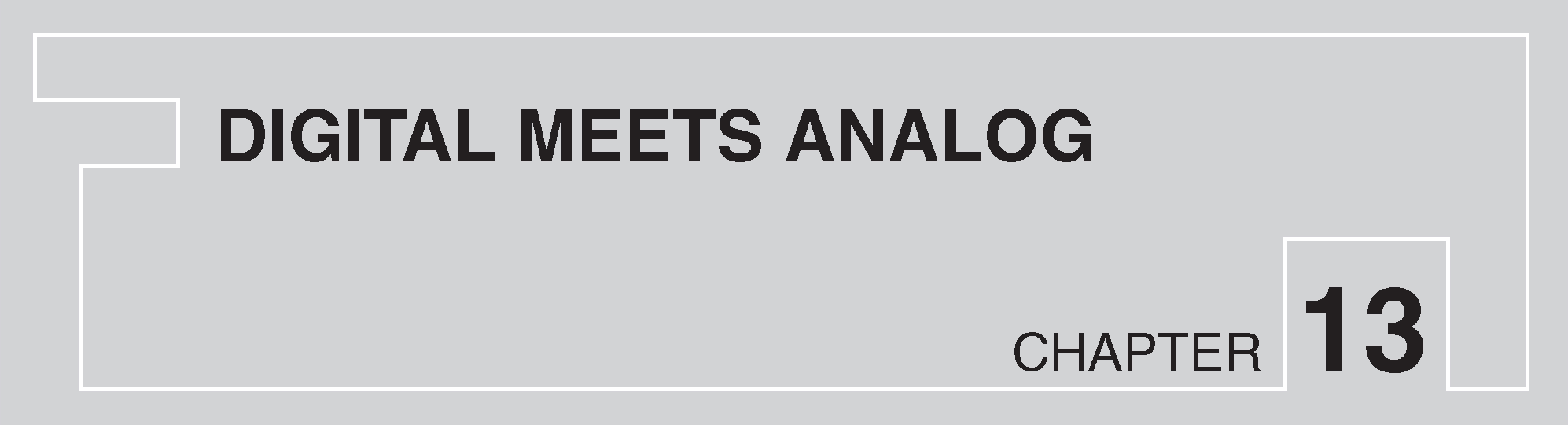

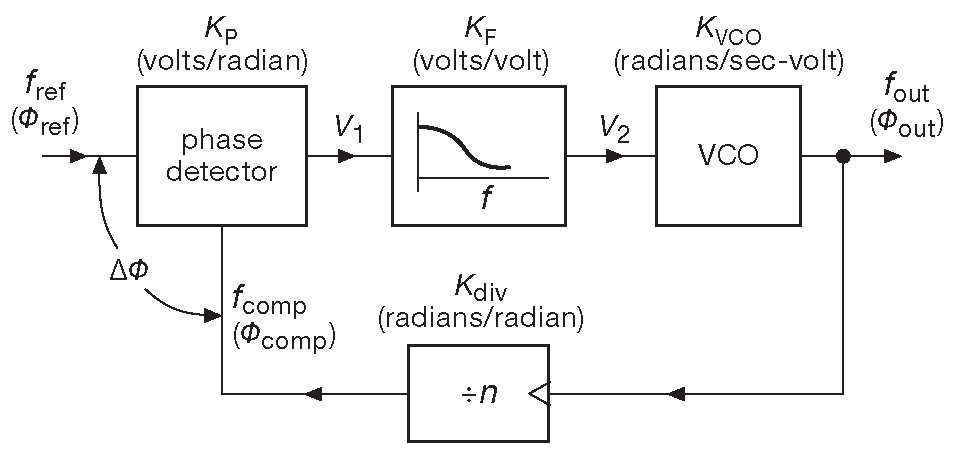

Классическая конфигурация показана на рис. 13.85 . Фазовый детектор сравнивает две частоты, создавая сигнал, пропорциональный разности их фаз. Когда речь идёт о разных частотах, на выходе детектора присутствует периодический сигнал с разностной частотой. Если \( f_{in}\) не равна \( f_{VCO}\) , сигнал фазовой ошибки после фильтрации и усиления используется для коррекции частоты VCO в направлении \( f_{in}\) . Если параметры правильные ( подробнее об этом чуть позднее ), VCO быстро «захватывает» \( f_{in}\) , сохраняя определённое соотношение фаз между двумя сигналами.

Рис. 13.85 Фазовая автоподстройка частоты

В этот момент на отфильтрованном входе фазового детектора присутствует постоянный сигнал, пропорциональный входной частоте. Очевидное применение - детектирование тона ( используется в телефонии ) и демодуляция FM сигнала. Выход VCO - частота, равная входной, возможно, зашумлённой \( f_{in}\) , и может использоваться в качестве чистой локальной копии. Причём на выходе VCO может быть треугольный сигнал, синусоидальный или какой-либо иной, т.е. это удобный способ получения сигнала произвольной формы, синхронизированного с заданным.

Одной из самых распространённых схем использования PLL является создание частоты, кратной «по-модулю-n» опорной \( f_{in}\) . Это идеальный способ создания тактовой частоты для интегрирующих АЦП ( двойного интегрирования и уравновешивания заряда ), где в качестве опорной выступает частота питающей сети. Данный способ позволяет улучшить подавление сетевой наводки и её гармоник. Так же строятся синтезаторы частот.

==957

13.13.2 Компоненты схемы фазовой автоподстройки

13.13.2.A Фазовый детектор

Начнём рассмотрение с фазового детектора. Есть два основных типа, часто называемых «тип I» и «тип II».

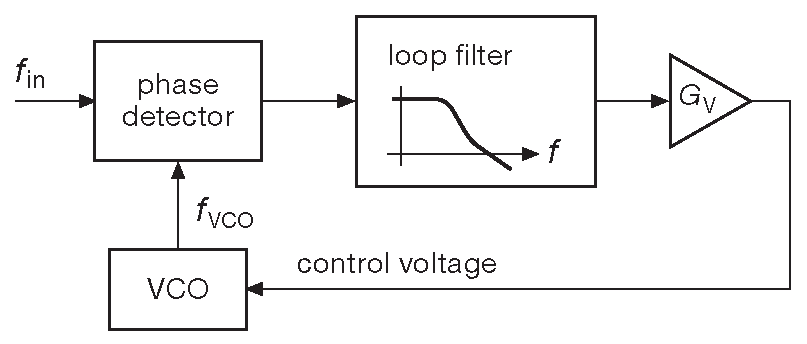

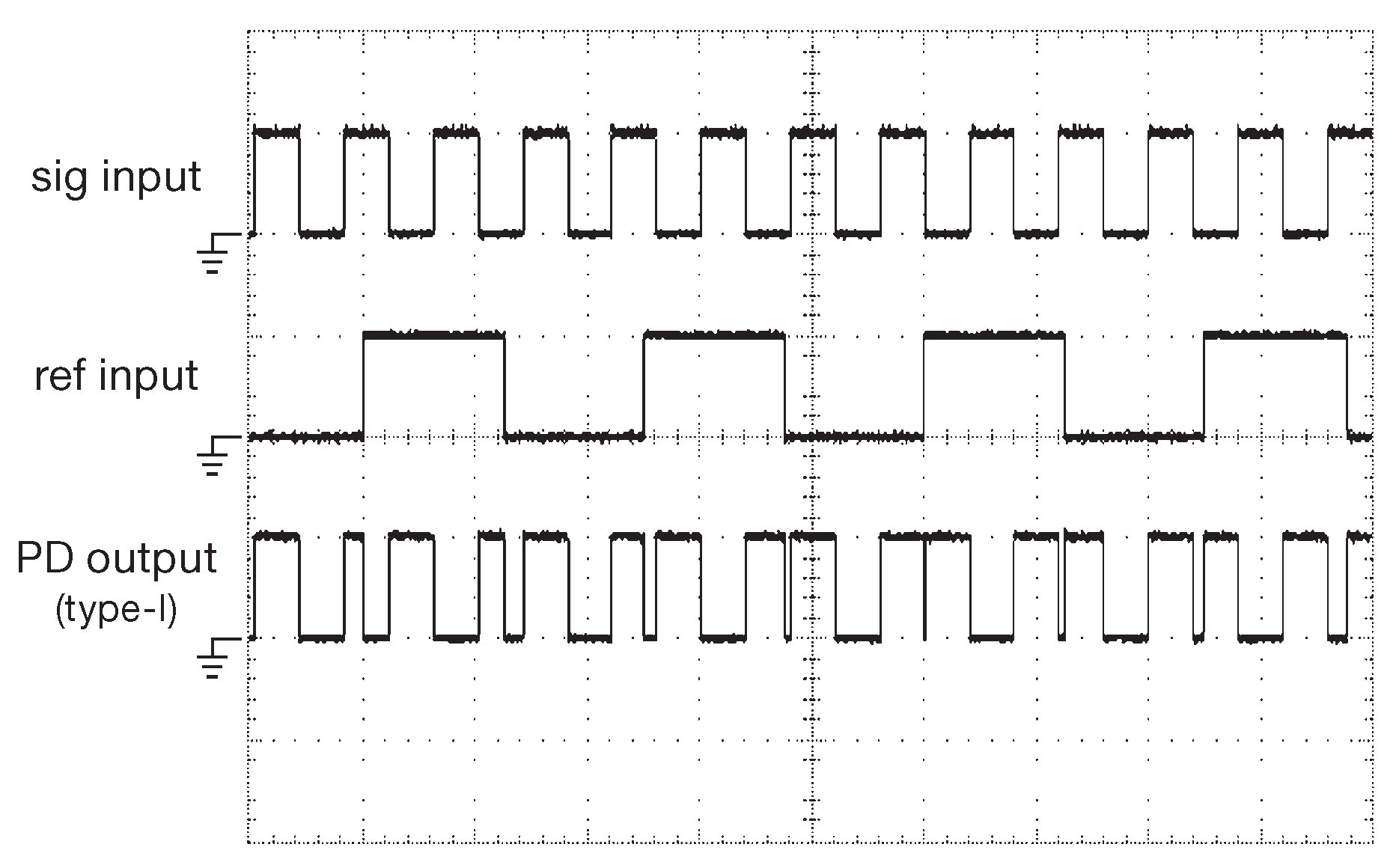

- Фазовый детектор типа I

- Применяется как для аналоговых, так и для цифровых сигналов и выполняет простое перемножение входных сигналов. Для цифровых сигналов используется простая схема «ИСКЛЮЧАЮЩЕЕ-ИЛИ» ( рис. 13.86 ). После ФНЧ зависимость выходного сигнала от разности фаз напоминает треугольный сигнал. На рисунке показана временная диаграмма для скважности входных импульсов 50% . Для аналоговых сигналов в качестве типа I выступает линейный умножитель ( называемый также «четырёхквадрантным умножителем» или «балансным смесителем» ) [* см. рис. 8.116 на стр. 575 ] . Его характеристики аналогичны цифровому фазовому детектору на логическом элементе XOR. Фазовые детекторы с высокой степенью линейности - обязательный элемент схемы синхронного детектирования .

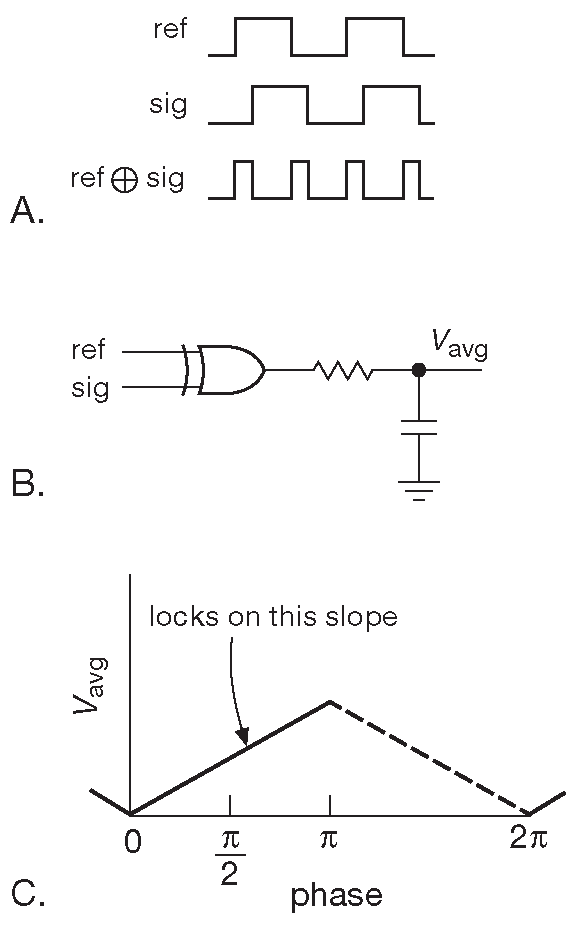

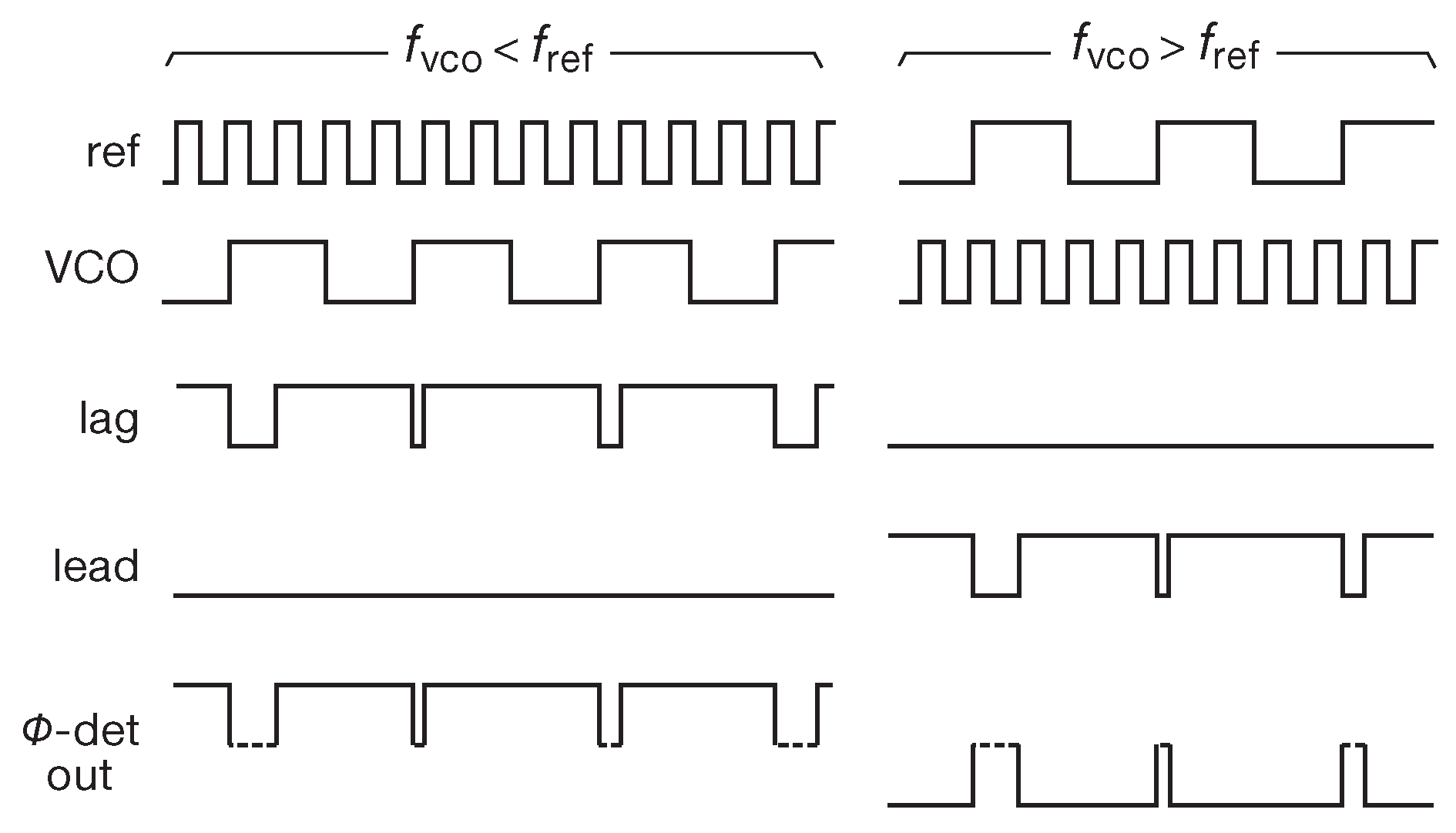

- Фазовый детектор типа II

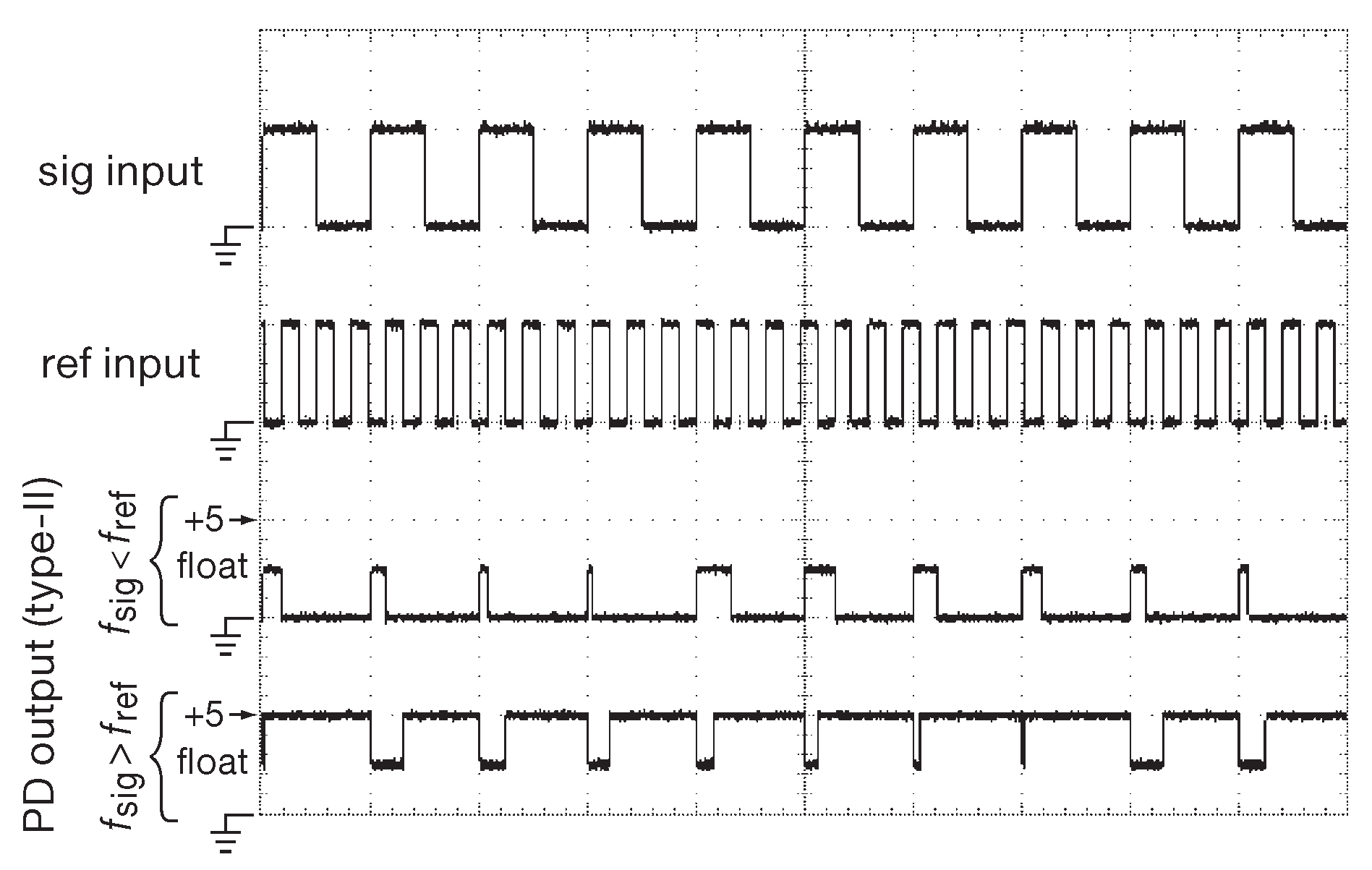

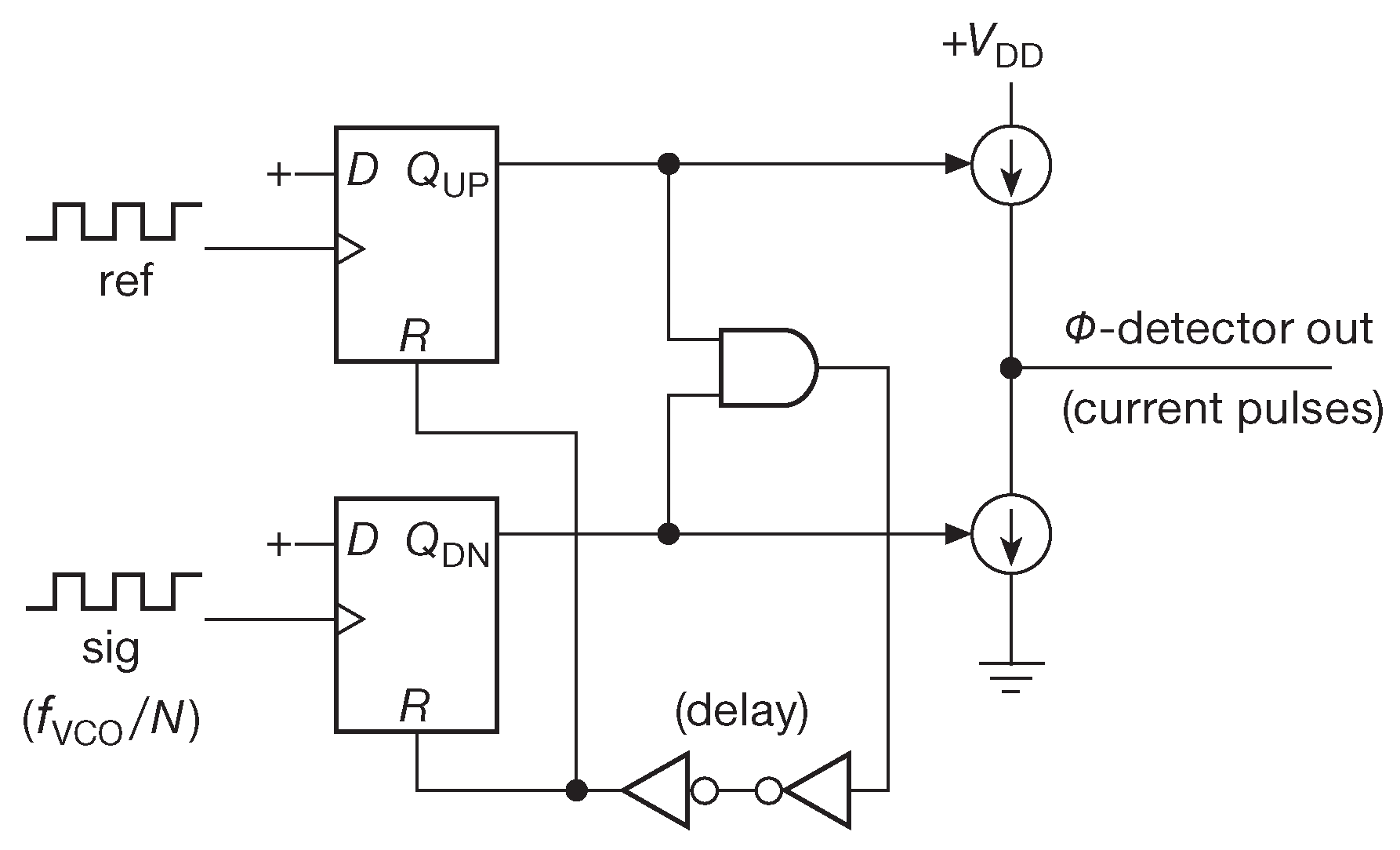

- Чисто цифровое устройство, реагирующее на фронты входных сигналов. Он чувствует только относительное время между фронтами входного сигнала и выхода VCO ( рис. 13.87 ). Компаратор фазы выдаёт только импульсы опережения, если фронт от VCO приходит раньше опорного сигнала, или импульсы задержки, если фронт от VCO приходит позже фронта опорного сигнала. Ширина импульсов равна задержке между появлением фронтов. Выходной каскад принимает или отдаёт ток в активной фазе импульса и находится в третьем состоянии остальное время, создавая сигнал, пропорциональый средней разнице фаз ( рис. 13.88 ). Такая схема, в отличие от типа I, совершенно нечувствительна к скважности входных импульсов.

Рис. 13.86 Фазовый детектор на элементе «ИСКЛЮЧАЮЩЕЕ-ИЛИ» ( тип I )

Рис. 13.87 Фазовый детектор, чувствительный к опережению/отставанию фронтов сигналов ( тип II )

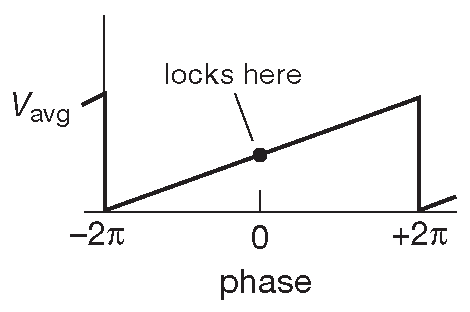

Рис. 13.88 Выход фазового детектора типа II

Тип II характеризуется отсутствием выходных импульсов при нулевой разнице фаз сигналов ( состояние синхронизации ). Это также означает и отсутствие пульсаций на выходе. Такие пульсации свойственны типу I и приводят к постоянному изменению взаимного расположения фронтов. Отдавая должное типу II, стоит отметить, что у него есть ещё одна приятная особенность: он создаёт постоянное напряжение, показывающее знак разницы фаз ( рис. 13.89 , 13.90 и 13.91 ). По этой причине, его иногда называют фазо-частотным детектором - PFD . Скоро будет показано, как это помогает процессу захвата в PLL.

Рис. 13.89 Фазовый детектор типа II создаёт усреднённый постоянный выходной сигнал, показывающий знак разницы частот

Рис. 13.90 Выходной сигнал детектора типа II при большой разнице входных частот. Два входных сигнала ( верхние лучи ) вызывают появление выходного сигнала фазового детектора ( третий луч ) который нагружен на среднюю точку делителя 10 kΩ + 10 kΩ ( +2.5 V ). Нижний луч показывает картину для обратного соотношения частот ( входной и опорный сигналы поменяны местами ). По горизонтали 1 ms/div Рис. 13.91 Для сравнения, реакция фазового детектора типа I (XOR ) на набор сигналов с рис. 13.90 . На выходе получается безумный сигнал, мечущийся между уровнями питания, с постоянной составляющей в районе \( V_{CC}\)/2. По горизонтали 0.4 ms/div

Классическая схема PLL 74HC4046, которая включает и генератор, и фазовый детектор, даёт возможность выбрать тип детектора ( внутри есть оба ). Приведём их свойства:

==958

Type II

Type I edge triggered Parameter exclusive-OR (“charge pump”) Input duty cycle 50\text% optimum Irrelevant Lock on harmonic? Yes No Rejection of noise Good Poor Residual ripple at 2/IN High Low Lock range (L) Full VCO range Full VCO range Capture range /L(/ < 1 ) L Output frequency /center fmin when out of lock

Есть ещё одно различие двух типов. Первый всегда имеет на выходе сигнал, который необходимо фильтровать ( об этом далее ). Поэтому PLL с фазовым детектором типа I в петле обратной связи всегда есть ФНЧ, который чуть сглаживает выходные логические сигналы. Т.е. на выходе всегда имеются пульсации, ведущие к постоянному изменению фазы в петле обратной связи. В схемах, где PLL используется для синтеза частот, данное явление вызывает к жизни «боковую полосу модуляции фазы» в выходном сигнале.

Фазовый детектор типа II выдаёт на выход импульсы, только если есть разница фаз между опорным сигналом и частотой VCO. Так как всё остальное время выход находится в третьем состоянии, конденсатор фильтра обратной связи хранит управляющее напряжение для VCO. Если его частота уйдёт, фазовый детектор выдаст серию коротких импульсов. зарядит ( или разрядит ) конденсатор до нужного управляющего напряжения и вернёт VCO в режим синхронизации. Так работает интегратор фазовой ошибки.

«Мёртвая зона» и «скольжение частоты»

Постоянной проблемой первых PLL, использующих детектор типа II, была проблема мёртвой зоны. Околонулевая разность фаз порождала столь малые коррекционные импульсы, что цепь обратной связи начинала «гулять» ( качаться вперёд-назад ), вызывая модуляцию фазы или «джиттер» . Это явление усугубляется эффектами емкостной нагрузки на выходе фазового детектора. Для применений, требующих чистого стабильного сигнала ( сотовой связи, приёмников, синтезаторов частоты ) - это серьёзная проблема. Решением, которое сейчас используется почти повсеместно, стало создание зоны перекрытия зарядных и разрядных выходных импульсов. Чтобы это стало возможно, требуется переделка фазового детектора: он должен выдавать импульсы тока, а не напряжения.

==959

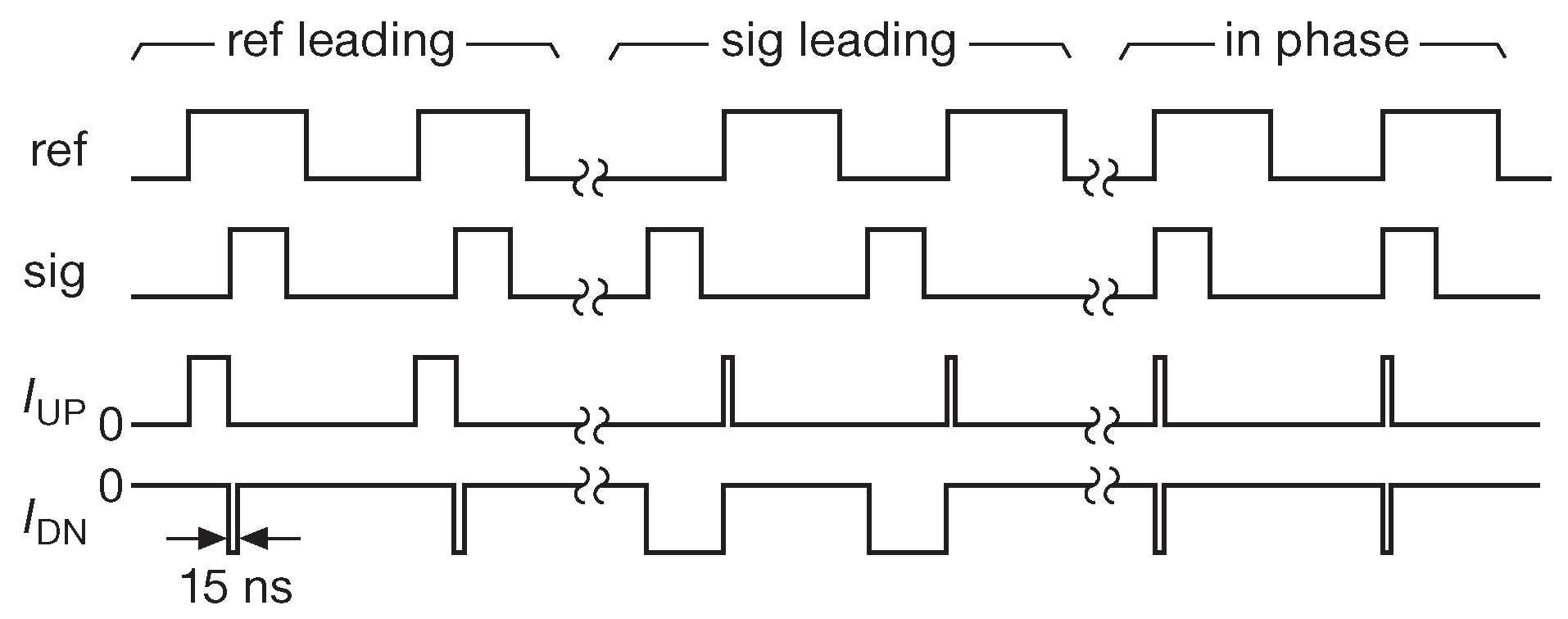

Как решается такая задача показывает схема 13.92 . Источник или приёмник тока включается первым пришедшим возрастающим фронтом, безразлично, опорного сигнала или VCO, и не выключается до тех пор, пока не закончится жёстко заданный минимальный интервал времени. Такая схема противодействия «скольжению частоты» гарантирует, что выходные импульсы никогда не пропадают. Когда два сигнала точно «в фазе» ( произошла синхронизация ), оба токовых импульса имеют заданную минимальную длительность ( ∼15 ns для 74HCT9046 - улучшенной версии 74HC4046 ) и противоположный знак, полностью взаимно компенсируясь ( рис. 13.93 ). Как только появляется рассогласование, возникает и разбалансировка импульсов. Такое линейное поведение схемы в области нуля решает проблему, причём емкостная нагрузка только помогает, работая в качестве интегратора.

Рис. 13.92 Улучшенный вариант фазового детектора типа II ( показана микросхема 74HCT9046 ), в котором ключи заменены источниками тока, что позволяет за счёт перекрытия импульсов избавиться от мёртвой зоны и скольжения частоты

Рис. 13.93 Зарядные и разрядные токовые импульсы схемы 13.92 . Импульсы шириной 15 ns создаются цепью защиты от «скольжения»

Простой способ подавить болтанку вблизи нуля - просто поставить резистор большого номинала параллельно конденсатору фильтра ( \( C_2\) на схеме 13.87 ), который выведет рабочую область обратной связи из мёртвой зоны. Заплатить придётся постоянным ненулевым сдвигом фаз, причём не слишком предсказуемым, но, по крайней мере, не будет джиттера.

13.13.2.B Генератор, управляемый напряжением

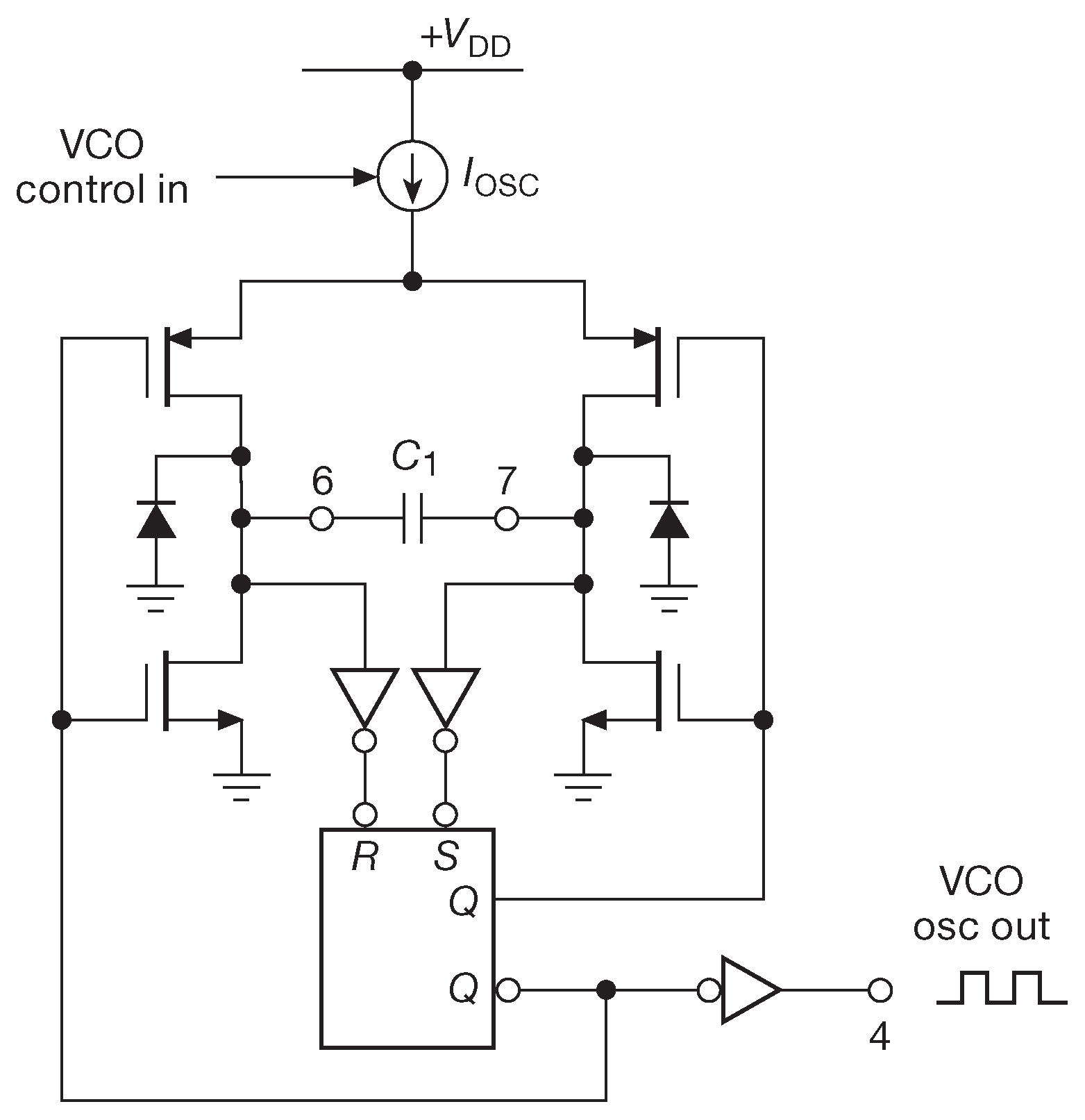

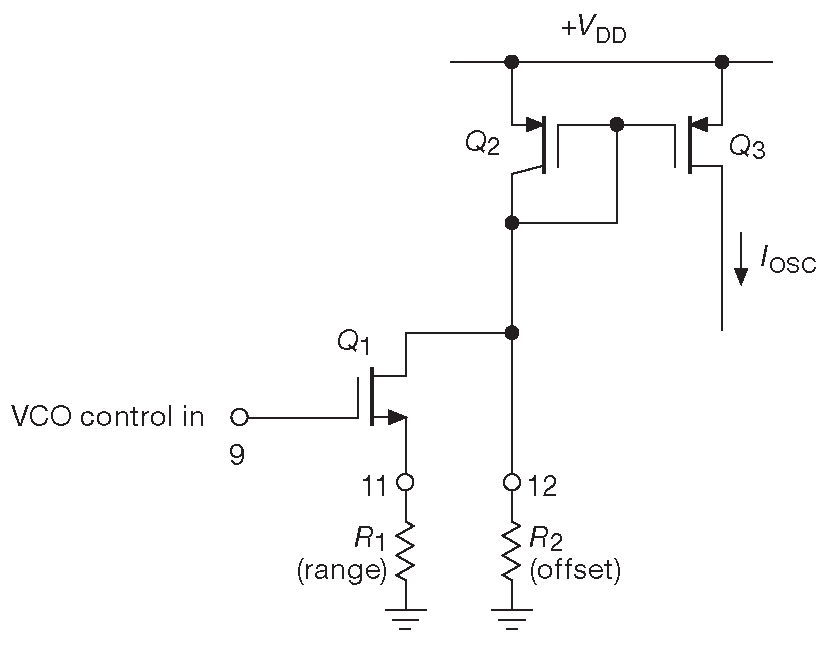

Обязательным компонентом PLL является генератор, управляемый напряжением ( VCO ) , чья частота управляется сигналом с фазового детектора. Такие устройства обсуждались в Части _7 ( §7.1.4.D и §7.1.5.D ) и очень скоро встретятся в примерах схем PLL. На данный момент будет достаточно простого RC генератора, управляемого напряжением на ’4046 и её преемниках ( рис. 13.94 ).

Рис. 13.94 RC генератор, управляемый напряжением и используемый в классической схеме PLL ’4046. Выходная частота примерно пропорциональна току управления \( I_{osc} \) , который заряжает внешний конденсатор \( C_1 \) попеременно через один или другой p-МОП ключ

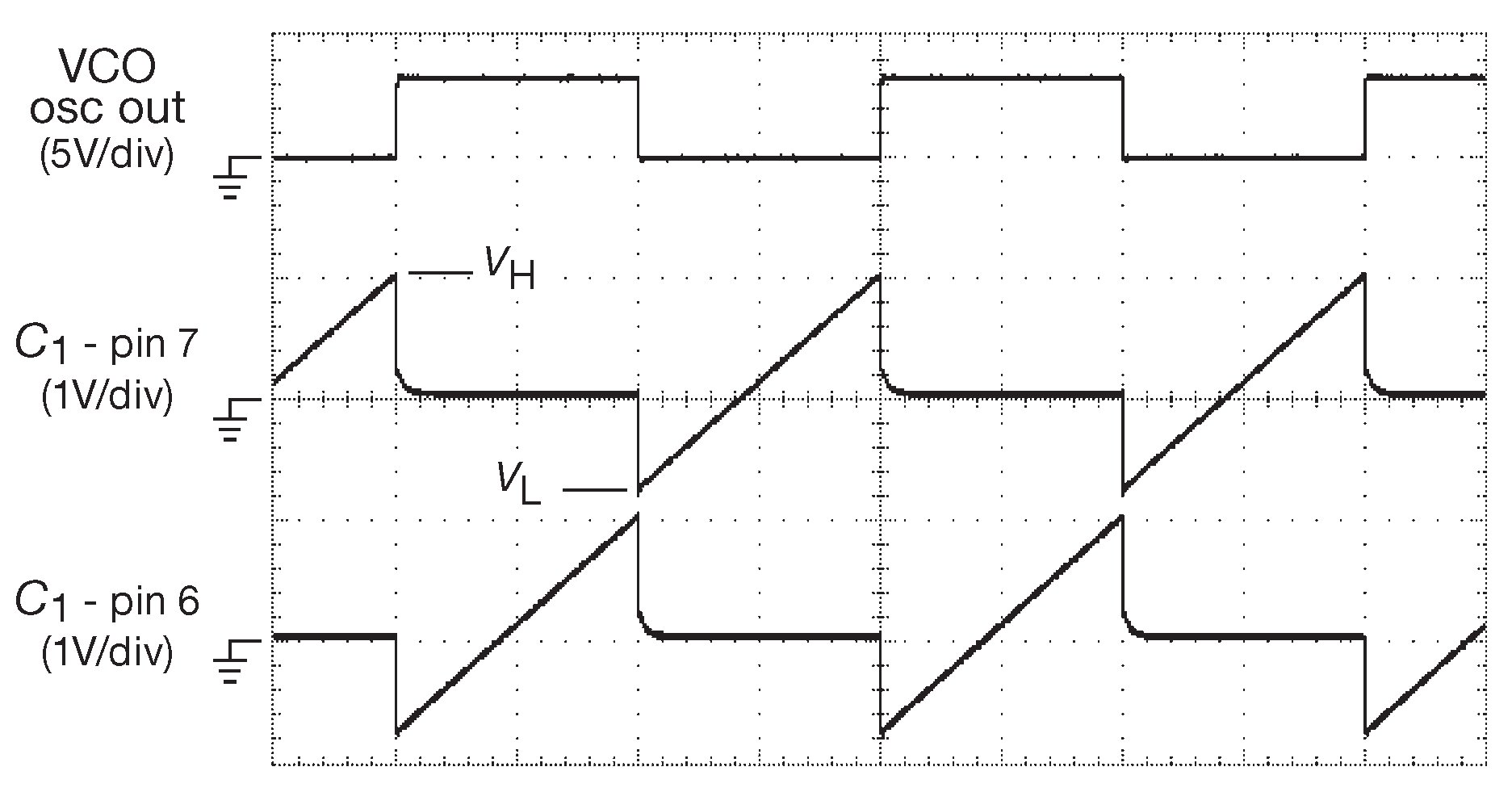

Работает схема просто. Выход триггера через n-МОП ключ удерживает один из выводов внешнего времязадающего конденсатора \( C_1 \) на уровне земли. Тем временем ток \( I_{osc} \) заряжает \( C_1 \) через p-МОП ключ другого плеча. Когда напряжение на конденсаторе превысит логический порог инвертора ( около 1.1V ), схема инвертирует потенциалы на выводах конденсатора. На рис. 13.95 показана временная диаграмма этого процесса для ’4046 при питании +3.3 V с \( C_1 \) =10 nF и \( I_{osc} \) =0.85 mA . Отметим, что каждый цикл начинается на уровне приблизительно –0.7 V ( прямом падении напряжения на ограничительном диоде ), когда положительно заряженная обкладка конденсатора закорачивается на землю.

Рис. 13.95 Формы сигналов в различных точках генератора 74HC4046 для \( V_{CC}\)=3.3 V . При питании 5V линейный подъём начинается с того же уровня, но заканчивается на 0.2 V выше. По горизонтали 10 μs/div

==960

В PLL часто требуется ограничить диапазон перестройки генератора, чтобы он работал в некоторой полосе с центром на желаемой частоте. Например, PLL в радиоприёмнике требует перестройки в диапазоне ±10 MHz с центральной частотой ∼100 MHz . Дальше встретится пример генератора с очень узким диапазоном перестройки ( до ±0.01% ) - управляемый напряжением кварцевый генератор . В ’4046 такое ограничение получить достаточно просто с помощью пары резисторов ( рис. 13.96 ). \(R_1\) отвечает за диапазон перестройки ( \( f_{max}-f_{min}\) ) , а \(R_2\) устанавливает минимальную частоту. В предложенной схеме \(Q_1\) работает как управляемая нагрузка для токового зеркала на p-МОП транзисторах, задающая зарядный ток \( I_{osc} \) .

Рис. 13.96 Задание начальной частоты и диапазона перестройки с помощью управляющего потенциала относительно земли для классической высоковольтовой схемы VCO CD4046. В 74HC4046 для управления токами через \(R_1\) и \(R_2\) используется ОУ

Хватит теории. Рассмотрим схемы PLL со встроенным генератором и без него. Для начала поиграем с новым товарищем - ’4046. Следует помнить, что PLL и их VCO не ограничиваются экземплярами, работающими на частотах в десятки мегагерц. На самом деле правильнее было бы говорить, что большинство таких схем работает в диапазоне сотен-тысяч мегагерц. На таких частотах времязадающие RC цепи уже не работают. Вместо них используют LC контуры с настройкой с помощью конденсатора, управляемого напряжением - варактора, или кольцевого генератора ( цепочки инверторов ), которые регулируются уровнем рабочего тока . Встречаются более экзотические техники: резонаторы на поверхностных акустических волнах ( ПАВ) [* в данном случае «акустические» означает неэлектрическую природу процесса: речь идёт о механических колебаниях на частотах, лежащих далеко за пределами слышимого диапазона ] и микроэлектромеханические системы ( МЕМС) . VCO не обязаны иметь линейную зависимость частоты от управляющего напряжения, но сильная нелинейность ведёт к изменению петлевого усиления с изменением частоты ( об этом ниже ), что плохо сказывается на устойчивости.

13.13.3 Конструкции PLL

13.13.3.A Замыкаем петлю управления

Фазовый детектор даёт сигнал ошибки сообразно с разницей фаз между опорным входом и сигналом с генератора. VCO позволяет управлять частотой с помощью напряжения. Задача выглядит тривиально: выбирается петлевое усиление и замыкается цепь обратной связи. Всё как в обычном операционном усилителе с обратной связью.

Но есть одно базовое различие. Ранее величина, подстраиваемая обратной связью, была тем самым сигналом ошибки на входе, который воздействовал на работу схемы, или как минимум была ему пропорциональна. Например, в усилителе напряжения измеряется сигнал на выходе и соответственно подстраивается сигнал на входе. Но в PLL имеется операция интегрирования: измеряется фаза, а изменяется частота. Фаза - это интеграл частоты. Другими словами, в цепи обратной связи появляется запаздывание по фазе на 90° .

Интегратор в цепи обратной связи имеет важное следствие: дополнительное запаздывание на 90° на частоте единичного усиления может вызвать генерацию. Простым решением будет исключение любых источников запаздывания фазы вблизи частоты единичного усиления. В конце концов, операционные усилители работают с таким сдвигом в большей части своего рабочего диапазона, и всё работает очень хорошо. Это один из подходов, который ведёт к схеме, носящей название «петля обратной связи первого порядка». Выглядит она как показанная ранее схема PLL с исключённым фильтром низких частот.

Такой метод находит применение, но не может работать как инерционное звено и сглаживать с помощью VCO шум и колебания управляющего сигнала. Кроме того, петля первого порядка не поддерживает фиксированного соотношения фаз между опорным сигналом и выходом VCO, потому что выход фазового детектора заводится непосредственно на генератор. Цепь «второго порядка» имеет в своём составе дополнительный ФНЧ ( как на предыдущих схемах ), который необходимо тщательно рассчитывать, чтобы не допустить появления неустойчивости. Такая схема приобретает «инерцию», сокращает «диапазон захвата» и удлиняет время захвата. Фазовый детектор типа II и цепь второго порядка гарантирует захват при нулевой разности фаз опорного сигнала и выхода VCO. Объяснения этому факту последуют чуть позднее. Петля второго рода используется повсеместно, потому что обычным требованием к PLL является отсутствие фазового шума и наличие эффекта «памяти» или инерции. Петля второго порядка позволяет иметь большое усиление на низких частотах, что позволяет получить высокую стабильность ( по аналогии с большим петлевым усилением в обычном усилителе с обратной связью ). Стоит познакомиться с предметом поближе, иллюстрируя идеи примерами разработок.

==961

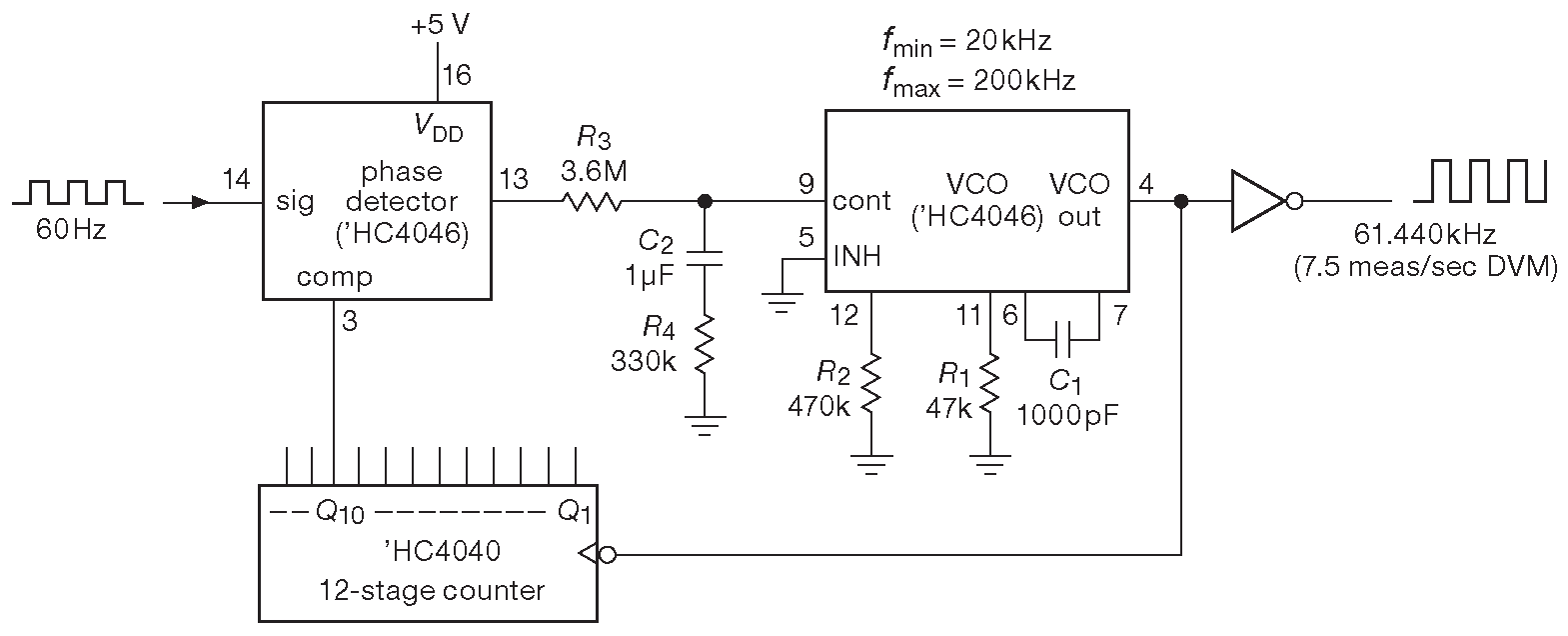

13.13.4 Пример разработки: умножитель частоты

Получение частоты, кратной входной, - одна из наиболее распространённых задач для PLL. Решается она синтезаторами частот, на выходе которых создаётся частота в n раз большая, чем стабильный низкочастотный сигнал ( например, 1 Hz ), причём n устанавливается цифровым способом. В результате получается универсальный источник сигнала, управляемый через цифровой интерфейс. В повседневной жизни PLL используется для получения тактовой частоты, кратной опорному источнику, уже имеющемуся в приборе. Предположим, например, что требуется тактовый сигнал 61440 Hz для АЦП двойного преобразования. Такая частота позволит выполнять 7.5 измерений в секунду, имея восходящую ветвь длительностью 4096 тактов ( напоминаем, что в двойном интегрировании сначала идёт зарядка за фиксированное время, а затем разрядка фиксированным током ) и длительность нисходящей - разрядка полной шкалы - до 4096 тактов. Уникальное достоинство PLL состоит в том, что 61440 Hz можно синхронизировать с частотой силовой сети 60 Hz ( 61440 = 60×1024 ), что позволит очень эффективно ослаблять сетевые 60-герцовые наводки, которые имеются на входе любого конвертора, см. тему в §13.8.4 .

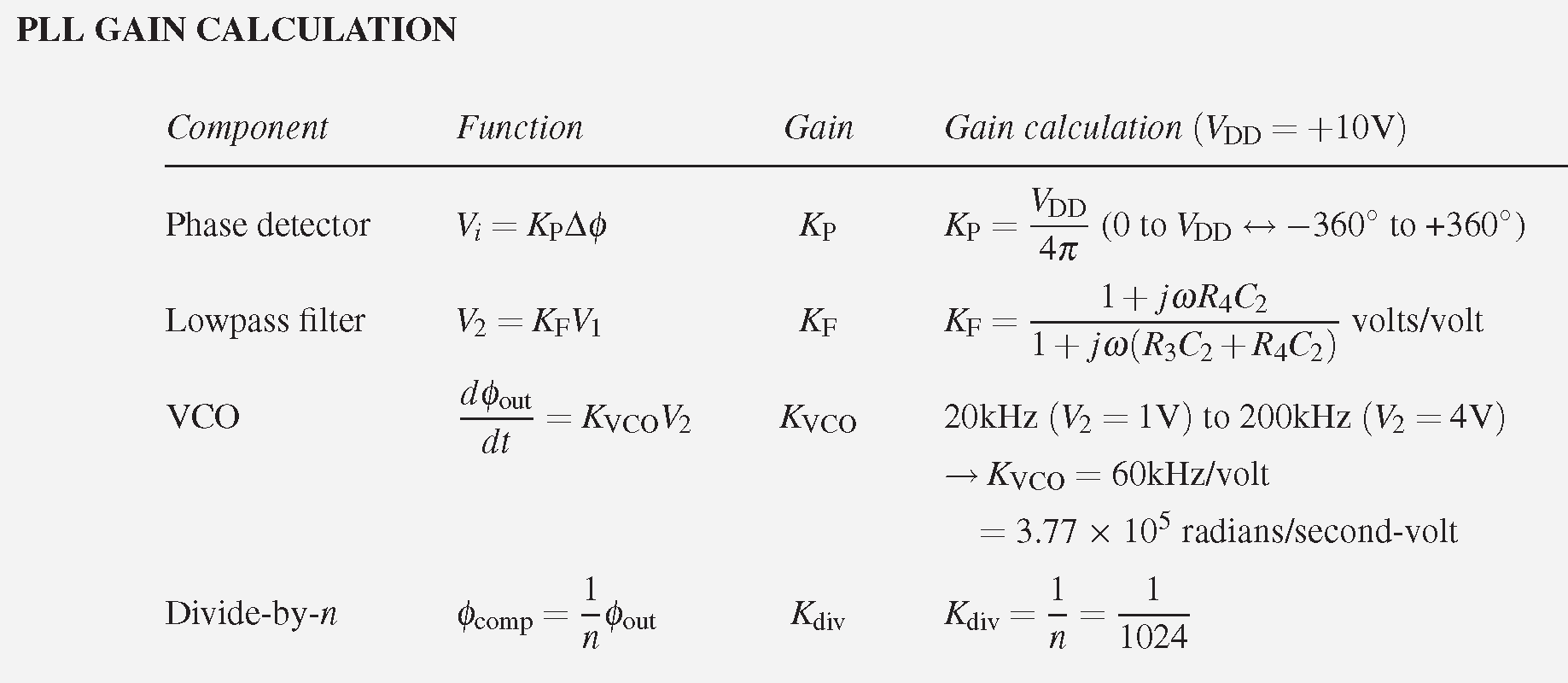

Начнём со стандартной схемы PLL с делителем «по-модулю-n» между выходом VCO и входом фазового детектора ( рис. 13.97 ). На схеме имеются индивидуальные обозначения коэффициентов усиления каждого элемента устройства. Они требуются для расчёта устойчивости схемы. Особо подчеркнём, что фазовый детектор преобразует фазу в напряжение, а VCO преобразует напряжение в производную фазы по времени ( частоту ). Т.е. VCO является интегратором, а нижняя часть блок-схемы имеет в качестве переменной фазу. Фиксированное изменение напряжения на входе VCO вызывает линейное изменение фазы на его выходе. ФНЧ и делитель «по-модулю-n» имеют безразмерные коэффициенты усиления.

Рис. 13.97 Блок-схема умножителя частоты

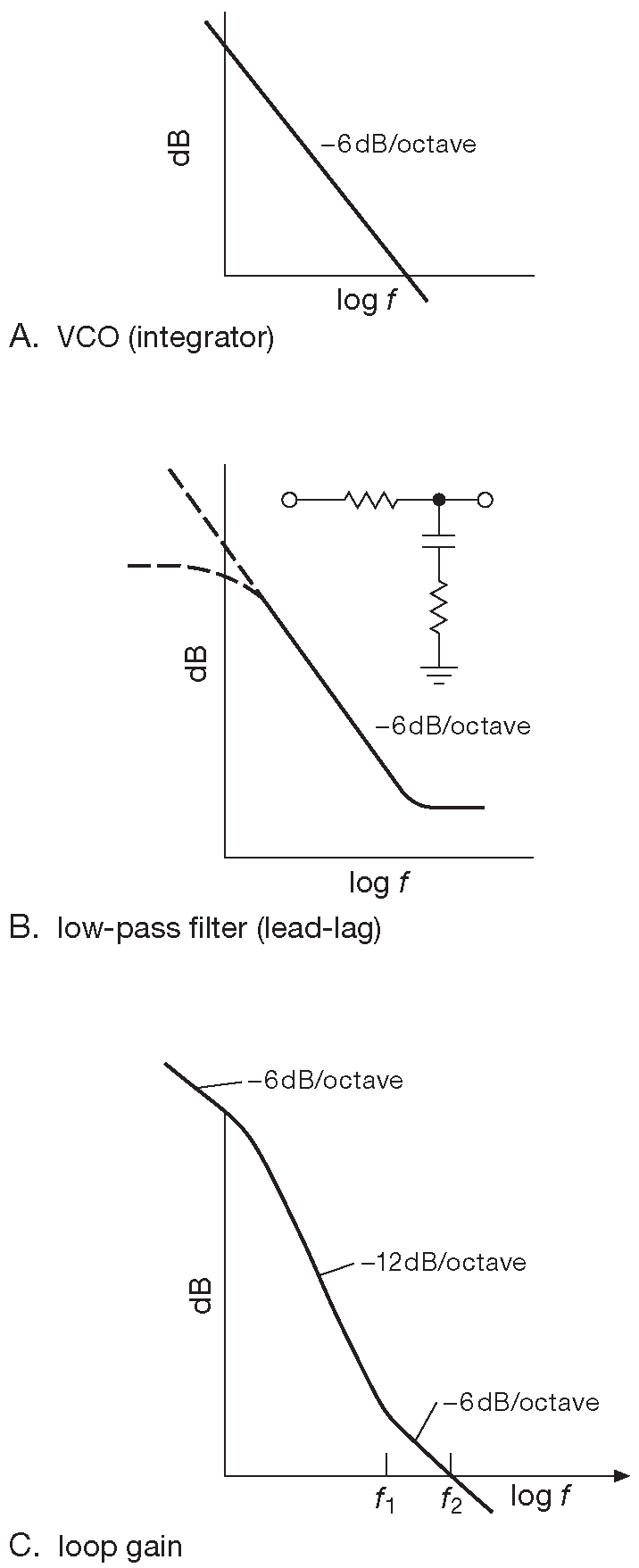

13.13.4.A Устойчивость и сдвиг фазы

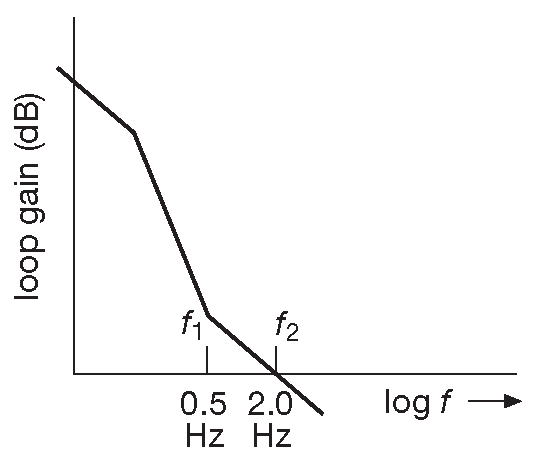

Основное условие стабильности PLL второго порядка показано на графике петлевого усиления - диаграмме Боде ( рис. 13.98 ). VCO представляет собой интегратор с передаточной характеристикой 1/\( f \) и запаздыванием фазы 90° ( т.е. отклик пропорционален 1/( \(jω\) ) , как в случае источника тока, нагруженного на конденсатор ). Чтобы иметь приличный запас по фазе ( разницу между 180° и сдвигом фазы в петле обратной связи на частоте единичного усиления ), в фильтре нижних частот есть дополнительный резистор последовательно с конденсатором, чтобы прекратить [* уменьшить ] спад на некоторой частоте ( такую точку называют «нулём» функции ). Комбинация двух таких характеристик имеет результатом показанный график усиления с обратной связью. До тех пор, пока петлевое усиление падает со скоростью 6 dB/octave в окрестности частоты единичного усиления, цепь обратной связи будет устойчива. Этим будет заниматься ФНЧ, если параметры схемы выбраны правильно ( методика такая же, как с коррекцией ОУ ). Процесс объясняется в следующем параграфе.

Рис. 13.98 Диаграммы Боде для схемы фазовой автоподстройки

==962

13.13.4.B Расчёт усиления в петле обратной связи

На рис. 13.99 показана схема синтезатора частоты 61440 kHz . Фазовый детектор и VCO входят в состав КМОП ИМС ’HC4046. Здесь использован фазовый детектор, чувствительный к фронту сигнала - тип II ( в ’HC4046 есть оба типа ). Выходной сигнал идёт с пары КМОП транзисторов, выдающих сигнал полного размаха питания. Это настоящий выход с тремя состояниями. Он находится в обрыве всё время, когда не выдаёт импульс фазовой ошибки.

Рис 13.99 Использование PLL для синтеза частоты, кратной 60 Hz силовой сети. В качестве микросхемы фазовой автоподстройки используется CD74HC4046A фирмы TI

VCO позволяет установить граничные частоты, соответствующие управляющим уровням нуля и \( V_{DD}\) . Для этого используются \(R_1, R_2\) и \( C_1 \) ( см. схему 13.99 ). Исходные номиналы взяты в соответствии с рекомендациями в справочных данных, проверены ( и подправлены! ) в ходе наладки, см. замечания о «жизненных реалиях» в §13.13.4.E .

Замечание: ’4046 «знаменит» высокой требовательностью к стабильности питания, см. графики в паспортных данных. Все остальные действия особенностей не имеют.

После завершения выбора диапазона VCO требуется настройка фильтра нижних частот. Это критически важная задача. Авторы начали расписывать выражение для петлевого усиления как на врезки «Расчёт усиления PLL», разбирая каждый компонент ( рис. 13.97 ). Особо доставила необходимость учёта единиц изменения: здесь важно не путать \( f \) и \(ω\) или ( что ещё хуже ) герцы и килогерцы. Выбор компонентов генератора, коэффициентов деления и уровней питания нужен для определения единственной итоговой величины - коэффициента усиления фильтра в цепи обратной связи KF . Для расчёта было выписано общее усиление с учётом того, что VCO - интегратор. \[ φ_{out}= \int V_2K_{VCO}dt. \]

Петлевое усиление в итоге выглядит так: \[ \begin{align*} Loop\text_gain &=K_PK_F\frac{K_{VCO}}{jω}K_{div}= \\ &=0.40×\frac{1+jωR_4C_2}{1+jω( R_3C_2+R_4C_2 )}×\frac{3.77×10\space^5}{jω}×\frac{1}{1024}. \end{align*} \]

Теперь надо выбрать частоту, на которой усиление падает до единицы. Основная мысль: частоту единичного усиления надо выбирать достаточно высокой, чтобы схема могла отслеживать изменения частоты в интересующем диапазоне, но достаточно низкой, чтобы обеспечивать сглаживание скачков частоты и шума. Например, PLL для демодуляции FM-сигнала или декодирования тональных посылок должна быстро реагировать на изменения. В частности для FM-сигнала полоса пропускания петли автоподстройки должна соответствовать полосе входного сигнала и реагировать на максимальную частоту модуляции. При декодировании тональных посылок время реакции на изменение частоты должно быть меньше, чем продолжительность тона. С другой стороны, схема, предназначенная для умножения стабильной и медленно меняющейся опорной частоты, должна иметь низкую частоту единичного усиления, потому что при этом снижается фазовый шум выходного сигнала, а схема умножения становится нечувствительной к помехам и шуму опорной частоты. Становится трудно обнаружить даже кратковременное пропадание опорного сигнала, потому что конденсатор фильтра продолжает сохранять управляющих уровень и VCO продолжает работу.

==963

В примере для \( f_2 \) выбрано 2 Hz или 12.6 радиан в секунду. Это гораздо ниже, чем опорный сигнал, так как резких изменений частоты сети, больших, чем указанная величина, не ожидается ( сетевая частота создаётся огромными генераторами с чудовищной инерцией ). Эмпирическое правило: точка перегиба характеристики ФНЧ ( его «нуль» ) должна иметь 3-, 5-кратный запас по частоте, чтобы иметь достаточный запас по фазе. Не следует забывать, что в простой RC цепи фаза сдвигается на 90° при изменении частоты от 0.1\( f_{3dB} \) до 10\( f_{3dB} \) ( на –3 dB находится «полюс» ), причём на самой частоте «-3dB» сдвиг составляет 45° . В примере частота «нуля» ( \( f_1\) ) составит 0.5 Hz или 3.1 радиан/сек ( рис. 13.100 ). Точка перегиба \( f_1\) определяется цепью \(R_4C_2\) . Постоянная времени \( R_4C_2=1/( 2πf_1 ) \) . Берём ориентировочные цифры: \( C_2\) =1 μF , \(R_4\) =330 Ω . Всё, что остаётся, выбрать \(R_3\) так, чтобы усиление на частоте \( f_2 \) было равно 1 . В данном случае \(R_3\) =3.6 MΩ .

Рис. 13.100 PLL второго порядка будет устойчива, если вблизи частоты единичного усиления спад характеристики будет -6 dB/octave

Упражнение 13.7

Покажите, что такой выбор компонентов схемы и в самом деле даёт G =1 на частоте \( f_2 \) =2.0 Hz .

Иногда получившиеся цифры не попадают в стандартные ряды номиналов, и их приходится подгонять или слегка сдвигать частоту единичного усиления. В случае КМОП микросхем фазовой автоподстройки и сами цифры, и их возможный диапазон вполне приемлемы, потому что управляющий вход VCO имеет типичное входное сопротивление \(10\space^{12}\) Ω . Для генераторов с низким входным импедансом может потребоваться внешний буферный ОУ.

В примере использован фазовый детектор, чувствительный к фронту ( тип II ), потому что с ним упрощается конструкция фильтра в обратной связи. В практической конструкции PLL для сетевой частоты такой выбор, вероятно, не лучшее решение, потому что в силовом переменном напряжении слишком много шума и мусора. Помехи в опорной частоте вызывают ложные срабатывания фазового детектора типа II и заставляют разработчика помучиться. Правильная конструкция аналоговых входных цепей ( триггер Шмитта с ФНЧ на входе ) позволяет детектору типа II работать должным образом. Если это не так, то придётся использовать «ИСКЛЮЧАЮЩЕЕ-ИЛИ» ( тип I ).

13.13.4.C Путь проб и ошибок

Для некоторых граждан искусство схемотехники заключается в непрерывной возне с номиналами компонентов фильтра до тех пор, пока устройство не «заработает». Если читатель относится к этой социальной группе, авторы рекомендуют ему пересмотреть своё отношение к жизни 119 . Похоже, плохая репутация фазовой автоподстройки проистекает по большей части из того, что слишком много людей выбирает указанный выше подход. Именно для них здесь приведены подробные расчёты элементов схемы. Так или иначе, авторы не могут отказать страждущим в нескольких полезных приёмах «обработки изделия напильником»: \(R_3C_2\) устанавливают время сглаживания ( отклика ) петли, а \(R_4R_3\) определяют демпфирование, т.е. величину выброса при резком изменении частоты. Начинать следует с соотношения \(R_4\) > (0.2–0.3 )\(R_3\) [* и затем снижать номинал \(R_4\) ] .

==964

13.13.4.D Связь между демпфированием в петле фазовой автоподстройки и джиттером

Побочным эффектом ненулевого «демпфирующего» резистора \(R_4\) является появление на выходе PLL джиттера. Проще всего обратить внимание на то, что даже на высоких частотах петлевой фильтр позволяет части исходного сигнала ( в пропорции \(R_4/( R_3+R_4 )\) ) с фазового детектора добраться до VCO. Для типичных отношений \(R_3∼\)10\(R_4\) джиттер будет вполне заметен. Обычным решением проблемы является небольшой конденсатор ( \(∼C_2\)/20 ) со входа VCO на землю. Его желательно располагать возможно ближе к микросхеме, чтобы отсечь заодно ВЧ наводки и шум.

13.13.4.E Рабочая схема фазовой автоподстройки

До настоящего момента разработка шла, исходя из уверенности, что документация по выбранной микросхеме ( популярный элемент ’HC4046 ) вполне надёжна. Данная уверенность, оказывается, не вполне обоснована. Чтобы слегка расцветить скучный список предупреждений, авторы приведут здесь историю ( её короткую версию ) выбора компонентов для схемы 13.99 .

Для центральной частоты 61 kHz требовался трёхкратный запас по области безопасной работы, поэтому были взяты значения \( f_{min} \) =20 kHz [* \( f \)/3 ] и \( f_{max} \) =200 kHz [* 3\( f \) ] . Была выбрана микросхема TI CD74HC4046A, потому что она повторяла проверенную временем оригинальную конструкцию фирмы RCA. Согласно графикам в справочных данных номинал \( C_1 \) получался равным 1000 pF . Подошёл момент выбора номиналов времязадающих резисторов \(R_1\) и \(R_2\) . Один из авторов начал с \(R_1\) . Номиналы, выбранные по соответствующим номограммам, получались \(R_1\) =30 kΩ и \(R_2\) =300 kΩ . Пришлось подправить схему. В то же самое время другой автор проделал ту же работу, но в обратном порядке, начиная с \(R_2\) , как рекомендовали без каких-либо пояснений два производителя микросхем. Результат - 40 kΩ и 410 kΩ . Разница настораживала. Была и другая несообразность: один график в справочных данных TI давал для \( C_1 \) =1000 pF и \(R_2\) =220 kΩ частоту \( f_{osc} \) =400 kHz (тип.), а по рис. 27 из тех же данных получалось ближе к 33 kHz . Короче, пришлось идти в лабораторию и уточнять цифры. Для заданного диапазона частот вышло 45 kΩ и 482 kΩ . Выбранные по справочным данным значения работали, но отличались от целевых показателей в 1.5 раза [* вероятно, речь идёт о паре 30 k + 300 k ] , отъедая половину запаса по частоте 120 .

Что из этого всего следует? А то, что каждый производитель клона ’4046 использует собственную схему для VCO 121 . Кроме того, характеристика управления VCO должна быть линейной и предсказуемой, а на деле зависимость непонятная, её параметры меняются с изменением управляющего тока, напряжения питания и рабочей частоты VCO. Ситуация усугубляется на частотах выше 10 MHz . Вывести аналитические соотношения возможно ( ##AN1410 фирмы ON Semi ), но рекомендуемым методом остаётся выбор номиналов времязадающих компонентов ( \(R_1, R_2\) и \( C_1 \) ) по номограммам из справочных данных, после чего разработчику в обязательном порядке предписывается подстраивать их в ходе макетирования, прежде чем отдавать схему в производство.

Столь большие различия и отсутствие какой-либо вызывающей доверие предсказуемости вынуждает дать несколько советов:

- необходимо выбрать какого-то одного производителя микросхем для серийной продукции и не разрешать никакие замены;

- надо задавать широкие границы области работы \( f_{min} \) и \( f_{max} \) , подобно трёхкратному запасу схемы 13.99 ;

- исходные номиналы на схеме необходимо заменить реальными цифрами, полученными в ходе настройки готового изделия.

Правило _1 применимо ко всем аналоговым функциям, встроенным в цифровые ИМС и в устройства смешанных сигналов, например, фазовые компараторы, генераторы, VCO, миксеры, триггеры Шмитта, одновибраторы и компараторы.

13.13.5 Захват и синхронизация в PLL

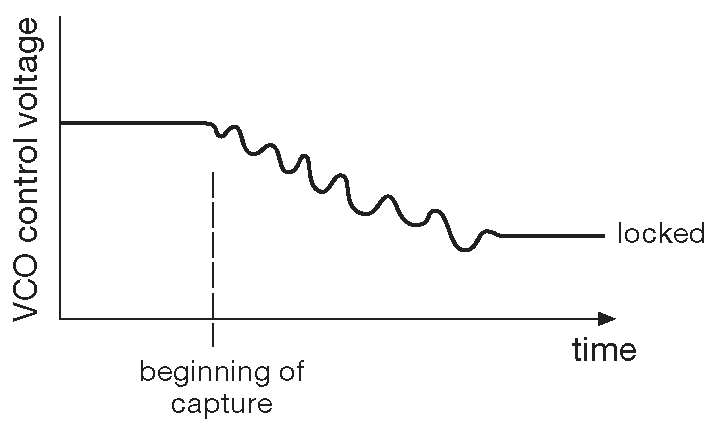

После того, как схема PLL вошла в синхронизацию, она будет оставаться в таком состоянии, пока входная частота не выйдет за рабочие пределы цепи автоподстройки или не начнёт меняться со скоростью большей, чем позволяет отслеживать рабочая полоса цепи обратной связи. Интереснее было бы узнать, на какой частоте произойдёт захват в первом случае. В конце концов, исходная разность частот на фазовом детекторе приведёт к периодическому гулянию выходного сигнала с периодом изменения частоты, равным разности выходного и опорного сигнала. После прохождения через ФНЧ эта разность превратится в колебания малой амплитуды вместо чистого постоянного уровня.

13.13.5.A Отслеживание изменений частоты

На самом деле ситуация несколько сложнее. Цепь фазовой автоподстройки первого порядка переходит в состояние синхронизации всегда, потому что входной сигнал не ослабляется при прохождении ФНЧ. Цепи второго порядка могут синхронизироваться, а могут этого и не делать. Результат зависит от типа фазового детектора и полосы пропускания ФНЧ. Кроме того, фазовый детектор типа I («ИСКЛЮЧАЮЩЕЕ-ИЛИ») имеет ограниченный диапазон захвата. Диапазон зависит от постоянной времени фильтра. Данное свойство может быть обращено в достоинство, если нужно, чтобы PLL проводило захват частоты в определённом диапазоне.

==965

Как происходит синхронизация в фазовом детекторе типа I вообще непонятно, поскольку, если на выходе фазового детектора постоянно имеется сигнал разностной частоты, частота VCO должна просто постоянно гулять взад-вперёд. Но если присмотреться к процессу, можно обнаружить следующую картину. В тот момент, когда сигнал ошибки подталкивает выход VCO ближе к опорной частоте, его собственная огибающая имеет более пологую форму и наоборот. Сигнал ошибки в результате становится асимметричным и меняется медленнее в той части цикла, в которой \( f_{VCO}\) ближе к \( f_{REF} \) . В результате среднее значение становится ненулевым, т.е. появляется постоянная составляющая, вынуждающая PLL войти в синхронизацию 122 . Если посмотреть внимательно на выходной сигнал VCO в момент изменения опорной частоты, можно заметить что-либо, напоминающее рис. 13.101 . Интересный момент возникает с финальным «выбегом» частоты перед синхронизацией. Даже когда VCO оказывается настроен на правильную частоту ( это видно по корректному уровню управляющего напряжения ), схема ещё не обязательно перешла в синхронизм, т.к. может быть некорректной фаза. Из-за этого и появляется выбег. Каждый переход к синхронизации индивидуален, все они отличаются друг от друга.

Рис. 13.101 Захват при изменении частоты

Для фазового детектора типа II ситуация существенно проще. Из-за того, что в выходном сигнале детектора присутствует постоянная составляющая, указывающая правильное направление изменения частоты ( второе название такого детектора - «фазо-частотный детектор» ), выход VCO быстро меняется в нужном направлении.

13.13.5.B Диапазон захвата и синхронизации

Для фазового детектора на «ИСКЛЮЧАЮЩЕМ-ИЛИ» ( тип I ) область захвата ограничивается параметрами ФНЧ и начинает сказываться, когда пилотный сигнал сильно уходит по частоте. Сигнал ошибки в этом случае будет ослабляться фильтром так сильно, что петля автоподстройки никогда не войдёт в синхронизацию. Очевидно, что по мере роста постоянной времени фильтра диапазон захвата становится всё уже. Такая же зависимость наблюдается при снижении петлевого усиления. Фазовый детектор, срабатывающий по фронту, таких проблем не имеет, потому что работает как настоящий интегратор для импульсов фазовой ошибки. У обоих типов диапазон синхронизации ограничен возможностями VCO при заданном управляющем напряжении.

13.13.5.C Время захвата

PLL с фазовым детектором типа II ( интегрирующим ) всегда входит в синхронизм ( предполагается, что у VCO достаточный диапазон перестройки ) за время, определяемое полосой пропускания петли автоподстройки.

Фазовый детектор типа I ( умножающий или смешивающий ) в паре с интегрирующим фильтром тоже синхронизируется, но, если рабочая полоса петли автоподстройки узкая, процесс может оказаться довольно долгим. Можно показать, что время синхронизации приблизительно равно \( (Δ f)^2/BW^3\) , где \(Δ f\) - исходная разница частот, а BW - ширина полосы автоподстройки. Таким образом, PLL с полосой 100 Hz , пилотным сигналом 100 kHz и исходной разницей частот 10% будет входить в синхронизм около минуты.

В схемах, рассчитанных на такие условия, иногда можно наблюдать интересный приём: при разомкнутой петле на управление VCO подаётся медленный пилообразный сигнал с полным диапазоном перестройки частоты, покуда не произойдёт синхронизация. Например, в рубидиевом стандарте частоты FRS фирмы Efratom слабый, но очень стабильный резонанс в атомах рубидия, возбуждаемых оптической накачкой, служит пилотным сигналом для высококачественного кварцевого генератора. 20-мегагерцовый термостатированный кварцевый генератор (XO ) подстраивается управляющим напряжением ( VCXO ) в диапазоне ±1 kHz . Роль инерционного звена выполняет петля автоподстройки за счёт фильтра-интегратора \(R\) =2 MΩ и \( C \) =1 μF .

Без посторонней помощи такая схема будет входить в синхронизацию вечно. В руководстве пользователя объясняется, как обходится это препятствие:

«Если сигнал «LOCK» отсутствует ...<начинается> медленное качание управляющего напряжения генератора со скоростью 250 mV в секунду. Качание продолжается до появления сигнала «LOCK». Сигнал «LOCK» запрещает работу схемы качания напряжения.. Это переводит интегратор под управление петли автоподстройки».

Фазовые детекторы типа II, благодаря наличию сигналов как величины рассогласования, так и его знака, в таких хитростях не нуждаются. Но на высоких частотах в системах связи фазо-частотные детекторы практически не используются, и подавляющее большинство составляют умножающие детекторы типа I.

==965

119 Возможно, цитата из технической заметки TI, относящаяся к методике настройки петлевого фильтра, придаст вам уверенности ( и, не исключено, что позволит продолжить еретические практики ):

«В любом случае следует рассматривать и возможность оптимизации методом подбора.»

( Optimizing by trial and error should be considered in all cases. ) <-

120 Были проведены дополнительные измерения как старых, так и новых образцов 74HC4046A фирм TI, NXP, ON Semi и Fairchild. Результаты показали хорошую повторяемость по производителям. Изменения нулевой частоты и рабочего диапазона для образцов с 15-летним разбросом даты производства отличались менее чем на 5% . Но при использовании номиналов со схемы 13.99 для микросхем разных производителей частоты менялись как +5%, +160% и -60% относительно значений для TI. <-

121 Например, TI подключает \(R_2\) к источнику \( V_{DD}\) –0.7 V , а ON Semi к \( V_{DD}\)/3 . Коэффициенты усиления токовых зеркал 7.5 и 25 соответственно. Похоже, 74HCT9046 фирмы NXP - самый лучший компонент типа ’4046 среди имеющихся, а графики в справочных данных NXP самые отчётливые. <-

122 Можно посмотреть на это с другой стороны. Сигнал ошибки слабо модулирует VCO на разностной частоте \(Δ f=|f_{REF}-f_{VCO}|\) . Эта модуляция формирует вокруг \( f_{VCO}\) симметричные боковые полосы шириной \(Δ f\) . В одной из этих полос в непосредственной бизости от \( f_{VCO}\) в выходном сигнале фазового детектора возникает постоянная составляющая, которую петлевой фильтр-интегратор вычленяет и возвращает систему в состояние равновесия - синхронизацию. <-