10.2 Цифровые интегральные схемы. КМОП и ТТЛ

==714

Цифровые логические функции реализованы в виде компонентов. Это могут быть микросхемы стандартной логики малой степени интеграции ( например, «74xx» ), или программируемая логика ( например, FPGA, см. §11.2.3 ), или специализированные заказные микросхемы ( ASIC или ASSP 21 , например, графический сопроцессор ). Данная книга предназначена в первую очередь для разработчиков схем ( как противоположности разработчикам кристаллов ) 22 и разработка самих ИМС здесь не обсуждается.

В производстве современных микросхем доминирует КМОП технология. Она по большей части заменила биполярную ( ТТЛ ) логику. КМОП быстрее, ориентирована на низкие напряжения питания и не так прожорлива. Подобно биполярной, КМОП логика делится на много семейств, которые предлагают стандартный набор функций, а все различия касаются в первую очередь быстродействия, напряжения питания и нагрузочной способности выходов. Есть довольно много производителей в значительной степени дублирующих друг друга ( «вторичные источники» ). Скажем, 2-входовой элемент «И-НЕ» популярной серии «LVC» (74LVC00) выпускают пять компаний, а ещё три почти такую же 74LCX00.

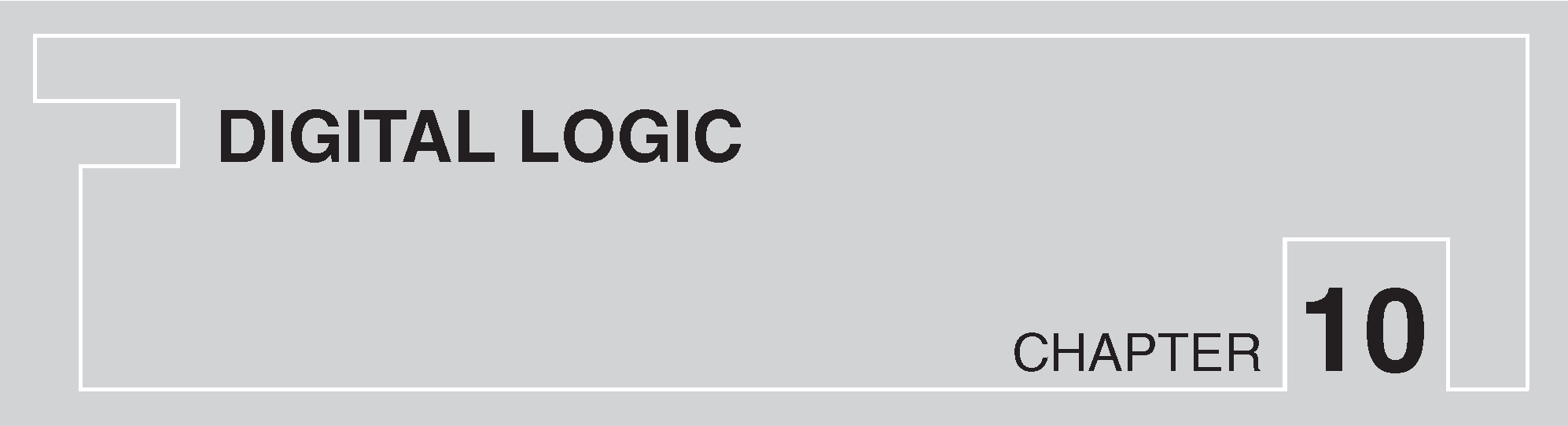

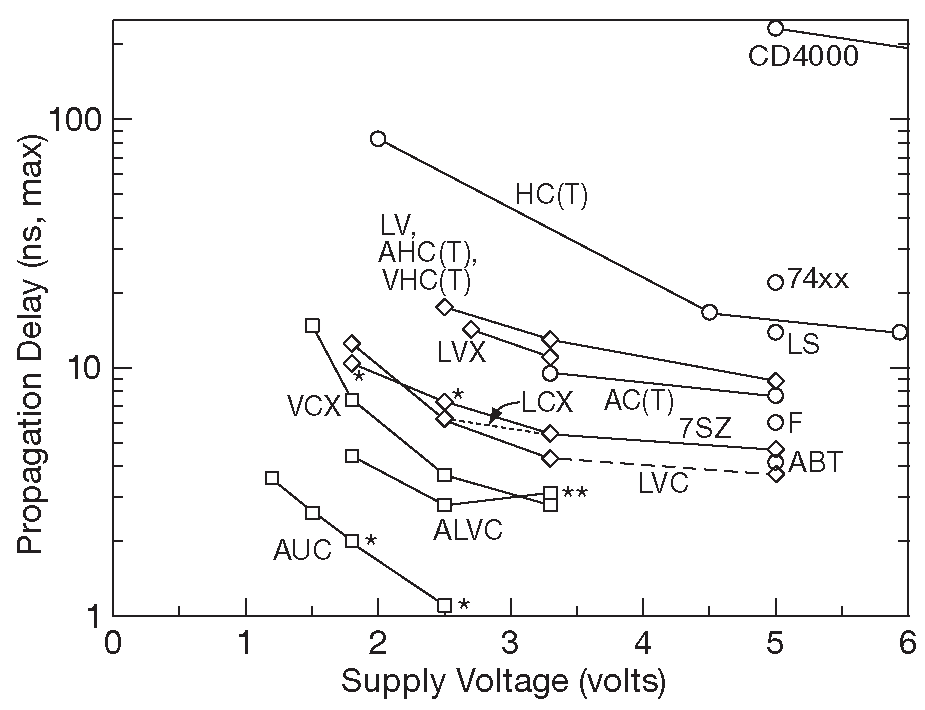

Выбор семейства будет обсуждаться в §10.2.2 и §12.1.1 , а сейчас будет полезно получить общее впечатление и взглянуть на рис. 10.22 , на котором виден жизненный цикл большей части важных логических семейств. Дни биполярной логики сочтены, исключая BiCMOS вариант - КМОП логику с биполярным выходом и некоторые очень специальные сегменты, например быстродействующую ЭСЛ.

Рис. 10.22 Жизненный цикл логических семейств на начало третьего тысячелетия. КМОП в фаворе, биполярные на закате. Здесь совмещены аналогичные иллюстрации от NXP, TI и некоторых других производителей

В данной части логика будет изучаться на примере старого семейства «HC(T)» и более свежего ( и быстрого ) «LVC/LVX» без углубления в некоторые детали ( см. §12.1.1 ). Первое интересно из-за широкой распространённости, огромного разнообразия доступных функций и наличия корпусов как для монтажа в отверстия ( DIP ), так и поверхностных вариантов ( SMT ). Второе семейство быстрее и оптимизировано под низкое напряжение питания, но выпускается только в SMT корпусах.

==715

10.2.1 Каталог стандартных вентилей

В табл. 10.3 приводится список логических элементов, входящих в стандартный набор цифровых функций. Каждый вентиль нарисован в нормальном виде ( с активными высокими входами ) и в варианте с активными низкими входами. Эти микросхемы упаковываются по несколько вентилей в стандартные 14-, 16-выводные корпуса ( по принципу «сколько влезет» ). Они же доступны в виде отдельных вентилей в компактных малоногих корпусах 23 . Как выглядят корпуса, можно посмотреть на рис. 10.23 . Как легко заметить, самый маленький чип легко помещается между двух соседних выводов самого большого.

Рис. 10.23 Некоторая коллекция корпусов цифровой логики. Все, кроме DIP-16 в левом верхнем углу, - поверхностные. Верхний ряд слева направо : DIP-16, SOIC-16, SSOP-16, TSSOP-16, QFN-16. Средний ряд : TQFP-48, SOIC-8, SSOP-8, SOT-23-8, US-8, WCSP-8 ( DSBGA-8 ). Нижний ряд ( два образца каждого вида, верхний - кверху брюхом ): SOT-23-6, SOT-23-5, SC-70, SOT-533, WCSP-5 ( DSBGA-5 )

Чтобы обозначить микросхему, надо составить её номенклатурный номер. Он начинается с цифр «74», далее следуют несколько букв, обозначающих семейство, например, «LVC» (низковольтовое КМОП). Потом цифры, указывающие нужную функцию, пусть будет «08» ( 2-входовой «И» ). Кроме того, будет полезно добавить суффикс, уточняющий корпус [*] и температурный диапазон, и, возможно, префикс «SN», чтобы назвать фирму-производителя. И вот уже у нас «74LVC08ADR» - счетверённый 2-входовой «И» серии «LVC» на катушке в количестве 2500 шт. в 14-выводном корпусе SOIC для температурного диапазона –40°C...+125°C производства Texas Instruments. Для простоты и чтобы не тратить понапрасну бумагу, все эти детали будут замещаться в названии простым апострофом при номере логической функции в виде «’08» для простого «2И-НЕ». Там, где это важно, будет добавляться код семейства: «’LVC08».

[*]

[* Только не так игриво.

Гляньте ещё раз на рис. 10.23 и подумайте: все эти корпуса ( кроме TQFP-48 и DIP-16 ) могут соответствовать частичному обозначению, скажем, «..HC08..». И, если вы по невнимательности закажете SOIC-14 вместо DIP-14, будет неприятно и неудобно, но вывернуться получится. Но, что делать, если наоборот SOIC вместо SOT-23? Суффиксы, обозначающие корпус, важны не менее чем код семейства и номер функции. А затем, написав, наконец, нужный номенклатурный номер, неплохо будет зайти на сайт производителя или дистрибьютора и проверить своё творение поиском, чтобы не сожалеть потом о бездарно потраченных деньгах. ]

10.2.1.A Универсальный вентиль

==716

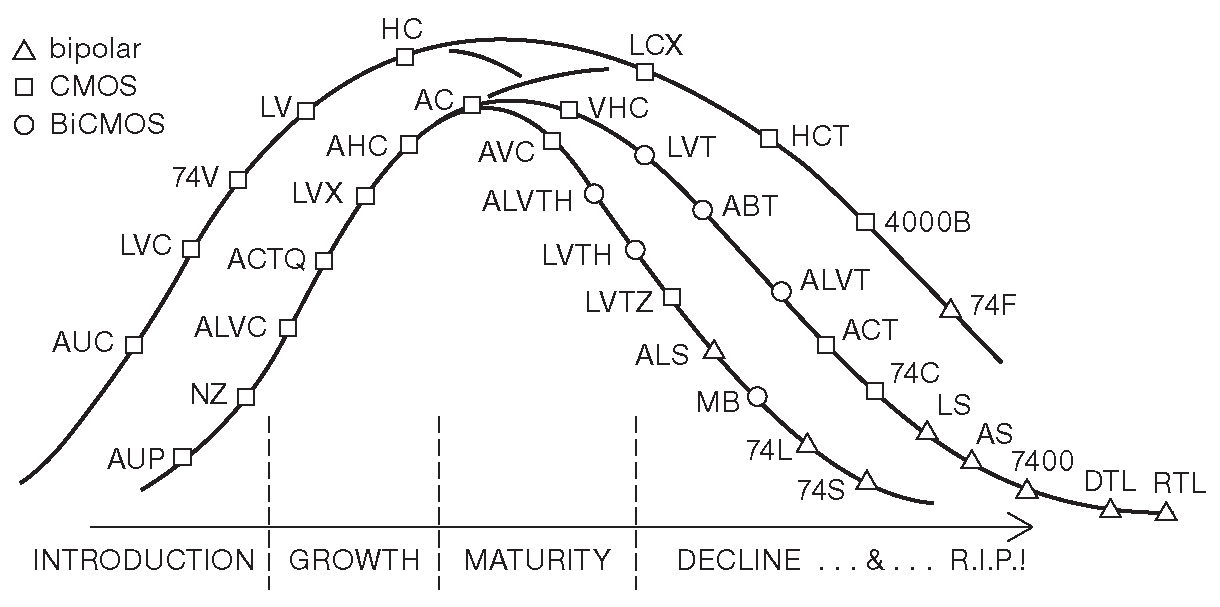

На рис. 10.24 показана очень красивая схема, которая влезает в 6-ногий корпус ( и зовётся ’1G97 ). Этот набор позволяет в зависимости от конфигурации входов выбрать одну из 9 функций: инвертор, неинвертирующий буфер, 2-входовой мультиплексор ( «MUX», см. §10.3.3.A ) и шесть вариантов 2-входовых вентилей ( «И», «ИЛИ», «И» с одним инверсным входом, «ИЛИ» с одним инверсным входом, «И-НЕ» с одним инверсным входом и «ИЛИ-НЕ» всё с тем же инверсным входом ). Второй столь же изменчивый родственник ’1G98 позволяет получить тот же набор функций, но с инверсией на выходе. Самый компактный корпус для этих микросхем имеет размер 1.4×0.9 mm и слишком мал для полного обозначения 24 . Дальше в этом направлении прошёл ’1G99. Добавление ещё двух выводов позволило получить:

- опциональную инверсию на выходе ( с помощью вентиля «ИСКЛЮЧАЮЩЕЕ-ИЛИ» ) и

- выход с «третьим состоянием» ( см. §10.2.4.A ).

Такая же пара ’1G57/’1G58 имеет на входах триггеры Шмитта.

Рис. 10.24 ИМС ’1G97 и ’1G98 «конфигурируемые многофункциональные элементы» позволяют выбрать одну из 9 функций. Показана схема ’1G97. ’1G98 выглядит так же, но имеет инверсный выход

Table 10.3 Standard Logic Gates in Popular Families3 Symbol Designatorb Inputs Outputc ALVC AHC(T) VHC(T) AC(T)(Q) HC(T) 7N, 7S, 7W CQ o o o LU _J LU LU O o T— Active-H Active-L inputs inputs AUC AUP LVC LCX LVX 5 LL cn _i AND ‘08 2 PP 1-4 1 4 T4 4 4 4 1-4 T4 4 4 4 4 12 4 T4^5 ‘11 3 PP - 13 - 1 3 - 3 - 3 3 3 3 3 1 3 - ‘21 4 PP - - - - - - 2 - 2 - 2 2 2 - 2 - NAND ‘00, ’37 2 PP 12 12 4 1-2-4 4 4 4 1-2-4 T4 4 4 4 4 12 4 T4^5 ‘03, ’38 2 OD - 12 - 12 4 12 - - ‘10 3 PP - 1 - 1 - - 3 - - - - - - 1 3 - ‘20 4 PP - - - - - - 2 - - 2 2 2 2 - 2 - ‘30 8 PP 1 1 1 - 1 - OR ‘32 2 PP 1-4 1 4 1234 4 4 4 1-4 T4 4 4 4 4 12 4 - ‘332 3 PP - 1 - 1 1 - - ‘802 4 PP - - - - - - - - - - 2 - - - 2 T4 NOR ‘02 2 PP 1-2-4 12 - 12 4 4 4 4 1-4 1-4 4 4 4 4 12 4 - ‘27 3 PP - 1 - 1 3 - 3 - 3 - 3 3 3 1 3 - ‘25 4 PP - - - - - - - - 2 - - - - - 2 1-4 INVERT (NOT) ‘04 PP CO 04 123 6 12 36 6 6 6 16 16 6 6 6 6 123 6 - ‘14 m ‘240 PP 3S 12 12 12 12 - 12 36 1 6 6 6 - - 16 6 - - - - 123 2 - - ‘05, ’06 OD CD 04 123 - 12 36 6 - 6 6 16 6 6 - 6 1 - - BUFFER ‘34 PP 26 12 - 1 - - - - - - - - - 1-2-3 6 - ‘125, ’126 ‘07, ’17 3S OD 1 12 1 12 6 1 12 6 6 6 - 16 1 16 1 - 6 6 6 12 123 6 - ‘241, ‘244, ‘541 3S 6 - 6 6 6 6 6 6 6 6 6 6 6 - - - XOR ‘86 ‘386 2 3 PP PP 12 - - 12 4 1 4 4 4 T4 T4 4 4 4 4 12 1 4 1-5 UNIVERSAL ‘57-8, ’97-8 3 PP - 1 - 1 1 - - ‘99 4 3S - 1 - 1 Notes: (a) available gates/pkg listed as mn etc.; e.g., a 2-input OR (‘32) in the AUC family is available with one or four gates in a package. (b) the digits signifying logic function follow the family designator (e.g., 2-input AND gates: 74LVC08, 74LVC1G 08); common to all families except HV CMOS (4000B) and ECL (100E, EL, EP). (c) PP=push-pull (active pull-up & pull-down); OD=open-drain; 3S=3-state.

==717

Упражнение 10.10

Покажите, как включить ’1G97, чтобы получить каждую из перечисленных функций.

10.2.2 Внутренняя схемотехника логических элементов

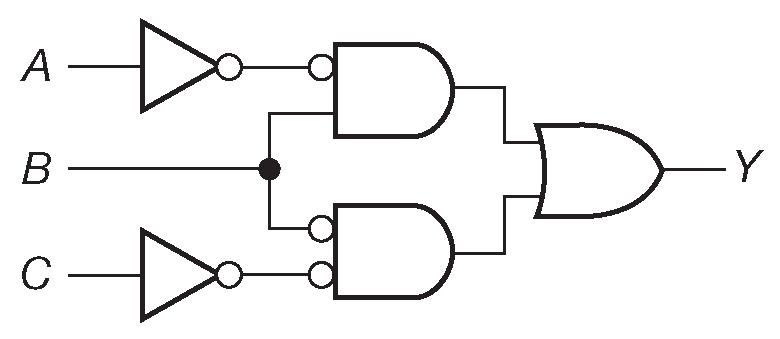

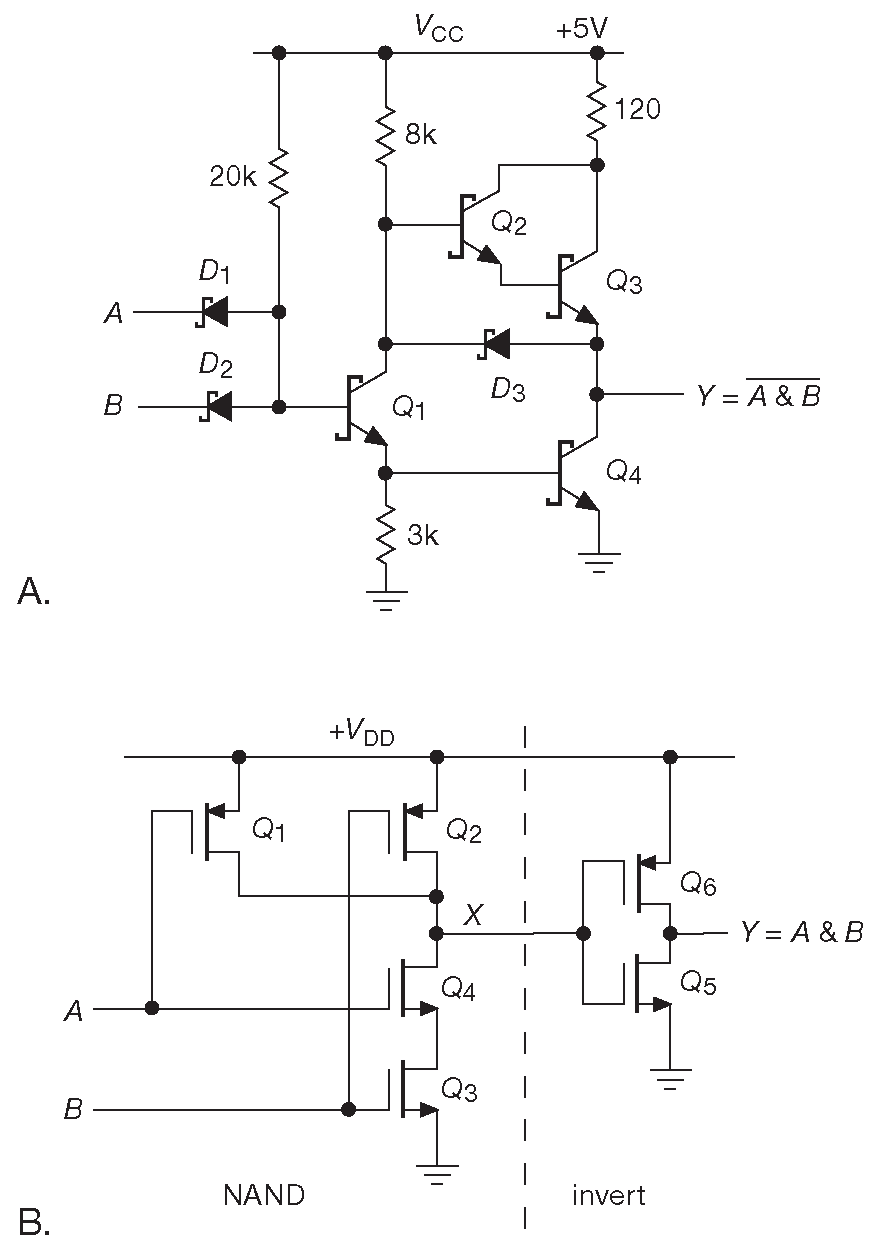

Хотя логическая функция одноимённых вентилей в различных семействах одна и та же, но прочие характеристики ( скорость, потребление, входной ток и т.д. ) сильно различаются. В общем случае надо соблюдать осторожность при смешивании различных семейств в одной схеме. Чтобы оценить различия взглянем на схему элемента «2И-НЕ» на рис. 10.25 .

Рис. 10.25 Вентили «И-НЕ»/«И», реализованные по двум технологиям. (A) Биполярный ТТЛ вентиль «И-НЕ» с псевдосимметричным выходным каскадом. (B) КМОП вентиль «И»

КМОП вентиль ( наиболее распространённый вариант ) собран на ключах из обогащённых МОП транзисторов обеих полярностей ( в биполярной версии - повторитель ). Открытый МОП транзистор выглядит как небольшое сопротивление \(R_{ON}\) на соответствующую шину питания. Чтобы перевести в проводящее состояние канал на последовательной паре \(Q_3Q_4\) и выключить параллельную пару \(Q_1Q_2\) , надо подать ВЫСОКИЙ уровень на оба входа. Общая выходная линия транзисторов ( точка «X» ) переходит при этом в НИЗКОЕ состояние, т.е. ведёт себя как элемент «И-НЕ». \(Q_5Q_6\) образуют обычный КМОП инвертор, доводя всю схему до конфигурации «И». По этому примеру понятно, как надо строить вентили «И», «И-НЕ», «ИЛИ» и «ИЛИ-НЕ» с любым числом входов.

Упражнение 10.11

Нарисуйте схему 3-входового элемента «ИЛИ».

Биполярные семейства теперь не пользуются былым успехом, потому что по всем параметрам перекрываются КМОП логикой 25 , но разобраться в устройстве ТТЛ элемента полезно 26 . Когда-то популярное семейство «LS» ( маломощное Шоттки ), см. рис. 10.25A базируется на диодно-резисторной схеме 10.12 , которая управляет инвертором на транзисторе. На выходе стоит псевдосимметричный повторитель. Если оба входа в ВЫСОКОМ состоянии, резистор 20kΩ удерживает \(Q_1\) во включённом состоянии, обеспечивая насыщение \(Q_4\), отсечку в \(Q_2Q_3\) и НИЗКИЙ уровень на выходе. Если хотя бы один вход в НИЗКОМ состоянии, \(Q_1\) вместе с \(Q_4\) выключены, а ВЫСОКИЙ уровень на выходе обеспечивается открытым повторителем \(Q_2Q_3\) . Отметим, что ВЫСОКИЙ выходной уровень с эмиттера пары Дарлингтона будет как минимум на два диода ниже уровня питания ( +5V ). Диоды и транзисторы Шоттки используются для увеличения быстродействия 27 .

Кроме того, и КМОП, и ТТЛ вентили имеют выходные каскады с активной подтяжкой к положительной шине питания, чем отличаются от примеров на дискретных компонентах (см. рис. 10.12 , 10.13 и 10.14 ).

==718

10.2.3 Характеристики ТТЛ и КМОП элементов

Этот параграф можно было бы назвать «аналоговые характеристики цифровых схем». Одна и та же логическая функция может быть реализована разными способами, и каждый вариант будет отличаться своими электрическими параметрами, даже если логическая функция будет одна. Итак.

- Напряжение питания

- КМОП допускает некоторый диапазон, ТТЛ требует +5V .

- Входной ток

- Статический ток КМОП входов исчезающе мал, ТТЛ потребляет довольно приличный ток.

- Входные уровни

- Различные семейства имеют отличающиеся пороги переключения и допустимые входные напряжения и не совместимы между собой.

- Выходы

- КМОП имеет RR выходы, ТТЛ не может дотянуться до положительной шины.

- Скорость и потребление

- КМОП имеет только динамический ток потребления, который пропорционален частоте переключения, ТТЛ имеет заметный ток покоя. Самые быстрые - низковольтные КМОП и биполярные ЭСЛ семейства.

А теперь все те же параметры подробно.

- Напряжение питания

- На рис. 10.26 отмечены уровни питания большинства интересных логических семейств. КМОП микросхемы имеют комфортные границы возможных напряжений питания. Например, «LVC» полностью специфицированы для диапазоне от +1.8 до +3.3 V , а большая часть семейства допускает работу с сигналами +5V 28 . В указанных пределах вентили переключаются быстрее возле верхней границы. ТТЛ работают только при напряжении +5 V±5% , ЭСЛ при –5.2 V ( иногда –4.5 V ) для NECL и при +5V для PECL.

Рис. 10.26 Скорость переключения как функция питания для популярных логических семейств. Максимальное указанное время задержки ( \(t_{pd}\) (max) ) для каждого семейства показано для стандартных напряжений питания. ( Грубо округляя, «типичные» цифры задержек лежат в диапазоне 35—75% от \(t_{pd}\) (max) ). См. рис. 12.3 )

- Входы. Токи

- КМОП микросхемы не имеют входного тока покоя, если не считать утечек, но их входная ёмкость порядка 4 pF требует перезарядки при смене уровня ( \(I=C(dV/dt)\) , поэтому, скажем, изменение уровня на входе величиной 2.5 V за 2.5 ns потребует обеспечить ∼5 mA тока ). В биполярной логике входной ток есть всегда. При НИЗКОМ уровне из входа вытекает порядка миллиампера ( 0.6 mA для серии F ), поэтому в дополнение к току перезарядки при переключении, придётся отбирать ток НИЗКОГО уровня 29 . В общем случае внутри семейства все выходы способны тянуть несколько выходов разом. Ситуация с напряжениями сложнее.

- Входы. Логические уровни

- В КМОП микросхемах порог переключения обычно лежит на половине питания ( но может иметь существенный разброс - от 1/3 до 2/3 питающего напряжения ). Такие цифры хорошо сочетаются с полным размахом питания на КМОП выходе. Но для совместимости с логическими уровнями старых ТТЛ микросхем ( их ВЫСОКИЙ уровень лежит сильно ниже положительного питания ) многие КМОП семейства имеют дублёров с «ТТЛ порогом» , которые отличаются добавочной буквой «T» в имени семейства: «HC»→«HCT», «VHC»→«VHCT». В таких семействах специфицируется максимальная граница НИЗКОГО уровня +0.8 V и минимальная граница ВЫСОКОГО +2.0 V ( см. рис. 10.2 и 12.6 ). Цифры взяты из спецификации на биполярную ТТЛ логику, где пороговый уровень примерно на два падения на p-n переходе выше уровня земли ( ∼1.3 V ) 30 .

- Входы. Допустимое входное напряжение

-

Единого международного стандарта на уровни питания микросхем нет, как и планов по его введению, поэтому в типичной цифровой схеме обычно есть несколько напряжений питания: +3.3, +5V и т.д. Отсюда вопрос: может ли семейство с напряжением питания X подключаться ко входу семейства с питанием Y, не совпадающим с X? Короткий ответ ( длинный смотрите в §12.1 ) таков: да, это возможно, если выполнены два условия. Во-первых, выходные уровни с питанием X должны соответствовать требованиям ко входным сигналам при питании Y, и, во-вторых, если Y ниже X, то входы должны допускать выход за уровни питания. Последнее требование называется «толерантностью по входу» и его требуется учитывать. Например, по рис. 10.2 видно, что старое семейство «HC(T)» последним свойством не обладает 31 , а новое «LVC» может принимать по входам сигналы до +5.5 V , независимо от уровня собственного питания ( в т.ч. и при отсутствии оного [* или, когда оно равно 0V : это разные ситуации ] ). «Толерантность по входу» необходима, если сигнальная линия пересекает границы областей с разными уровнями питания.

КМОП входы могут повреждаться статическими разрядами при неаккуратном обращении и в обязательном порядке должны подключаться к ВЫСОКОМУ или НИЗКОМУ уровню так, чтобы не мешать работе ( см. §10.8.3.B ).

- Выходы

- На КМОП выходе стоят комплементарные транзисторы, которые подтягивают вывод к земле или питанию, т.е. “rail-to-rail”. Выходной каскад ТТЛ в НИЗКОМ состоянии подтягивает вывод к земле через насыщающийся транзистор, а в ВЫСОКОМ состоянии подаёт на вывод положительный потенциал через повторитель на паре Дарлингтона ( два падения на диоде ниже питания ). Справочные данные дают больше информации и указывают типичные и наихудшие цифры выходных напряжений для некоторых типичных токов нагрузки 32 . В общем случае более быстрые серии имеют более мощные выходы ( «ALVC», «LVC», «LCX»; «F», «AS» ), чем медленные семейства ( «CD4000», «HC(T)», «LS» ).

==719

- Скорость и потребление

- Все КМОП серии стандартной логики не потребляют ток в статическом режиме 33 . Но их потребление линейно зависит от частоты работы, потому что на перезарядку внутренних и внешних емкостей нужен ток \(I=C(dV/dt)\) . КМОП логика, работающая на максимальной частоте переключения, может рассеивать даже больше мощности, чем биполярная ( см. рис. 10.27 ). Этот динамический ток 34 часто специфицируется в виде действующей «рассеивающей мощность ёмкости» \(C_{PD}\) , из которой можно посчитать рассеиваемую мощность микросхемы на заданной частоте без нагрузки \(P_{diss}=C_{PD}V^2f\) . ( В тактовом цикле два переключения, поэтому обычный множитель 1/2 сокращается ). Например, для 74LVC00 - счетверённого элемента «2И-НЕ» - указывается \(C_{PD}\) =19 pF на вентиль, из которой выводится 0.2 mW/MHz на вентиль ( при питании 3.3 V ). Таким образом, целиком одна такая микросхема на частоте 100 MHz рассеет 80 mW тепла только за счёт перезаряда внутренних емкостей, но есть, ведь, и внешние. Верхние границы рабочих частот современных КМОП ИМС лежат от 2 MHz ( для «CD4000» при питании 5V ) до примерно 100 MHz ( «AHCT»/«VHCT» при 5V ), 150 MHz ( «LVC»/«LCX» при 3.3 V ) и около 350 MHz ( «AUC» при 2.5 V ). В отличие от нулевого статического тока КМОП схем, биполярная логика потребляет заметный ток в состоянии покоя. Быстрые серии больше ( «AS», «F», «ABT» ). Максимальные скорости переключения лежат от 25 MHz ( «LS» ) и до 100 MHz ( «AS» и «F» ).

Рис. 10.27 Рассеиваемая мощность для ненагруженных схем как функция от частоты переключения для некоторых биполярных и КМОП серий. Обратите внимание на катастрофический квадратичный рост рассеиваемой мощности при увеличении уровня питания. См. также рис. 12.2

На рис. 10.26 нарисован график зависимости времени задержки вентиля стандартных логических семейств для наихудшего случая \(t_{pd}\) (max) . Он повторяется в сопровождении дополнительных пояснений на рис. 12.3 .

В обычной задаче отличные параметры КМОП логики - нулевое потребление в статике, RR выход, симметричная нагрузочная ( токовая ) характеристика выхода и высокая скорость делают её естественным выбором. Помимо всего прочего серии «LVC» и «7SZ» 35 приятно выделяются 5V-совместимыми входами и удобными диапазонами питания ( 1.8—3.3 V «LVC» 36 и 1.5—5V «7SZ» ). Для работы при 5V хорошо подходят «AHC(T)», «VHC(T)» и «LV». Их входы совместимы с 5V-логикой независимо от напряжения питания ( оно может лежать в диапазоне 2.5—5V ). Эти ИМС выпускаются только в корпусах для поверхностного монтажа. Если для макетирования нужен DIP, используйте «HC(T)» или «AC(T)».

==720

В экзотических случаях может потребоваться «CD4000B», имеющая диапазон питания 3...15 V , но она медленная . Для высоких скоростей подойдёт быстрая ЭСЛ ( более 1 GHz ) и гибридная серия «ABT» ( выходной ток до 64mA , чтобы раскачивать шины данных ).

Внутри одного семейства входы и выходы можно соединять, не задумываясь о порогах, входных токах и т.п. вещах. Скажем, в биполярных ТТЛ сериях каждый выход может быть нагружен 10 входами ( официальное название этого параметра «коэффициент разветвления» , у ТТЛ он равен 10 ), т.е. каких-либо дополнительных усилий по обеспечению совместимости прикладывать не надо. В Части 12 рассматриваются проблемы передачи сигналов между различными логическими семействами и особенности диалога с внешним миром.

10.2.4 Схемы с третьим состоянием и открытым коллектором

В КМОП и ТТЛ схемах вентили имеют активные выходные каскады: вывод удерживается в НИЗКОМ или ВЫСОКОМ состоянии включённым транзистором. Практически вся цифровая логика использует тот или иной вид схемы с активной нагрузкой: либо симметричную ( КМОП ), либо псевдосимметричную ( ТТЛ ). Такая конструкция обеспечивает низкий импеданс в обоих состояниях, малое время переключения и повышенную помехоустойчивость, если сравнивать с одним транзистором с пассивной нагрузкой в виде коллекторного резистора. Кроме того, активная схема снижает рассеиваемую мощность.

Но есть несколько ситуаций, когда активная нагрузка не подходит. Рассмотрим такой пример. Некая компьютерная система состоит из нескольких функциональных узлов, обменивающихся данными друг с другом. Центральный процессорный узел ( CPU ), память и разная периферия нуждается иногда в каналах передачи для отправки и получения данных. Иметь отдельные каналы передачи для всех пар устройств было бы затруднительно ( это если вежливо ). Решением будет так называемая шина данных - один канал передачи, к которому имеют доступ все устройства. Решение напоминает «спаренную телефонную линию» ( ныне полностью исчезнувшую (?) 37 ), в которой только один аппарат мог говорить, а всем остальным оставалось только слушать. В шине данных есть специальный механизм, обеспечивающий выбор передающего устройства. В литературе он скрывается под названием шинный арбитр .

Для подключения к шине нельзя использовать вентили ( или иные схемы ) с активной подтяжкой к земле или питанию, потому что они не могут отключить свой выход от шины данных общего пользования и удерживают на линии постоянный НИЗКИЙ или ВЫСОКИЙ уровень. Требуются элементы с возможностью отключения выхода. Такие микросхемы существуют и представлены двумя вариантами: устройствами с третьим состоянием и с открытым коллектором .

10.2.4.A Логика с третьим состоянием

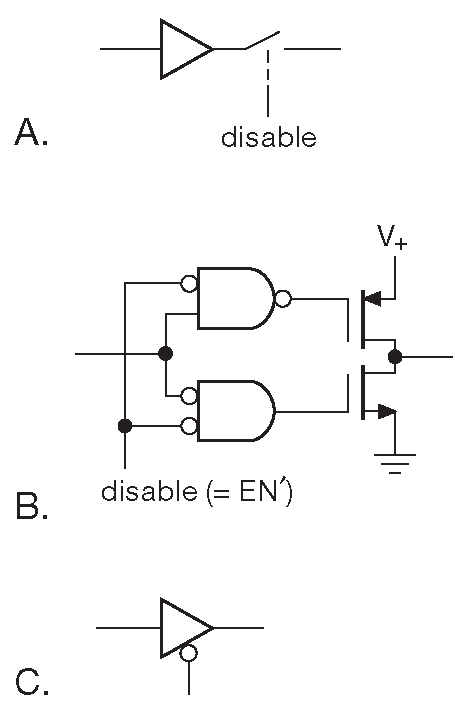

Элегантное решение проблемы предлагает логика с третьим состоянием TRI-STATE®. Название немного сбивает с толку. В схемном решении не используется третий логический уровень, а просто в обычном выходе добавлено состояние разрыва линии ( рис. 10.28 ). Отдельная линия разрешения независимо от прочих сигналов определяет, ведёт ли себя выход как обычный каскад с активной подтяжкой или переведён в «третье» состояние - обрыв. Третье состояние есть во многих цифровых микросхемах: в счётчиках, регистрах и вплоть до отдельных вентилей. В разрешённом состоянии такие ИМС ведут себя в точности как обычная логика, всегда имея на выходе либо ВЫСОКИЙ, либо НИЗКИЙ уровень. В запрещённом состоянии связь выхода вентиля с ногой микросхемы разрывается 38 , и другие устройства получают возможность управлять линией. Давайте разберём примеры.

Рис. 10.28 КМОП логика с третьим состоянием. Концепция (A), реализация (B) и схемный символ (C)

10.2.4.B Заглядывая вперёд: шины данных

==721

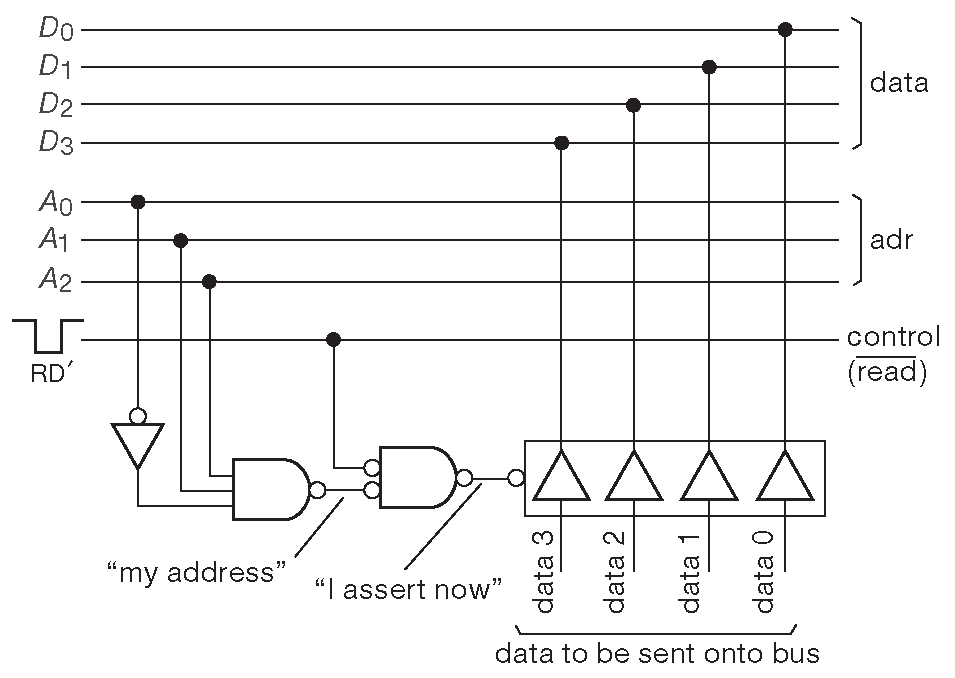

Драйверы с тремя состояниями широко используются при подключении к компьютерным шинам данных. Каждое устройство ( память, периферия ... ), которому требуется передать данные по шине, цепляется к ней через буферы с третьим состоянием ( или через более сложные микросхемы, называемые «регистрами» ). Схема организуется таким образом, чтобы в каждый момент времени только одно устройство находилось в режиме передачи, а все остальные были в третьем состоянии, т.е. с отключёнными от шины выходами. В обычной схеме выбранное устройство «узнаёт», что может работать с шиной, когда адрес, выставленный на адресных линиях, совпадает с его собственным, а управляющие сигналы разрешают передачу ( рис. 10.29 ). В предложенном случае передающее устройство имеет номер «6». Оно смотрит на адресные линии A0...A2 и выдаёт данные на шину D0...D3 , когда видит на адресных линиях состояние «LHH» И одновременно НИЗКИЙ уровень на линии «/READ». Такой протокол хорошо подходит простым системам. Что-либо подобное используется в большинстве микрокомпьютеров, о чём ещё будет речь в Части 14 . [* В изображениях и описаниях шин вычислительных систем принято располагать старшие биты слева, младшие - справа (для схемы 10.29 это A2...A0 и D3...D0 . В таком варианте информационные слова и адреса читаются «естественно», т.е. как цифры, каковыми они в большинстве случаев и являются. «HHL» превращается в «110» или «6» ].

Рис. 10.29 Шина данных, адресные и управляющие линии, декодирующая логика и буфер с третьим состоянием

Отметим, что для гарантированного предотвращения одновременной работы нескольких передатчиков на одну шину ( такая ситуация носит официальное название «столкновение на шине» ) требуется дополнительная логика. В предложенном примере всё будет работать правильно, пока у каждого передатчика будет уникальный адрес.

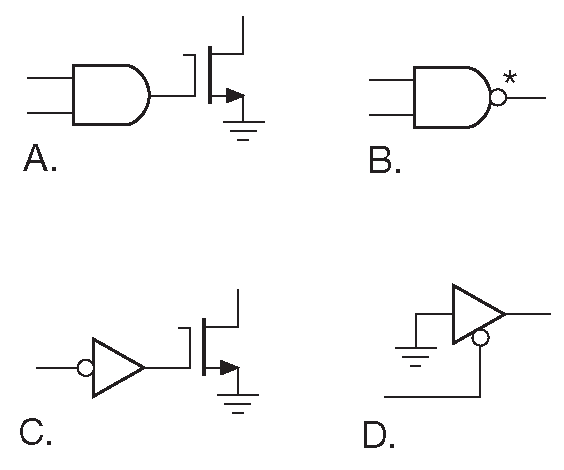

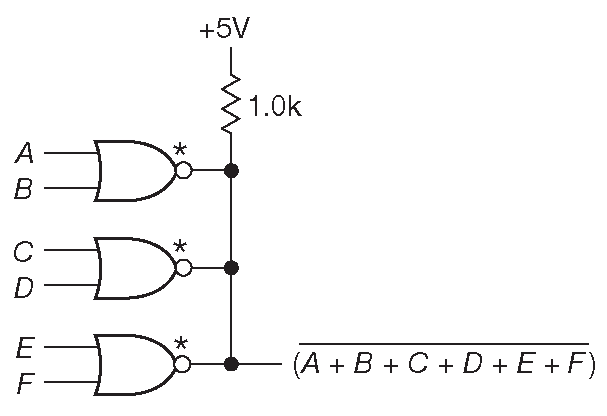

10.2.4.C Логика с открытым коллектором и открытым стоком

Предшественником микросхем с третьим состоянием была логика с «открытым коллектором». Она позволяла подключать выходы нескольких передатчиков к одной линии. В каскаде с открытым коллектором ( или открытым стоком ) активная подтяжка - верхний транзистор просто отсутствует ( рис. 10.30 ). Название «открытый коллектор» точно отражает положение вещей. При работе с такими микросхемами требуется ставить внешний подтягивающий резистор на положительный источник. Номинал не критичен: низкоомный увеличит скорости и помехоустойчивость вместе с рассеиваемой мощностью и нагрузкой на выход. Обычно используются номиналы от нескольких сотен до нескольких тысяч ом. Если хочется организовать общую шину на драйверах с открытым коллектором, то на схеме 10.29 каждый передатчик с третьим состоянием надо заменить 2-входовым элементом «И» для негативно-истинных сигналов с открытым коллектором. При этом НИЗКИЙ уровень будет разрешать передачу бита на шину. Каждая линия шины должна иметь один собственный резистор подтяжки к положительному питанию.

Рис. 10.30 Вентили с открытым коллектором. (A) «И-НЕ»; (B) схемный символ «И-НЕ»; (C) неинвертирующий буфер с открытым коллектором; (D) реализация на буфере с третьим состоянием

Недостатком открытого коллектора ( резистивной подтяжки ) является уменьшение скорости и помехоустойчивости по сравнению с активным выходом. Именно по этой причине все компьютерные шины используют драйверы с третьим состоянием. Но есть три ситуации, когда открытый коллектор имеет преимущество: работа на внешнюю нагрузку [* в т.ч. простое преобразование логических уровней см. рис. 12.9 ] , «ПРОВОДНОЕ-ИЛИ» и внешние шины. Рассмотрим их.

10.2.4.D Работа с внешней нагрузкой

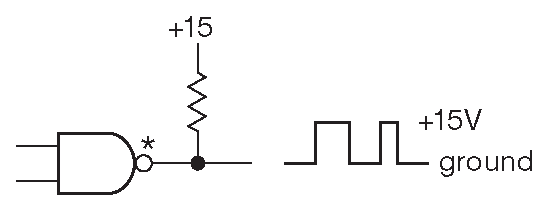

Логика с открытым коллектором легко сопрягается с внешней нагрузкой, висящей на положительном источнике. Так можно зажечь светодиод или включить реле, а можно просто получить логический сигнал для 15-вольтовой логики, повесив подтягивающий резистор на источник +15 V (рис. 10.31 ). Очень популярны ULN2003/4 - 7-канальные драйверы с открытым коллектором и защитными диодами ( для индуктивных нагрузок ). Они принимают логические уровни и допускают рабочее напряжение до 50 V и ток до 500mA [* только один канал за раз ] . Аналогичными возможностями обладает 75468/9, но напряжение повышено до 100 V , см. §12.4 .

Рис. 10.31 Логика с открытым коллектором в качестве преобразователя уровня

10.2.4.E «ПРОВОДНОЕ ИЛИ»

==722

Если соединить выходы элементов с открытым коллектором по схеме 10.32 , то результирующий сигнал будет называться «ПРОВОДНОЕ-ИЛИ». Он будет вести себя подобно элементу «ИЛИ» для НИЗКИХ уровней. С активными выходами такое соединение невозможно, потому что в общей точке будет столкновение сигналов [* короткое замыкание ] во всех ситуациях, когда состояние выходов различается. Тип логического элемента, подключённого к «ПРОВОДНОМУ-ИЛИ» не имеет значения. На общем выходе будет НИЗКИЙ уровень, если хотя бы один из объединённых выходов НИЗКИЙ. Такую конфигурацию иногда называют «ПРОВОДНОЕ-И», потому что он принимает ВЫСОКОЕ состояние, только когда все участники объединения имеют ВЫСОКИЙ уровень. Оба названия описывают одну функцию: это «ПРОВОДНОЕ-И» для активных высоких сигналов и «ПРОВОДНОЕ-ИЛИ» для активных низких. Данный вопрос станет понятнее после знакомства с теоремой ДеМоргана.

Рис. 10.32 «ПРОВОДНОЕ-ИЛИ»

«ПРОВОДНОЕ-ИЛИ» было довольно популярно на заре цифровой электроники, но сейчас используется редко. Есть два исключения.

- В ЭСЛ ( ECL ) элементах выходы представляют собой «открытый эмиттер» и могут спокойно объединяться.

- В компьютерных системах есть линии общего пользования ( наиболее известные - линии «прерывания» ), в задачи которых не входит передача данных. Они просто должны сообщать, что как минимум одно устройство требует обслуживания. «ПРОВОДНОЕ-ИЛИ» помогает легко расширить систему и исключает проблемы со столкновениями и дополнительной логикой.

10.2.4.F Внешние шины

Если скорость не важна, то на открытом коллекторе можно делать внешние шины общего пользования. Именно так был организован первый вариант периферийной шины SCSI. Так же выполнена шина IEEE-488, иногда называемая «интерфейсной шиной общего назначения» ( GPIB ) [* в отечественной практике это «канал общего пользования» - КОП ] . Шины данных рассматриваются в Части 14 .

==722

21 Стандартное изделие специального назначения - ASSP . <-

22 Иногда встречаются термины «разработка на уровне платы » и на « уровне кристалла ». <-

23 В качестве примера курьёзной инверсии могут выступать номенклатурные обозначения микросхем. Чем больше компонент, тем короче наименование и наоборот. Пример: счетверённый 2-входовой «И-НЕ» ( 4 вентиля в корпусе ) в 14-ногом корпусе имеет обозначение «SN74LVC00DR». Микросхема с той же функциональностью, но упакованная в виде одиночного вентиля в 5-выводной корпус, называется «SN74LVC1G00MDBVREP». Сочетание «1G» в середине наименования - указание на принадлежность к «мини-логике» - одновентильным компонентам в компактных корпусах. <-

24 Полное обозначение «SN74AUP1G97YZPR». <-

25 Исключая особо быстрые ЭСЛ и мощные гибридные “BiCMOS”. <-

26 Среди прочих соображений над всеми современными логическими семействами витает фамильное проклятие 74-ой серии – «входные ТТЛ уровни», устанавливающее для НИЗКОГО уровня величину ≤ 0.8 V , а для ВЫСОКОГО - ≥ 2.0 V . Для примера можно взглянуть на рис. 10.2 .) <-

27 Диоды Шоттки не накапливают носителей зарядов и поэтому не имеют задержки обратного восстановления (см. §9.5.3.B и §X9.6 [* или ##Linear AN ] ). Ограничители на диодах Шоттки не дают транзисторам переходить в режим насыщения, сильно замедляющий время выключения.) <-

28 Для большинства микросхем из семейства «LVC» справочные данные обозначают верхнюю границу «рекомендованного» напряжения питания на уровне +3.6 V , и только у нескольких представителей она повышена до +5.5 V , а параметры специфицированы для +5V . <-

29 Семейство ЭСЛ - странная штука. Логическими выходами служат «голые» эмиттеры, которые необходимо подтягивать к –2V в NECL или к +3V в PECL через резисторы 50 Ω . [* Изначальный ЭСЛ имел питание \(V_{CC}\) =0V и \(V_{EE}\) =–5.2 V , а резистор вешался на уровень \(V_{CC}\)—2V , т.е. на –2V . PECL - тот же ЭСЛ, но передвинутый в положительную область: \(V_{CC}\) =5V, \(V_{EE}\) =0V. Резистор, как и прежде, вешается на уровень \(V_{CC}\)—2V , но теперь это +3V . Обычно никто не заморачивался цифрами «–2V» и «50 Ω»: просто пересчитывали эмиттерные резисторы и вешали их на шину \(V_{EE}\) ] . <-

30 Этот кусочек исторического наследия простирает свою тень через весь цифровой мир. «Входные уровни ТТЛ» более всего подходят на роль признанного стандарта для любого устройства с цифровыми входами. <-

31 Точнее, входы не могут уходить более чем на 0.5 V за уровни питания или земли. <-

32 Для КМОП выходов обычно специфицируется пара симметричных токов для ВЫСОКОГО и НИЗКОГО уровня, например, ±8 mA . ТТЛ схемы имеют несимметричные выходы и указывают большой входной ток, но весьма скромный выходной ( например, +8 mA и –0.04mA ). Эти цифры очень важны, когда на выходе висит какой-нибудь необычный потребитель - светодиод или реле. Подключайте нагрузку так, чтобы логический выход потреблял ток, а второй конец нагрузки вешайте на положительный источник через ограничительный резистор, если требуется. <-

33 Большие интегральные КМОП схемы ( например, вентильные матрицы или микропроцессоры ), в противоположность стандартной логике, имеют ненулевой и часто весьма заметный ток покоя. <-

34 При зарядке и разрядке конденсатора от 0 до V на частоте \(f\) требуется средний ток \(I=fCV\) . <-

35 Серии «7SZ» и «17SZ» выпускаются только в малоногих корпусах. <-

36 Максимальный «рекомендованный» уровень питания для некоторых представителей «LVC» семейства составляет 5.5 V , а для остальных только 3.6 V . Тем не менее, хотя вторая часть и не предоставляет данных о работе при питании выше 3.6 V все «LVC» микросхемы позволяют поднимать питание до +5.5 V [* технология-то одна ] . <-

37 Но играл важную роль в фильме 1959 года “Pillow Talk”. <-

38 Mr. Lebowski в запрещённом состоянии. <-