11.2 Аппаратная часть

==765

Современные PLD дьявольски сложны и не собираются упрощаться в будущем. Старшие модели уже имеют миллиарды транзисторов ( и это число постоянно растёт ). Чтобы разобраться с ними всеми, надо пройти несколько шагов: классическая архитектура PAL ( 22V10 ), чуть более сложные PLA ( Xilinx CoolRunner-II ) и, наконец, сложные FPGA.

11.2.1 Самые простые PAL

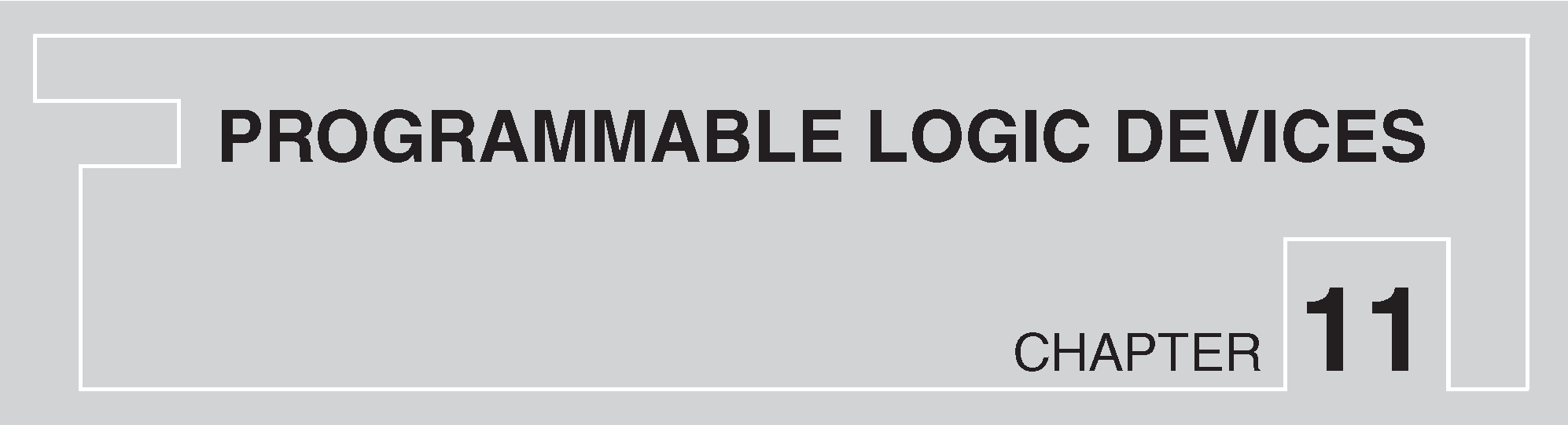

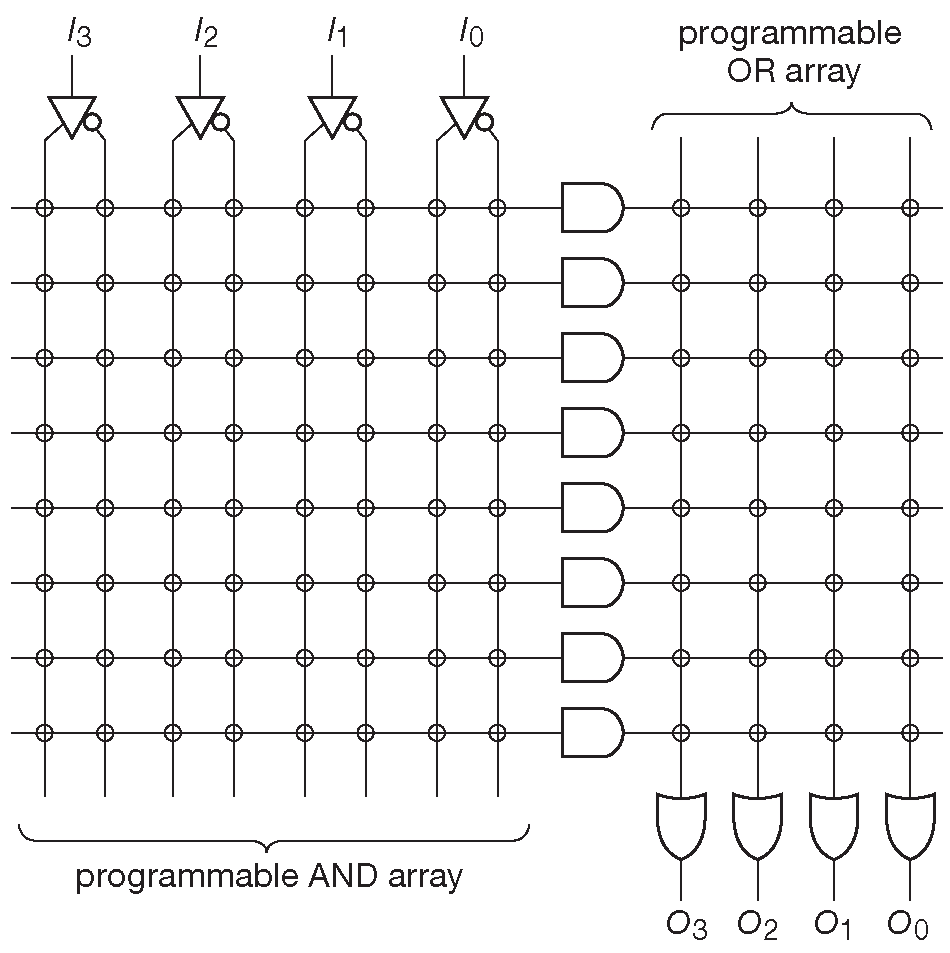

Простые PAL - хорошая исходная точка и хороший пример PLD. Классическая схема 22V10, где 10 означает число выходных макроячеек , а 22 - число сигнальных выводов всех видов ( исходно эти микросхемы упаковывали в 24-ногий корпус ). Внутренняя схема PAL включает программируемую матрицу межсоединений, где и входы, и линии обратной связи можно выборочно подключить к набору многовходовых вентилей «И». После «И» сигналы идут на элемент «ИЛИ», а уже его выход заводится в «выходную макроячейку», где может использоваться непосредственно ( комбинационный выход ) или защёлкиваться в D-триггере ( регистровый выход ). Идею иллюстрирует рис. 11.2 ( схема упрощена до 4 входных сигналов ). Каждый логический выход с элементов «ИЛИ» является результатом операции над выходами двух 8-входовых вентилей «И» и поступает на выходную макроячейку ( обратите внимание на то, как сворачиваются многочисленные параллельные сигналы на схеме 11.2A по сравнению с полной схемой 11.2B ).

Рис. 11.2 (A) В программируемом массиве логики ( PAL ) каждый доступный логический сигнал и его дополнение может подключаться к любым вентилям «И». Выходы нескольких «И» собираются на элементах «ИЛИ» и на пути к выходной линии проходят через макроячейку. (B) Каждый элемент «И» имеет множество входов, которые загромождают схему. Здесь показаны в сокращённой и полной форме

==766

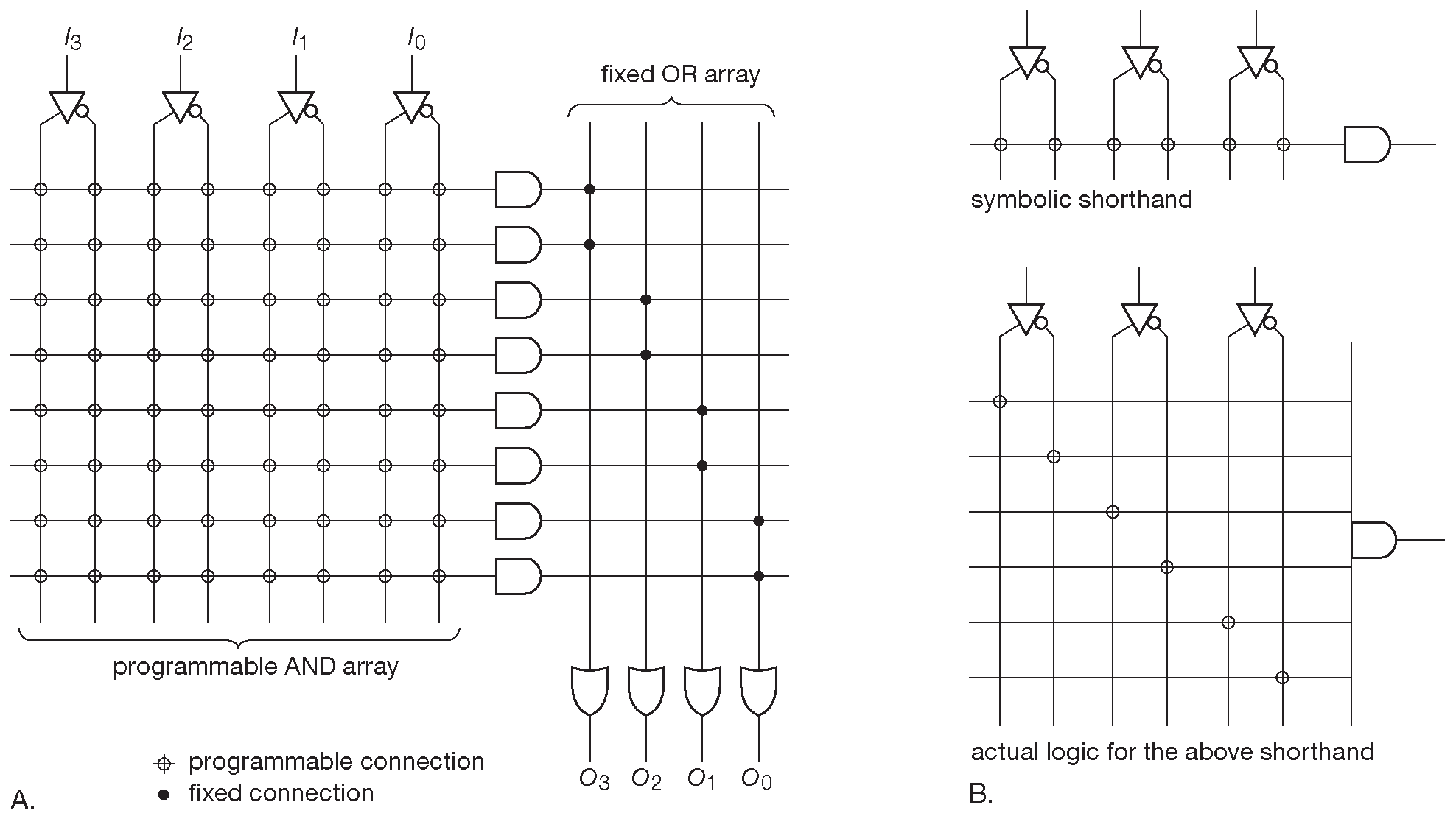

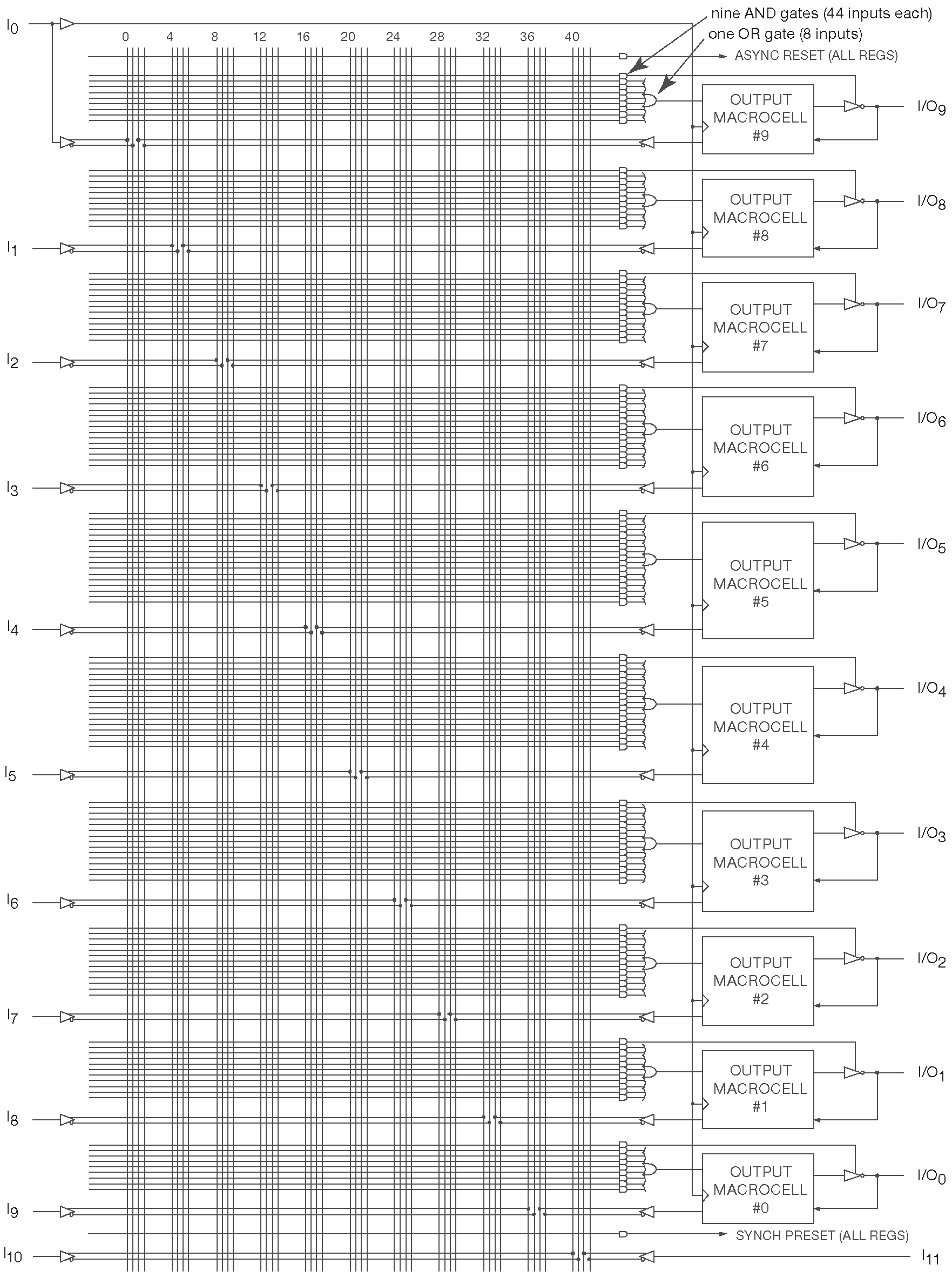

В настоящих PAL входов и вентилей гораздо больше. Структура реальной 22V10 показана на рис. 11.3 . Выглядит впечатляюще, но по современным стандартам очень скромная схема. 12 входов и их дополнения вместе с обратными связями с 10 выходов и тоже с дополнениями - всего 44 сигнала - заводятся в матрицу межсоединений. Теперь их в любом сочетании можно завести на любой 44-входовой элемент «И». Выходы «И» объединяются по «ИЛИ» с выходами других «И», причём таких «И» может быть от 7 до 15 ( по краям меньше, в центре больше ). Так получается 1 сигнал из 10 . Он не идёт на выход сразу, а заходит в макроячейку ( рис. 11.4 ), содержащую ещё немного логики, которая или защёлкивает сигнал в триггере, или пропускает его прямо на выход. По рис. 11.4 видно, что, кроме «регистрового» или «комбинационного», выход может быть ещё прямым, инверсным и вдобавок с Z-состоянием.

Рис. 11.3 Матрица межсоединений классической PAL 22V10 с архитектурой «программируемое_И/фиксированное_ИЛИ». Выходная макроячейка может работать как D-триггер или просто передавать сигнал на выход, см. рис. 11.4 . ( Схема взята из справочных данных ispGAL22V10 фирмы Lattice, ©Lattice Semiconductor Corporation, 2004 )

22V10 подходит для многих задач. На ней можно сделать регистр, счётчик, адресный декодер или просто собрать какую-то логическую схему. Но по современным воззрениям её возможности ничтожны как из-за ограниченного числа регистров и линий ввода-вывода, так и из-за единственного общего тактового сигнала «CLK». Счётчик пульсаций на 22V10 сделать нельзя.

Рис. 11.4 Программируемая «макроячейка» классической PAL 22V10. Выход может быть прямым, инверсным, комбинационным, регистровым и вдобавок с Z-состоянием. Кроме того, он заводится обратно в матрицу межсоединений. Сигналы «CLK», «SP» ( синхронная установка ) и «AR» ( асинхронный сброс ) являются общими для всех 10 макроячеек, а управление Z-состоянием идёт с индивидуальной для каждой макроячейки 44-входовой схемы «И»

Архитектуру можно развивать эволюционным путём, создав что-то вроде «супер-PAL», в которой тактовый сигнал для макроячеек можно брать из массива логики [* т.е. делать «асинхронную логику» ] , а число самих макроячеек увеличено. Всё перечисленное дополняется элементами, раздающими сигнал с выхода логики на соседние макроячейки. Такая модификация носит название cPLD и выпускается всеми производителями программируемой логики _6 . Число макроячеек может достигать 2000, плюс в таких ИМС есть линии синхронного тактирования. Часть ячеек при этом неизбежно оказывается «внутренней» , т.е. не имеет доступа к блокам ввода-вывода, хотя может участвовать во внутренних связях.

==767

==768

Архитектура «Программируемое-И/фиксированное-ИЛИ» ( иногда их называют «суммами произведений» ) сама по себе является ограничением, особенно если требуется блок чисто комбинационной логики, потому что допускает только одну сумму ( «ИЛИ» ) для нескольких произведений ( «И» ). Следующим уровнем сложности являются программируемые логические массивы PLA .

11.2.2 PLA

В PLA массив логики состоит из программируемых произведений ( «И» ), которые заводятся на программируемые суммы ( «ИЛИ» ), см. рис. 11.5 , в противоположность PAL, где «ИЛИ» фиксированы. Производители не разделяют PAL и PLA явным образом и называют оба типа cPLD. Чтобы понять, с чем предстоит работать, надо смотреть в справочные данные [* прямо скажем, необычный метод ] . Современный пример - CoolRunner-II ( XC2C ) фирмы Xilinx имеет от 32 до 512 макроячеек. В последнем случае половина макроячеек являются внутренними, поэтому у ИМС всего 324 вывода.

Рис. 11.5 Программируемый логический массив ( PLA ) - более гибкая схема, чем PAL ( рис. 11.2 ). В нём можно задавать конфигурацию и произведений «И», и сумм «ИЛИ»

Программные инструменты, используемые в работе с логическими матрицами, скрывают внутреннюю архитектуру кристаллов от пользователя. Обычно разработка состоит из создания кода на языке описания аппаратуры и прогона его через компилятор. Результат должен

- помещаться в выбранную матрицу и

- удовлетворять заданным временным ограничениям.

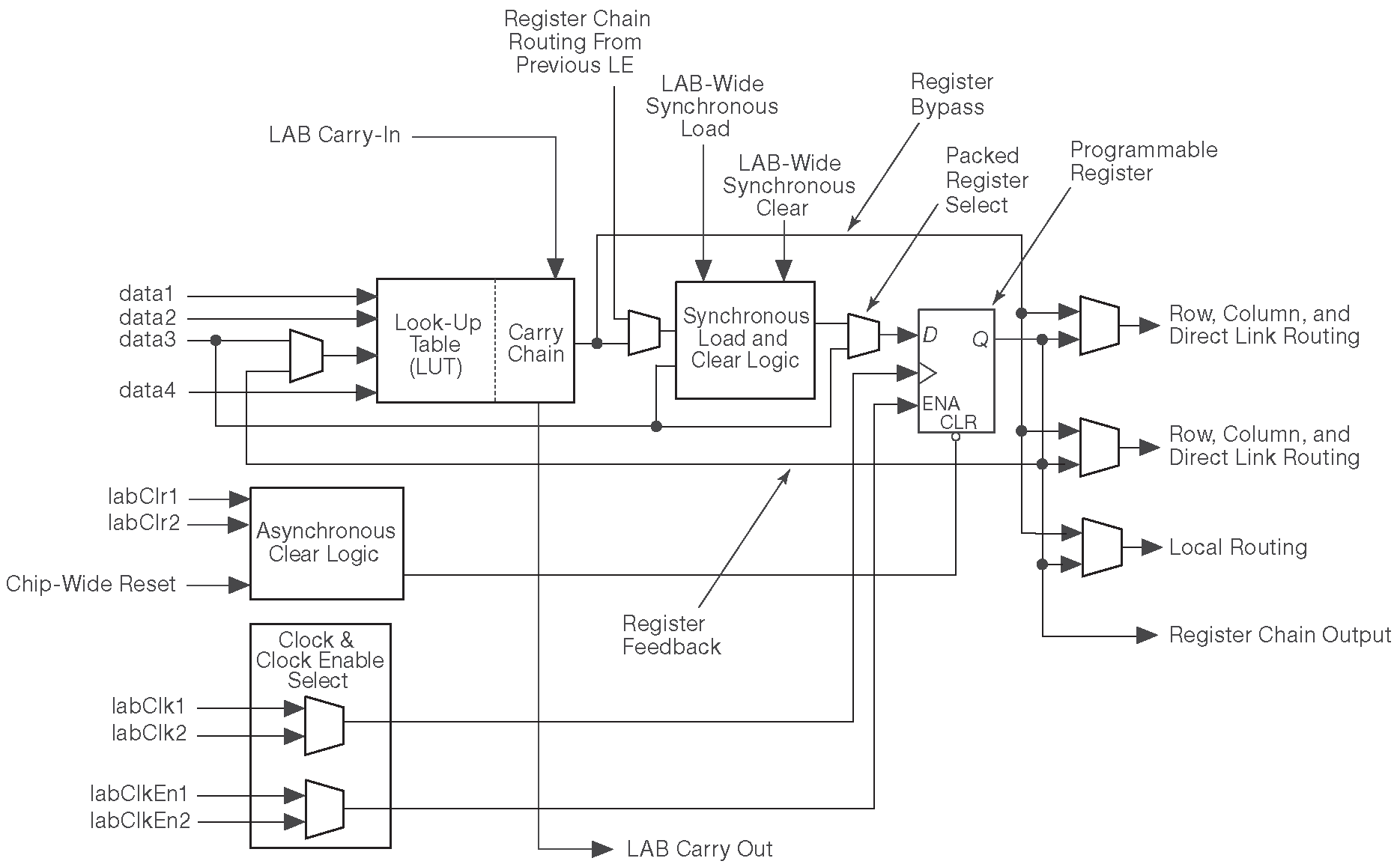

11.2.3 FPGA

PAL, PLA и cPLD - примеры того, что можно было бы назвать «много логики, мало регистров». Скажем, 22V10 имеет десятки 44-входовых элементов «И», связанных с вентилями «ИЛИ», но только 10 триггеров. Современный подход к вопросу выражен в FPGA. Это массив триггеров, на входе которых стоит небольшой блок логики ( обычно это четырёхвходовая таблица перекодировки - LUT , переплетённый массой линий связи. Речь идёт о десятках тысяч и более такого рода ячеек. Называют их «конфигурируемые логические блоки» ( CLB ) или «логические элементы» ( LE ). В комплекте идут блоки памяти, арифметические ускорители и умножители и даже встроенные процессоры и интерфейсные модули ( PCIe или Ethernet ). Такую «мелкодисперсную» _7 архитектуру можно назвать «мало логики, много регистров». Типичная ячейка показана на рис. 11.6 . В данном случае это Cyclone-II - FPGA фирмы Altera.

Рис. 11.6 Логический элемент ( LE ) FPGA, один из десятков тысяч таких же элементов в типичной ИМС из серии «Cyclone II» фирмы Altera. Тактируемый триггер и таблица перекодировки ( LUT ) обрамляются дополнительными элементами и расширяются за счёт управляющих сигналов из блока логики ( LAB ) более высокого уровня. ( Изображение взято в справочных данных семейства Cyclone II фирмы Altera, ©Altera Corporation, 2007 )

FPGA можно рассматривать как продвинутую специализированную ИМС, конфигурируемую пользователем. В старших моделях легко помещаются целые микропроцессоры вместе с периферийными устройствами, образуя системы-на-кристалле ( SOC ). Производители программируемой логики активно внедряют самые современные технологии в свои микросхемы. В результате современные FPGA всё активнее выступают альтернативой заказным кристаллам _8 , для которых характерна высокая стоимость разработки, меньшая универсальность и приличная задержка при выводе изделия на рынок . Последний параметр критически важен для потребительской электроники и делает FPGA экономически оправданным решением, несмотря на более высокую стоимость самих микросхем. Дополнительным плюсом идёт возможность модификации заданной конфигурации ( исправление ошибок, добавление новых функций и т.п. ).

==769

Обычная цена за небольшие cPLD и FPGA составляет один-два доллара, десять долларов за FPGA средней ёмкости и от ста долларов и до десятков тысяч (!) за старшие модели. Обычные FPGA не относятся к малопотребляющим схемам: типичных ток в режиме простоя исчисляется миллиамперами. Он дополняется динамическим током при высокой рабочей частоте. Но есть и микропотребляющие модели, предназначенные в первую очередь для мобильных приложений. К таким ИМС относится серия IGLOO фирмы Actel с током потребления в режиме ожидания на уровне 5..50 μW .

Крупнейшими игроками на рынке FPGA являются Altera и Xilinx ( родоначальник ). Небольшие модели выпускают Actel, Atmel, Cypress и Lattice.

11.2.4 Конфигурационная память

Программируемой логике надо где-то хранить конфигурацию внутренних связей. PLD всех видов держат эти данные в постоянной памяти на кристалле. Самые первые PAL фирмы MMI вообще имели однократные пережигаемые перемычки. Первые серии фирмы Altera ( например, MAX7000 ) имели кварцевые окошки и EPROM с ультрафиолетовым стиранием, но промышленность быстро перешла на память с электрическим стиранием ( EEPROM или Flash ). Сейчас так делаются все PLD. Стирание занимает секунды, а запись зависит от объёма, но обычно не больше минуты. В справочных данных есть параметр «минимальное время хранения» данных во внутренней конфигурационной памяти ( обычно порядка 20 лет ), стойкость составляет от 1000 до 10000 циклов стирания-записи.

Первые PLD требовали программатора - специального устройства, которым торговали BP Microsystems, Needhams Electronics и DatalO. Микросхемы требовалось сначала запрограммировать, а затем поставить на место в схему. Всё было хорошо, пока компоненты паковались в корпуса DIP с выводами под монтаж в отверстия. Для таких корпусов существуют панельки, которые можно было запаять на плату, но для SMT корпусов такая методика не работала. [* Поверхностные компоненты монтируют в специальной печи, где все корпуса сильно нагреваются, а вся программируемая память при этом норовит забыть всё, что в неё писали. Ну, или как минимум нагрев сокращает срок жизни данных в памяти ] . Решением стало программирование «в схеме» ( ISP ), которое в итоге добавили даже в старые серии PAL ( ispGAL22V10 фирмы Lattice - isp версия стандартной 22V10 ). Все современные PLD программируются внутрисхемно через порт граничного сканирования JTAG ( IEEE 1149 ) _9 . К выводам программирования микросхемы подключается адаптер, другим концом включённый в USB порт управляющей машины. Цена адаптера - около $100, см. обсуждение JTAG в §14.7.4 .

С FPGA ситуация иная. Традиционные серии не имеют внутри постоянной памяти, загружают конфигурацию из внешней микросхемы и хранят её, пока есть питание. Такая ситуация сохраняется по сей день, но теперь появились семейства FPGA с внутрикристальной конфигурационной памятью. Такие серии есть у Actel, Lattice и Xilinx. Как и cPLD, они программируются в схеме через адаптеры сравнимой стоимости.

11.2.5 Прочие программируемые логические устройства

Полезно помнить, что обычные микросхемы памяти - тоже относятся к программируемой логике: они выдают n-разрядное значение ( данные ) в ответ на m-разрядное входное воздействие ( адрес ). Так она используется в машине состояний общего вида ( рис. 10.64 ), а в совсем простом варианте 16×1 в таблице перекодировки ( LUT ) внутри логического элемента FPGA.

Существуют новые разработки программируемых микросхем смешанных сигналов . Примером является PSoC фирмы Cypress. Это программируемая микросхема, имеющая внутри усилители, фильтры и прочие аналоговые компоненты на одном кристалле с микропроцессором. [* Сейчас появились и чисто аналоговые программируемые микросхемы: см. Silego . Производитель утверждает, что параметры микросхем позволяют строить на них системы 12-разрядной точности ] .

11.2.6 Программное обеспечение

Прежде чем получится поработать с программируемой логикой, придётся поучиться работать с системой проектирования. Работа начинается с создания входного файла. Это может быть текст на языке описания аппаратуры или графическое изображение схемы. Затем запускается моделирование , которое проверит, что результат соответствует ожиданиям. Затем наступает черёд синтеза , который превращает схему в список связей - «нетлист» . Наконец включается размещение и разводка , в ходе которого нетлист размещается в целевом кристалле. Наконец размещённый и разведённый проект загружается в физическую микросхему: или в неё саму, или во внешнюю конфигурационную память, из которой FPGA грузится при включении питания. Возможна горячая загрузка конфигурации из вспомогательного процессора.

==770

Производители программируемой логики распространяют программное обеспечение для ИМС средней ёмкости бесплатно 10 , но захотят от нескольких сотен до тысяч долларов за поддержку старших моделей. Часть суммы уходит на программные блоки с уже отлаженными периферийными устройствами, относящимися к классу «интеллектуальной собственности» ( IP ). Учебным и некоммерческим проектам даётся большая скидка.

Изучать всё это программное обеспечение и так не легко, но оно ещё и постоянно меняется. В программах периодически находят ошибки, требующие глубоких знаний для поиска обходных путей. Это вполне себе работа на штатной должности. Тема располагает к изучению её некоторой командой таких же страдальцев, которая будет использовать одни программные инструменты. Другими словами, следует использовать те средства, которые использует большинство самых опытных людей в вашем окружении.

Авторы не ставят задачи научить использованию упомянутых программных средств. Вместо этого предполагается разобрать пример законченной разработки, выполненной пятью разными способами ( §11.3 ), в числе которых есть и вариант с cPLD ( §11.3.3 ).

==770

6 Например, серия MAX7000 ( Altera ), Mach 4000 ( Lattice ) или CoolRunner-II ( Xilinx ). Последняя использует более новую архитектуру PLA, см. §11.2.2 . <-

7 По случайному стечению обстоятельств эта изящная конструкция не попала в некоторых cPLD, которые и не PLD вовсе, а замаскированные FPGA. К таким сериям относятся Max-II ( фирма Altera cPLD, которые используют 4-входовые таблицы LUT ), Delta39K ( cPLDs фирмы Cypress ) или MachXO ( Lattice ). <-

8 Их иногда называют ASIC - интегральные схемы специального применения. <-

9 Организация IEEE опубликовала промышленный стандарт формата данных для внутрисхемной конфигурации через порт JTAG, см. IEEE 1532. <-

10 Пример: Xilinx “WebPACK”, загружаемый из интернета ( запаситесь терпением - придётся скачать и установить более 5GB данных ). <-