10.4 Логика последовательного действия

==728

10.4.1 Элементы с памятью: триггеры

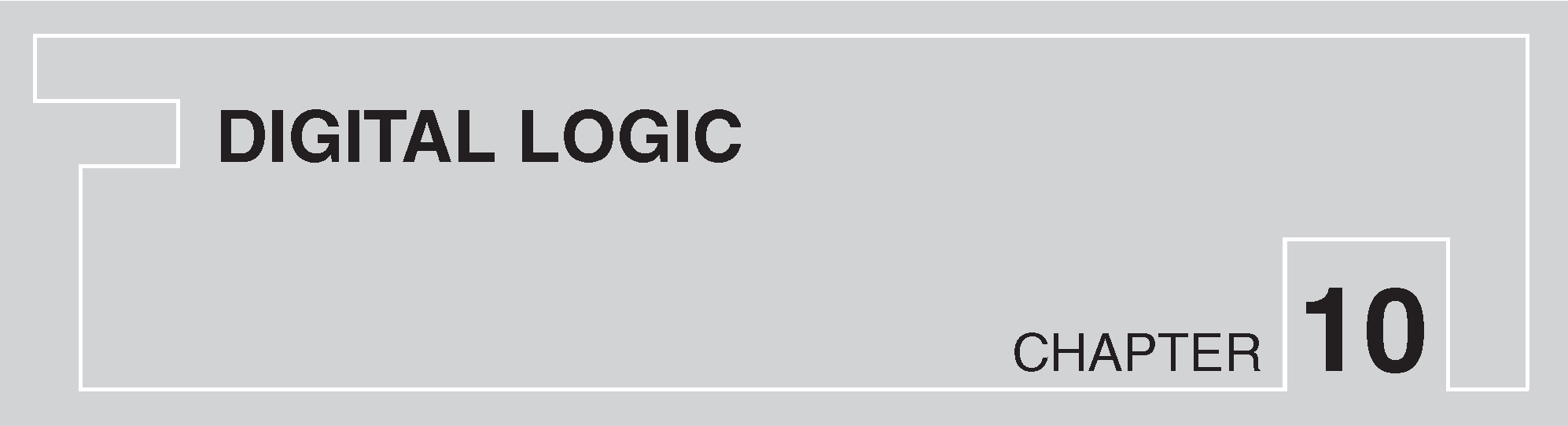

До настоящего момента разговор крутился вокруг комбинационных схем или набора логических вентилей. В таких устройствах состояние выхода целиком определяется текущим состоянием входов. В них нет ни «памяти», ни истории состояний. Но цифровая жизнь становится гораздо интереснее, когда у логики появляется память. При этом возникает возможность создавать счётчики, аккумуляторы и схемы, способные выполнять последовательные действия. Основой всех таких конструкций является триггер , в своём простейшем виде представленный на рис. 10.49 .

Рис. 10.49 Триггер типа RS ( “set-reset” )

==729

Предположим, что оба входа «A» и «B» в ВЫСОКОМ состоянии. Какие уровни на «X» и «Y» ? Если на «X» ВЫСОКИЙ, тогда оба входа \( G_2 \) в ВЫСОКОМ состоянии и «Y» - НИЗКИЙ. Такая ситуация совместима с ВЫСОКИМ уровнем на «X», и разбор можно закончить. Да?

X = HIGH, Y = LOW.

Нет! Схема симметрична, поэтому противоположное состояние столь же приемлемо.

X = LOW, Y = HIGH.

Невозможны только состояния с одинаковыми уровнями на «X» и «Y» ( напоминаем, что на «A» и на «B» - ВЫСОКИЙ ). Таким образом, триггер имеет два устойчивых состояния ( т.е. он «бистабильный» ). Какое состояние на выходах сейчас зависит от предшествующего состояния. Мы получили элемент с памятью. Чтобы записать в него значение надо кратковременно перевести один из входов в НИЗКОЕ состояние. Пусть, например, это будет вход «A». НИЗКИЙ уровень на входе «A» переведёт схему в состояние

X = HIGH, Y = LOW,

причём независимо от того, в каком состоянии она находилась ранее. Такую конструкцию называют RS триггером, который взводится или сбрасывается активным низким импульсом на одном из входов.

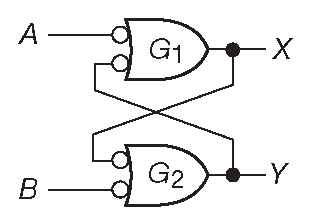

10.4.1.A Защита от дребезга контактов

Описанный триггер ( входы «SET» и «RESET» сокращают до «S» и «R» ) находит множество применений. Возьмём, к примеру, схему 10.50 . Предполагается, что разомкнутый переключатель переводит вентиль в разрешённое состояние 44 . Проблема в том, что контакты механических ключей дребезжат . Когда ключ замыкается, механические контакты вибрируют, отскакивают и вновь замыкаются, прежде чем замкнуться окончательно. За время порядка миллисекунды может пройти от 10 до 100 циклов замыкания- размыкания, а на сигнальной линии будет картина, показанная на рис. 10.50 . Если дальше по схеме стоит счётчик или сдвиговый регистр, то каждый цикл дребезга будет воспринят как тактовый сигнал.

Рис. 10.50 Дребезг ( “bounce” ) механического ключа

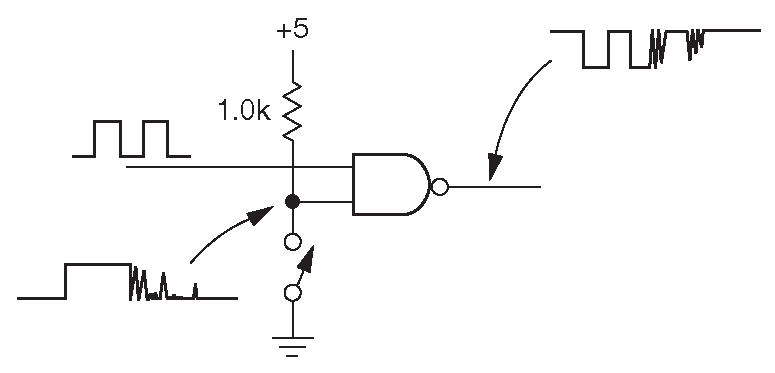

Защита показана на рис. 10.51 . RS триггер переключит своё состояние при первом же замыкании контактов. Все последующие изменения на линии не повлияют на состояние триггера. Та же картина будет наблюдаться и при переходе ключа в противоположное состояние. На выходе сигнал, свободный от дребезга, что и требовалось. Подобная схема активно используется. Есть элемент ’279 – «счетверённый RS триггер» и ’1G74 в одиночном варианте и мелком корпусе. К сожалению, иногда первый импульс на сигнальной линии новой схемы может быть короче прочих, если замыкание ключа придётся на активную половину импульса. То же можно сказать об укорочении при размыкании контактов. Понятно, что те же проблемы есть и у ключа без защиты от дребезга. Для предотвращения подобного развития событий можно использовать схему синхронизации ( см. §10.4.4 ).

Рис. 10.51 Защита от дребезга на RS триггере. Обратите внимание на укорочение импульса в сигнальной линии. Входы, помеченные «\(\bar S\)» и «\(\bar R\)», являются активными низкими входами «/SET» и «/RESET» триггера

==730

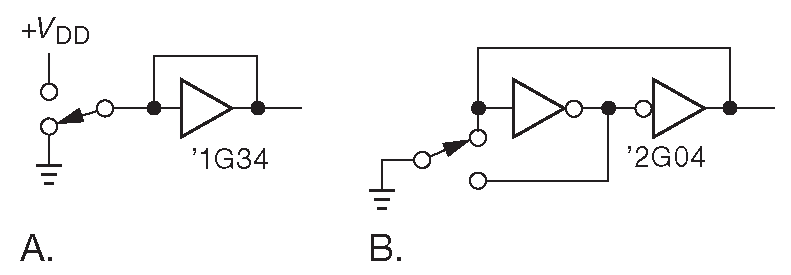

На рис. 10.52A показан приём, упрощающий схему защиты от дребезга. Неинвертирующий буфер ( его можно сделать из элемента ’08 – 2-входового «И» или двух инверторов ’04 и т.п. вентилей ). Он, подобно триггеру, сохраняет своё последнее состояние. Изменение положения переключателя на мгновение создаёт на выходе короткое замыкание и передавливает выходное напряжение буфера, заставляя последний переключиться ( без дребезга ). В момент самого короткого замыкания в цепи питания течёт большой ток, но сохраняется такое положение ровно на время распространения сигнала в логическом элементе, т.е. несколько наносекунд. Это совершенно безопасная и хорошо работающая схема, и единственным неудобством является дискомфорт от использования «грязных хаков» 45 . Если есть пара инверторов, то можно обойтись без подвода к тумблеру напряжения питания ( рис. 10.52B ). [* Зато от ключа к вентилю надо два провода тянуть ] .

Рис. 10.52. Упрощённая схема защиты от дребезга

[* Схема работает, потому что все механические ключи переключаются в режиме «разрыв перед новым подключением», см. §1.9.1.A Т.е. при изменении состояния ключ будет дёргать входную линию в формате «новое состояние или обрыв», а не «новое состояние или старое состояние». См. также §12.1.4.B ].

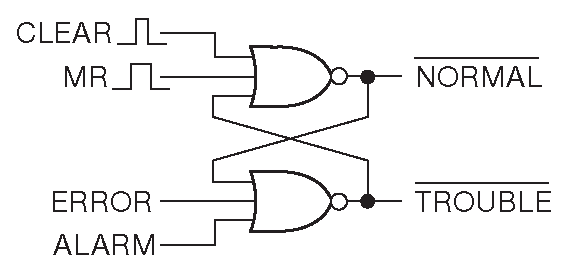

10.4.1.B Триггер с увеличенным числом входов

На рис. 10.53 показан ещё один вариант RS триггера. Здесь используются вентили «ИЛИ-НЕ». ВЫСОКИЙ уровень на входе вызывает появление НИЗКОГО потенциала на выходе. Множественные входы позволяют взводить и сбрасывать триггер разными сигналами. На этом фрагменте схемы нет подтяжек на землю, потому что в качестве источников выступают обычные логические выходы.

Рис. 10.53 RS триггер с увеличенным числом входов

10.4.2 Тактируемый триггер

Триггеры, собранные на паре вентилей ( рис. 10.49 или 10.53 ) называются RS триггерами прямого действия . Их можно перевести в одно или другое состояние, подав на вход нужный сигнал. Они удобны для защиты от дребезга и разных прочих дел. Но более массовые триггеры выглядят иначе. Вместо двух простых входов у них есть один или два входа данных и тактовый вход. Состояние на выходе остаётся прежним или меняется в зависимости от состояния входов данных в момент прихода тактового импульса.

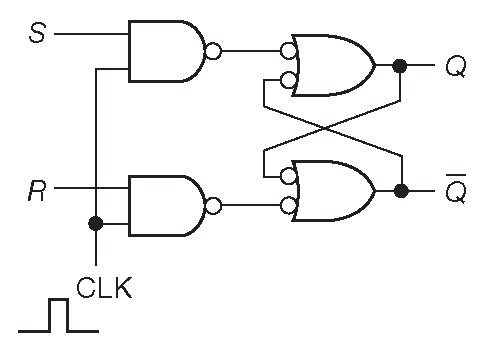

Самый простой вариант тактируемого триггера показан на рис. 10.54 . Это обычный RS триггер с парой дополнительных вентилей на входе. Они отвечают за тактирование и разрешают передачу входных сигналов на триггер. Легко убедиться, что таблица истинности выглядит следующим образом

Рис. 10.54 Тактируемый триггер. Первое приближение

S R Qn+1 0 0 Qn 0 1 0 1 0 1 1 1 X

==731

, где \( Q_{n+1} \) - состояние выхода «Q» после прихода тактового импульса, а \( Q_n \) - перед приходом. Основное различие с базовой схемой в том, что теперь «R» и «S» следует рассматривать в качестве входов данных ( как противоположность входам управления в простом RS триггере ). Состояние входов «R» и «S» должным образом определяет состояние «Q» в момент прохождения короткого тактового импульса. Во все остальные моменты времени состояние «R» и «S» на выход не влияет.

У нового триггера есть недостаток: пока на тактовом входе присутствует ВЫСОКИЙ уровень входы «R» и «S» прямо влияют на выход. В этот момент устройство вновь становится простым триггером ( такие схемы называют прозрачными защёлками : пока строб в разрешающем положении, выход видит состояние входа ). Полноценные тактируемые триггеры имеют несколько иную конструкцию. Это схемы вида «мастер-помощник» и триггер «срабатывающий по фронту».

10.4.2.A Работа по фронту: D-триггер

Это на данный момент самый популярный вид триггеров. Логический уровень, появившийся на входе «D» несколько ранее 46 прихода перепада тактового импульса, именуемого «фронтом» , определяет состояние выхода после смены уровня на тактовом входе.

Вот таблица истинности D-триггера :

D Qn+1 0 0 1 1

Его функционирование можно рассматривать как копирование состояния входа на выход. Одна из основных задач таких элементов - захват и хранение меняющихся логических уровней по команде с тактового входа 47 . Такие триггеры доступны в виде ИМС.

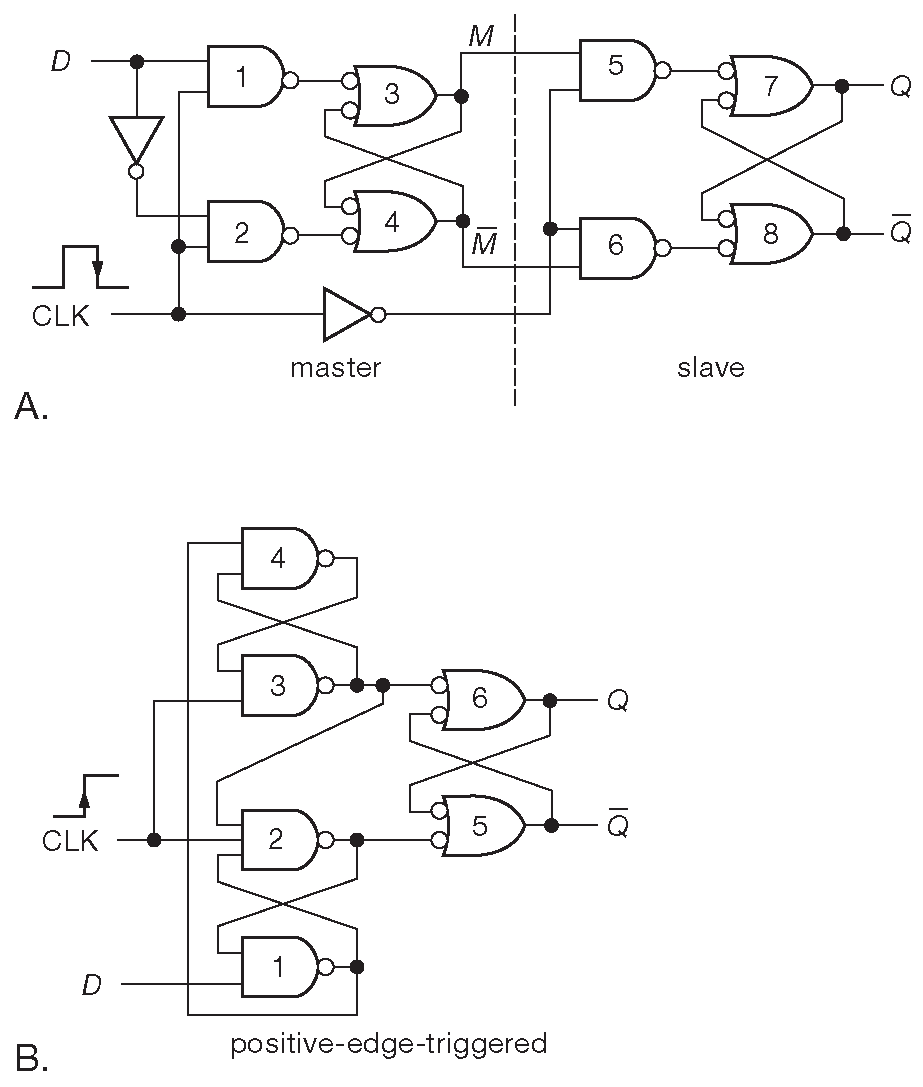

Полезно будет задержаться ненадолго и заглянуть внутрь D-триггера, чтобы понять, что там происходит. На рис. 10.55 показаны две конфигурации – «мастер-помощник» и «со срабатыванием по фронту». Первая проще для понимания. Разберём, как она работает.

Рис. 10.55 Триггеры с тактированием: «мастер-помощник» и D-триггер

Пока на тактовом входе ВЫСОКИЙ уровень, вентили «1» и «2» находятся в разрешённом состоянии и устанавливают мастер-триггер ( «3» и «4» ) в соответствие с уровнем на входе «D»: M=D, /M=/D . Вентили «5» и «6» в запрещённом состоянии, поэтому подчинённый триггер ( вентили «7» и «8» ) сохраняет предыдущее состояние. Когда тактовый вход переходит в НИЗКОЕ состояние, входы мастер-триггера отсоединяются от входа «D», а подчинённый триггер копирует состояние мастера себе на выход. Таким образом, проходит передача информации по схеме. Выходы более не меняются, потому что мастер хранит прежнее состояние. На следующем восходящем фронте подчинённый триггер отключится от мастера и будет хранить текущее состояние, а мастер начнёт отслеживать вход.

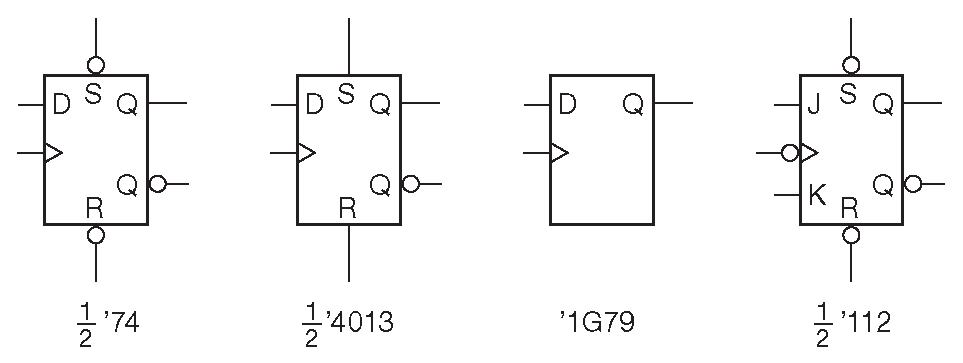

Функционирование работающей по фронту схемы снаружи выглядит так же, но отличается во внутренних деталях. Схема соответствует неизменно популярному триггеру ’74, срабатывающему по восходящему фронту. D-триггеры выпускаются под обе полярности тактового сигнала, и под восходящий, и под нисходящий фронт 48 . ( Разобранная выше схема «мастер-помощник» передавала данные на выход по нисходящему фронту ). Кроме того, большинство микросхем имеет дополнительные входы взведения и сброса прямого действия. Активный уровень последних зависит от конкретного типа триггера. На рис. 10.56 показаны некоторые примеры. «Клин» на выводе обозначает срабатывающий по фронту вход, а кружочек – «инверсию» или дополнение. Таким образом, ’74 - сдвоенный D-триггер, срабатывающий по фронту с активными низкими входами взведения и сброса прямого действия, ’4013 - сдвоенный D-триггер, срабатывающий по восходящему фронту, с активными высокими входами взведения и сброса прямого действия, ’1G79 - одиночный D-триггер, срабатывающий по восходящему фронту, без входов установки и без комплементарного выхода, и, наконец, ’112 - сдвоенный JK триггер типа «мастер-помощник» со сменой состояния по нисходящему фронту и активными низкими входами взведения и сброса прямого действия.

Рис. 10.56. D- и JK триггеры

JK и T-триггеры

JK- и T-триггеры работают аналогично D-типу. Вот их таблица истинности:

J K Qn+1 T Qn+1 0 0 Qn 0 Qn 0 1 0 1 /Qn 1 0 1 1 1 /Qn

Выход «Q» повторяет состояние «J» по активному тактовому фронту, если «J» и «K» имеют разное состояние. Если «J» и «K» оба НИЗКИЕ, триггер хранит прежнее состояние, а, если «J» и «K» - оба ВЫСОКИЕ, то триггер переходит в счётный режим и меняет состояние на каждом активном фронте.

T-триггер меняет состояние на выходе с каждым активным фронтом, если на входе «T» ВЫСОКИЙ уровень, или хранит прежнее состояние, если НИЗКИЙ.

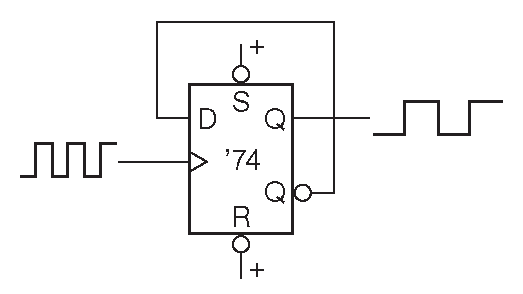

10.4.2.B Деление на 2

==732

В цифровых схемах часто нужны сигналы, переключающиеся с частотой, кратной некоторой исходной. Например, электронные наручные часы имеют внутри генератор опорной частоты 32768 Hz на кварцевом кристалле. Эта странная цифра выбрана, потому что она в 215 раз больше 1 Hz - частоты переключения секундной стрелки или изменения показания секунд. Здесь используются переключательные возможности триггеров. На рис. 10.57 показан D-триггер, который постоянно видит на своём входе «D» дополнение текущего состояния, и, соответственно, переключается с приходом каждого активного фронта, порождая на выходе частоту в 2 раза меньшую, чем частота тактирования.

Рис. 10.57 D-триггер в счётном режиме

На рис. 10.58 показано описание на Verilog для D-триггера в счётном режиме.

Рис. 10.58 Счётный режим D-триггера на Verilog

wire CLKIN; reg Q; always @( posedge CLKIN ) Q = ~Q;

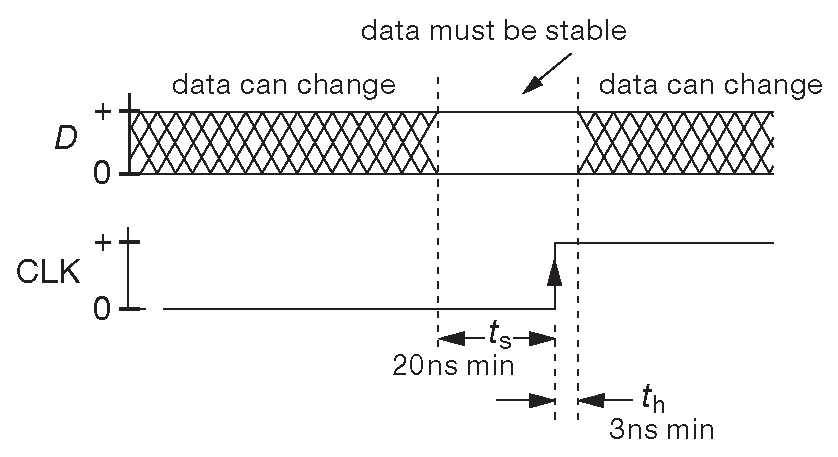

10.4.2.C Временная диаграмма для данных и тактового сигнала

Последняя схема поднимает интересный вопрос: переключится ли микросхема, если состояние входа «D» изменится почти сразу после прохода активного фронта ? [* Если речь о схеме 10.57 , то ответ: конечно переключится, ведь она УЖЕ переключилась, и именно поэтому изменилось состояние на входе ] . Или иначе, повлияют ли подобные события на работу триггера? Можно изменить вопрос: когда конкретно D-триггер ( или триггер другого типа ) «смотрит» на свой вход данных относительно активного тактового фронта? Ответ: существуют оговариваемые спецификацией параметры - время предустановки \( t_S \) и время удержания \( t_H \) , которыми характеризуется любое тактируемое устройство. Входные данные должны появиться и быть стабильными не позднее чем за \( t_S \) до прихода активного фронта и сохраняться не менее \( t_H \) после смены состояния на тактовом входе, чтобы схема гарантированно работала правильно. Для 74HC74 требуется \( t_S \) =20 ns и \( t_H \) =3 ns ( рис. 10.59 ). Таким образом, для схемы 10.57 условие по \( t_S \) выполняется, если данные появятся более чем за 20 ns до прихода восходящего фронта. Можно обеспокоиться временем удержания, но здесь тоже всё хорошо. Минимальная задержка распространения сигнала от активного фронта до выхода составляет 10 ns , поэтому D-триггер в счётном включении гарантированно укладывается в требования спецификации. Большинство современных разработок имеет нулевое время удержания.

Рис. 10.59 Время предустановки и удержания для триггера 74HC74

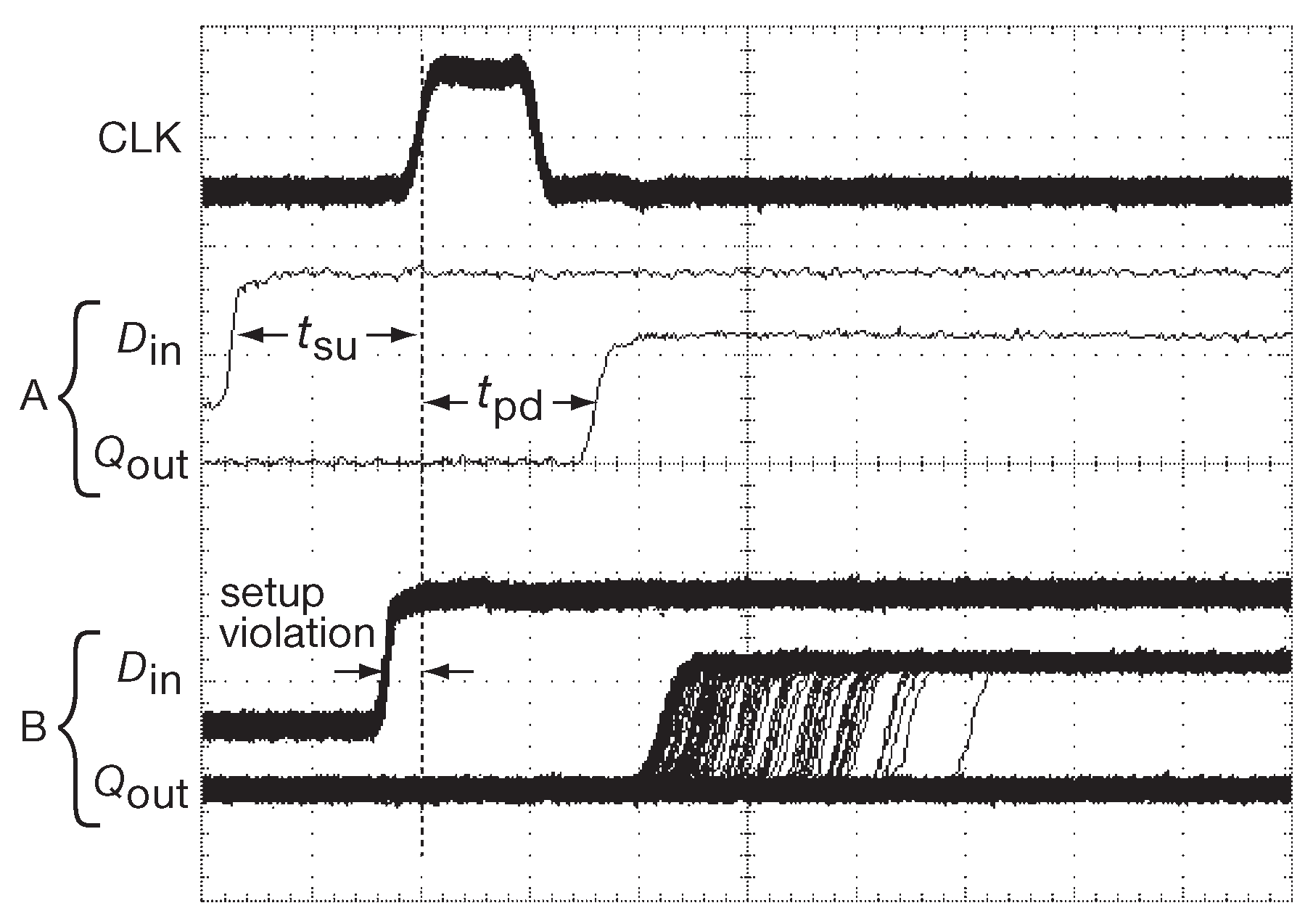

10.4.2.D Метастабильность

==733

Интересная проблема возникает, если уровень на входе «D» меняется в течение интервала \( t_S \). Проблема носит название метастабильное состояние и отражает ситуацию, когда триггер лишается возможности решить, в какое состояние он будет переключаться. Рис. 10.60 показывает, что происходит, если намеренно менять данные на входе с нарушением времени предустановки. 74HC74, работающий от +3.3 V , получает на входе «D» изменение состояния ( ВЫСОКИЙ уровень ) в самый последний момент. Выход «Q» честно думает положенное время, в какое же состояние ему переключиться 49 . Луч осциллографа отражает данные за примерно 2 s , в течение которых обнаруживаются события с задержкой переключения до 50 ns ( при нормальном времени 16 ns ). После нескольких минут работы в таком режиме рекорд увеличился до 75 ns . Более быстродействующие семейства имеют пропорционально меньшие времена, а для некоторых заявляется «устойчивость к метастабильности» 50 . Эксперименты с 74LVC74 ( +3.3 V питания ) показали, что метастабильность ( между прочим, для времени \( t_S \) всего 0.4 ns! ) приводила к удлинению времени задержки до 2...4 ns при нормальной цифре 1.4 ns 51 .

Рис. 10.60 Нарушение временнЫх требований спецификации ведёт к появлению метастабильного состояния в тактируемых устройствах. В данном случае нарушено время предустановки данных на входе «Din» ИМС 74HC74 ( пара лучей B ). В результате выход «Qout» получает изрядную дополнительную задержку относительно фронта CLK, если сравнивать с нормальным временем ∼16 ns ( пара лучей A ). По горизонтали 10 ns/div

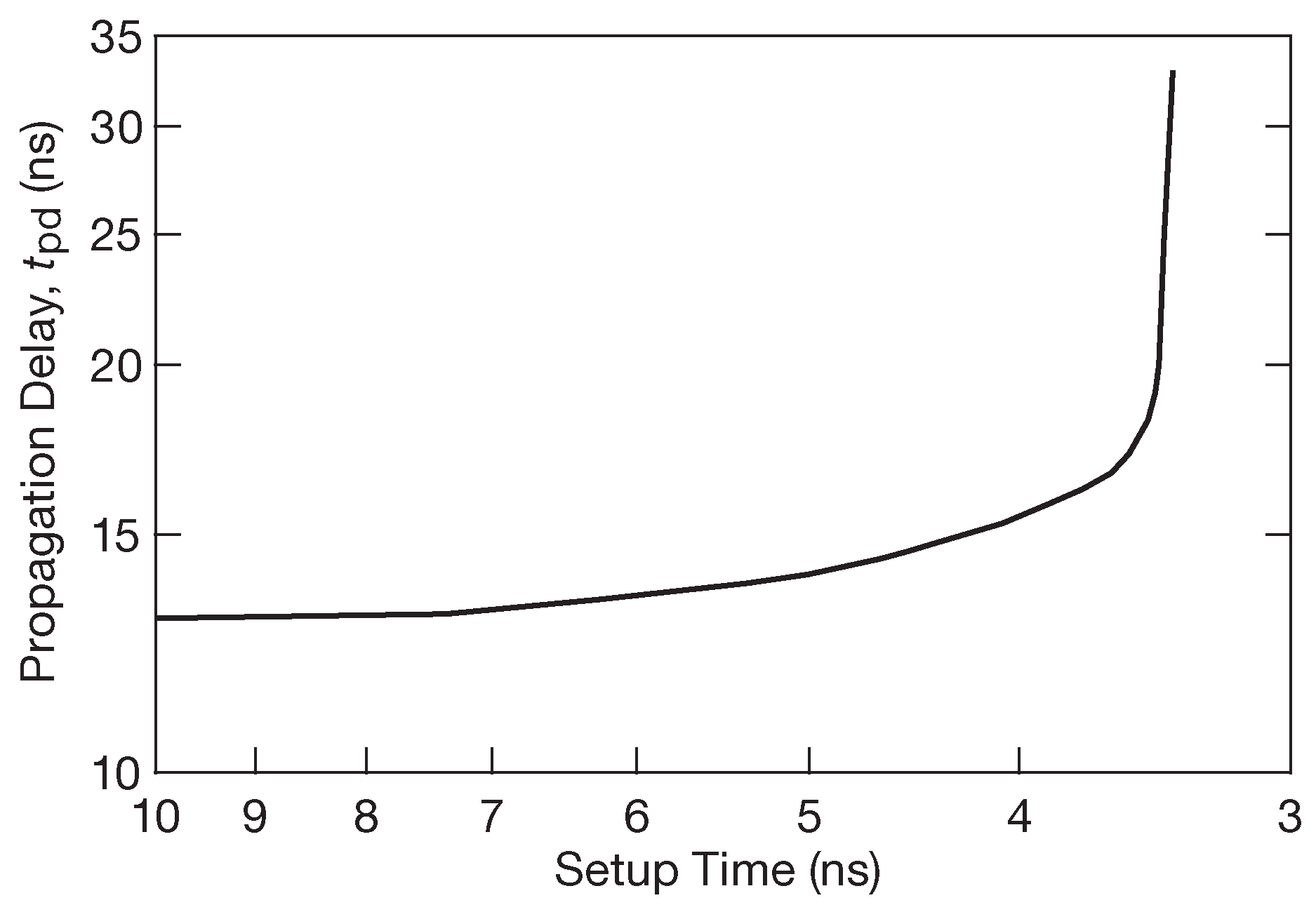

Из интереса было измерено увеличение времени «на раздумья» для триггера 74HC74 по мере сокращения времени между сменой состояния и приходом активного фронта. Результат показан на рис. 10.61 .

Рис. 10.61 Хвост дракона: рост метастабильной задержки по мере приближения момента смены данных к активному фронту для 74HC74

10.4.2.E Деление с коэффициентом большим чем 2

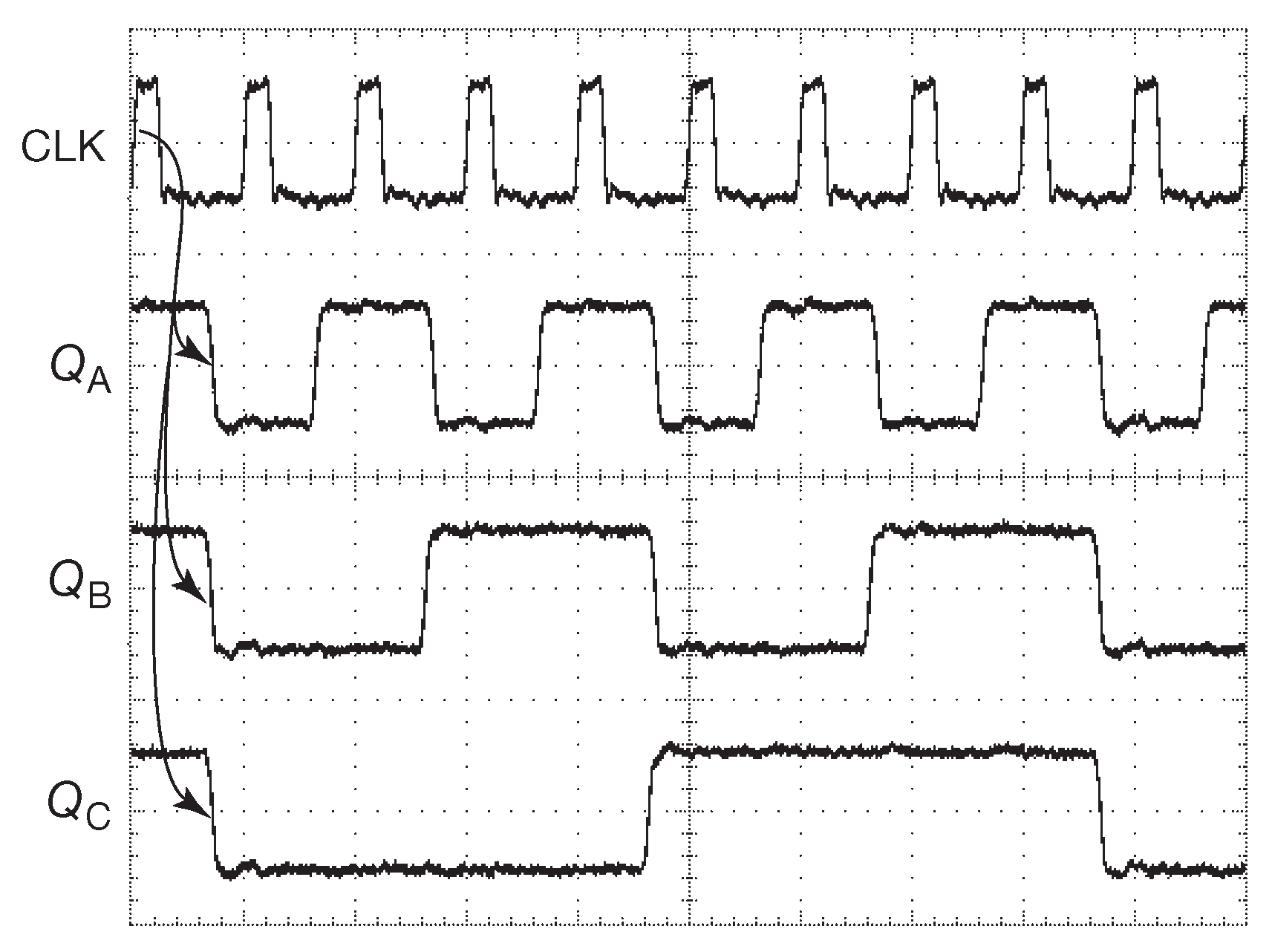

Собрав цепочку счётных триггеров ( подключив выход «Q» на тактовых вход следующей ступени ), легко получить делитель на 2n или двоичный счётчик. На рис. 10.62 показан трёхразрядный счётчик пульсаций или «делитель-на-8». На выходе последнего триггера частота в 8 раз меньшая, чем на входе счётчика. Схема называется счётчиком , потому что состояние выходов всей цепочки можно рассматривать как 3-разрядное двоичное число, увеличивающееся после каждого входного импульса. ( Здесь для тактирования используются выходы «/Q», чтобы получить прямой счётчик, считающий вверх , а не вниз 52 ).

Рис. 10.62 3-разрядный двоичный счётчик пульсаций

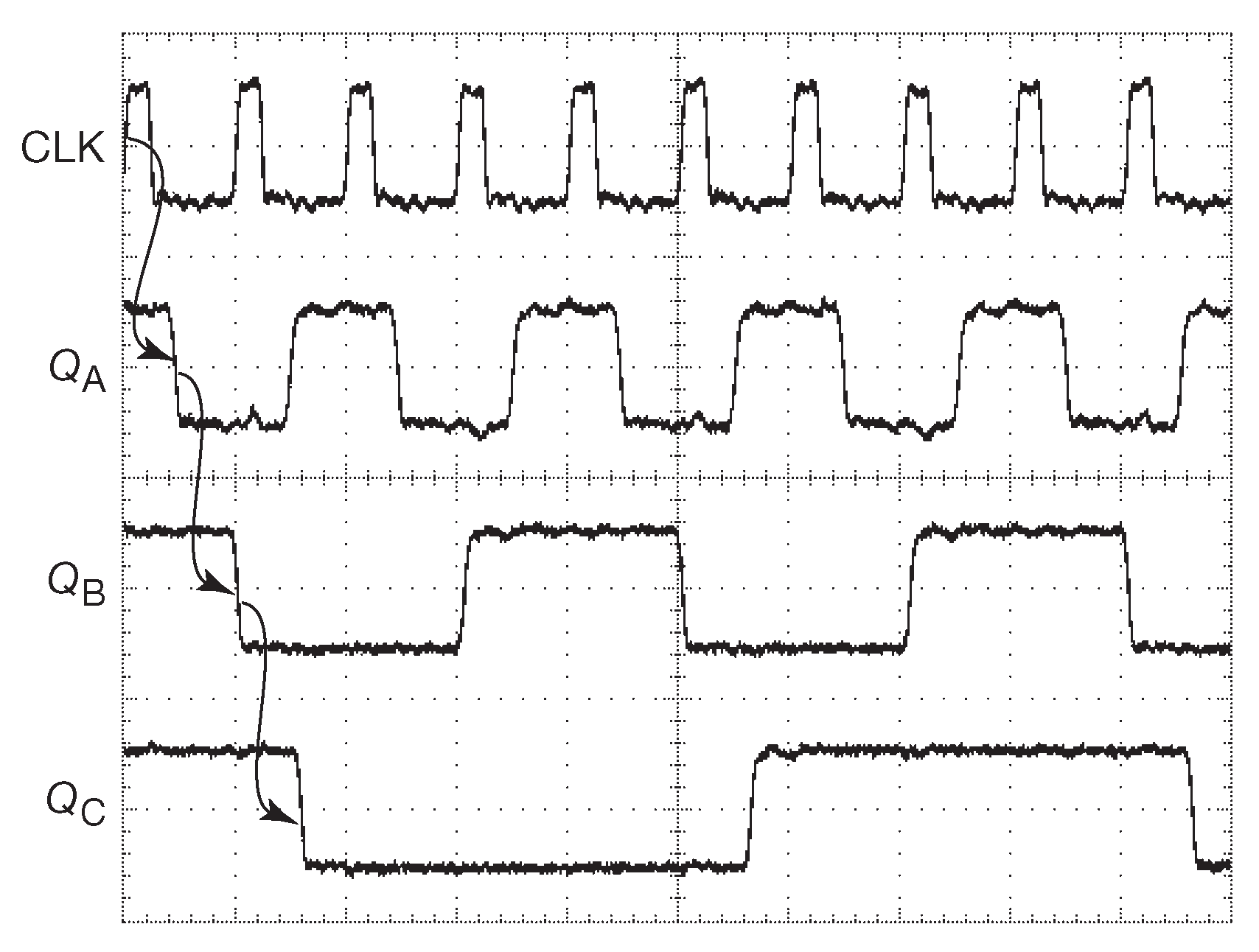

На рис. 10.63 показаны сигналы на выходе каждой ступени делителя, работающего от 50 MHz . Чтобы показать последовательность событий, на рисунок добавлены стрелки. Можно видеть двоичные числа от 0 до 7 , причём QA - младший разряд , а QC - старший . Хорошо видна задержка, последовательно нарастающая от разряда к разряду ( отсюда и термин «счётчик пульсации» ) 53 .

Рис. 10.63 Временная диаграмма работы счётчика пульсаций. Экран осциллографа показывает работу цепочки триггеров 74HC74 на частоте 50 MHz , срабатывающих по восходящему фронту. Видно последовательное увеличение задержки распространения ( по ∼10 ns на ступень ). Счётчик начинает работу из состояния ( 1,1,1 ) и перещёлкивается в ( 0,0,0 ) самым первым слева восходящим фронтом сигнала CLK . См. рис. 10.71 , где показана картина для синхронного варианта. По горизонтали 20 ns/div , по вертикали 4V/div

Простая схема соединения счётных триггеров в цепочку создаёт проблемы с нарастающей каскадной задержкой, неуклонно увеличивающейся по мере прохождения сигнала вниз по цепочке. Синхронная схема, при которой все ступени переключаются единым тактовым сигналом, проблем с нарастанием задержки не имеет 54 . Вскоре будет показано, как устроен синхронный счётчик.

==734

Счётчик - полезная функция и в стандартной логике представлены самые разные их виды, в т.ч. двоичные, BCD и многоформатные. Каскадируя несколько микросхем можно получить счётчик событий. Если считывать его с частотой 1 Hz , то на выходе будет число событий за секунду.

10.4.3 Объединение памяти и логики: логика последовательного действия

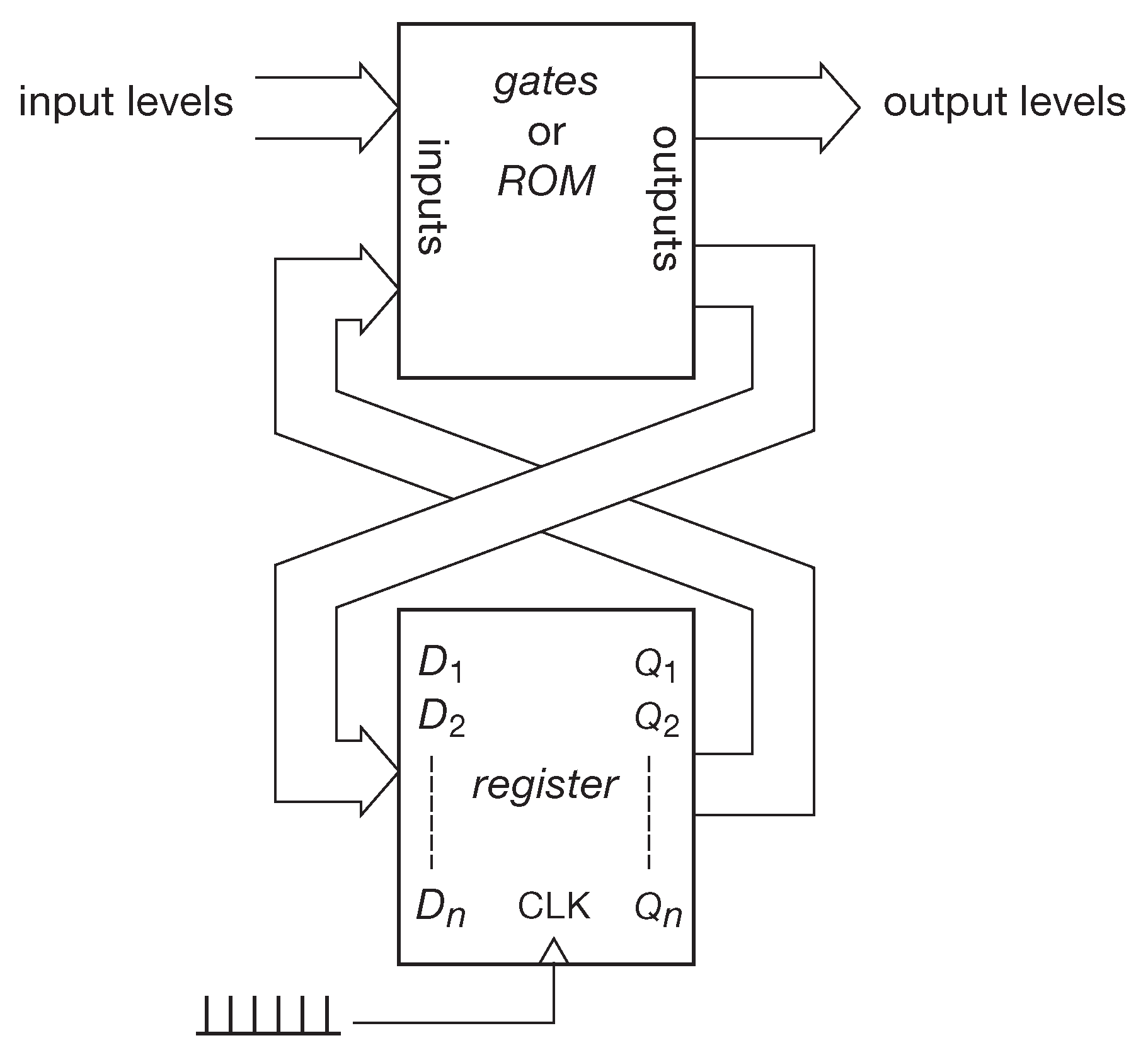

Исследуя возможности триггеров, полезно посмотреть, что можно построить, дополнив триггеры комбинационными схемами. Конструкции, собранные из вентилей и триггеров образуют новый вид логики

10.4.3.A Синхронные тактируемые схемы

В предыдущем параграфе было заявлено, что логика последовательного действия, в которой общий тактовый сигнал приводит в действие все триггеры разом, имеет весьма интересные свойства. В таких синхронных схемах все события происходят в момент прихода тактового импульса, основываясь на стабильных состояниях, предшествующих его появлению. Устройство завершает переход в новое состояние до наступления следующего такта. Такое поведение очень удобно для задания обратной связи, а синхронная работа триггеров позволяет избавиться от цифрового шума непосредственно перед тактовым импульсом ( затишье перед бурей ).

Общая схема показана на рис. 10.64 . Все триггеры собраны в один регистр , который является просто группой D-триггеров, чьи тактовые входы объединены, а от каждого триггера наружу выводятся только линии «D» и «Q». Как обычно, тактовый импульс передаёт данные со входа «D» на выход «Q». Набор вентилей смотрит на выходы регистра и входные линии микросхемы и формирует новое состояние для входов «D» регистра и комбинационных выходов устройства. Эта, простая на первый взгляд, организация обладает огромными возможностями и является основой цифровых процессоров. Разберём пример.

Рис. 10.64 Классическая последовательная «машина состояний»: набор счётчиков плюс набор комбинационной логики. Такая конструкция легко реализуется с помощью программируемой логики ( cPLD и FPGA )

[* Такая идеология построения схем называется «синхронная архитектура» и является идеологической противоположностью старого стиля «асинхронного проектирования» ].

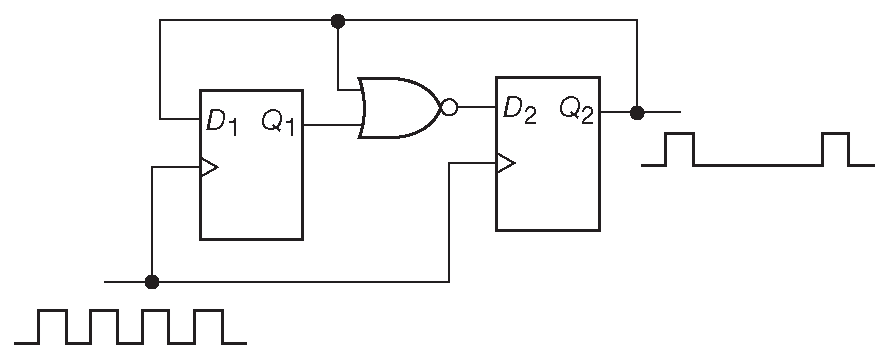

10.4.3.B Пример: делитель на 3

==735

Давайте создадим синхронный «делитель-на-3» на двух D-триггерах, тактируемых одним сигналом. В данном случае «D1» и «D2» - входы регистра, а «Q1» и «Q2» - его выходы, плюс есть общая линия тактирования ( рис. 10.65 ). Задача состоит в таком выборе и подключении внешних вентилей, которое позволит создать правильное сочетание сигналов на входах «D», нужное для перехода к следующему состоянию.

Рис. 10.65 Заготовка для «делителя-на-3»

- Выбираем три состояния. Пусть это будут

Q1 Q2 0 0 0 1 1 0 0 0 ( начальное состояние )

- Находим комбинационную таблицу последовательности состояний, т.е. изобразим, что должно быть на входах «D», чтобы получить нужное сочетание на «Q».

Q1 Q2 D1 D2 0 0 0 1 0 1 1 0 1 0 0 0

- Собираем подходящие вентили, которые переведут состояние на «Q» в комбинацию на «D». В общем случае для этого подходит «таблица подстановок» ( LUT ) - таблица перекодировки в ПЗУ ( ROM ), в которую заносится нужное состояние на входах «D», а выбор нужной записи ( адресация ) проводится текущим состоянием выходов «Q» и входов управления устройства 55 . В нашем случае пример очень простой и решается с помощью единственного вентиля:

D1 = Q2, D2 = /(Q1 + Q2).

Из данных уравнений вытекает схема 10.66 .

Рис. 10.66 Синхронный делитель на 3

Правильности её работы проверяется просто. Счётчик синхронный, поэтому, в отличие от счётчика пульсаций, все выходы меняются одновременно. В общем случае синхронные ( тактируемые ) системы гораздо удобнее, потому что менее восприимчивы к шуму, т.к. сигналы на входах успокаиваются раньше, чем приходит тактовый импульс. В итоге устройства, считывающие вход строго по фронту тактового сигнала, менее чувствительны к емкостным наводкам от соседних цепей. Синхронная система нечувствительна к событиям, происходящим после прохода тактового импульса, поэтому в ней отсутствуют ложные срабатываний при смене состояния вентилей логики, которое может порождать кратковременные ложные сочетания сигналов из-за разных схемных задержек. Некоторые примеры будут показаны позже

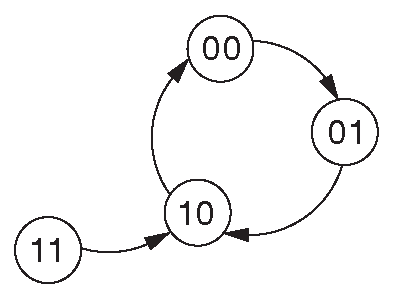

10.4.3.C Пропущенные состояния

Что произойдёт со схемой «делителя-на-3» , если по каким-нибудь причинам он попадёт в состояние ( 1,1 )? Это легко может случиться в момент подачи питания, потому что о начальной установке никто не позаботился. По рис. 10.66 видно, что первый тактовый импульс вызовет переход в состояние ( 1,0 ), после чего будет продолжена нормальная работа. Проверять исключённые состояния системы требуется в обязательном порядке, потому что какое-нибудь из них может не иметь выхода на нормальный цикл и вызовет зависание схемы. Правильная последовательность разработки устройства должна включать спецификацию всех возможных состояний системы. Полезным инструментом является диаграмма состояний , которая для предложенного примера выглядит как на рис. 10.67 . Обычно возле стрелок выписываются условия для каждого перехода, если они зависят от нескольких переменных. Стрелки могут идти в обоих направлениях, соединять несмежные состояния или вести к нескольким состояниям.

Рис. 10.67 Диаграмма состояний «делителя-на-3»

Код для схемы 10.66 на языке Verilog приводится на рис. 10.68 ( на этот раз в виде законченного «модуля» ).

Рис. 10.68 Описание на Verilog для синхронного «делителя-на-3»

module divideBy3( CLKIN, Q1, Q2 );

input CLKIN;

output Q1, Q2;

reg Q1, Q2;

always @( posedge CLKIN ) begin

Q1 <= Q2; // the "<=" symbol is called a "nonblocking assignment"

Q2 <= ~( Q1 | Q2 ); // it takes all steps happen at once, not sequentially

end

endmodule

Упражнение 10.23

Нарисуйте синхронный «делитель-на-3», используя два JK триггера. Задача может быть решена 16 различными способами без привлечения внешних логических элементов.

Подсказка При построении таблицы для состояний на «J» и «K» входах обоих триггеров учитывайте, что для пары «J, K» есть два пути в нужное состояние в каждый момент времени. Например, если выход триггера должен перейти из 0 в 1 , «J» и «K» могут быть в сочетании ( 1, X ), где X - любое состояние. Наконец, требуется проверить схему на зависание в исключённом состоянии ( из 16 решений задачи 4 зависают, а 12 - нет ).

==736

Упражнение 10.24

Разработайте синхронный 2-разрядный реверсивный ( UP/DOWN ) счётчик. У него должен быть тактовый вход, вход управления ( «U/D» ) и два выхода «Q1» и «Q2». Если «U/D» ВЫСОКИЙ, счёт идёт вверх с увеличением чисел, а, если «U/D» НИЗКИЙ, то счёт идёт вниз Q2Q1 = 00, 11, 10, 01, 00...

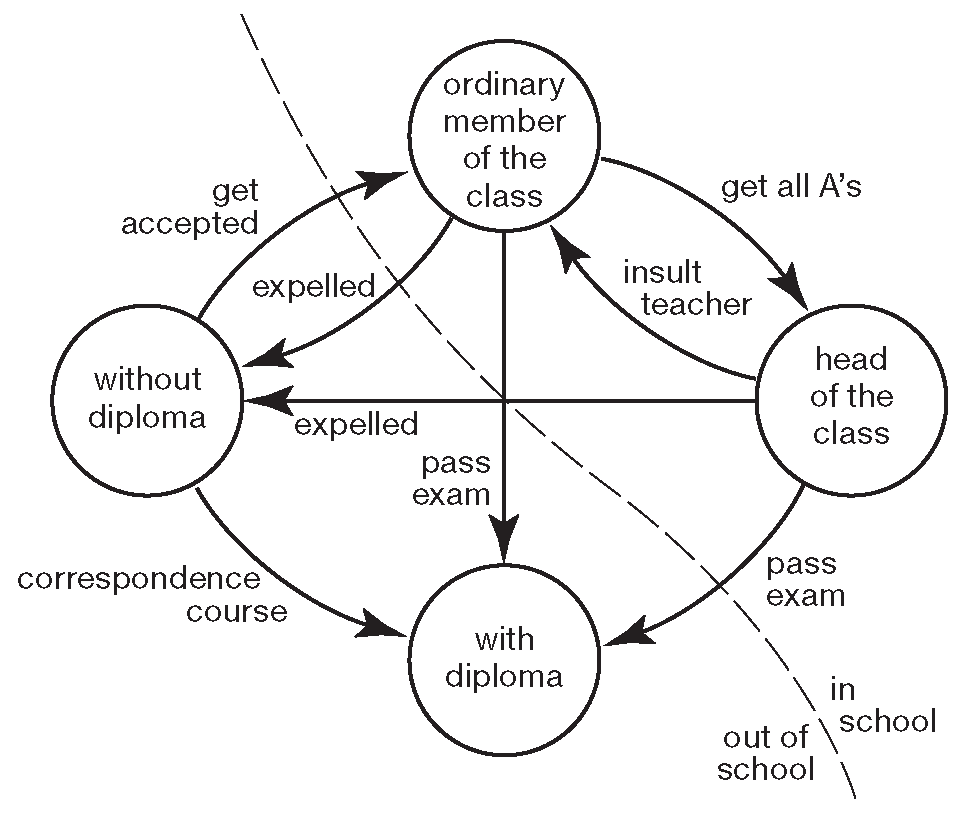

10.4.3.D Диаграммы состояний как инструмент разработки

Диаграммы состояний могут быть очень полезны при построении логики последовательного действия, особенно если состояния могут переходить одно в другое несколькими путями. При таком подходе работа начинается с выбора набора уникальных состояний системы и задания для них уникальных имён, скажем, двоичных номеров. Потребуется n триггеров, где n -наименьшее число, для которого 2n больше или равно числу нужных состояний [* с двоичными номерами всё просто: сколько разрядов у самого большого номера состояния, столько и триггеров ] . Далее выписываются все правила для переходов между состояниями, например, перечисляются все условия для попадания в каждое состояние и выхода из него. После чего остаётся очевидная, хотя, возможно, занудная работа по переводу таблицы в комбинационную логику, потому что имеется полный набор сочетаний выходов «Q» и входов «D». Таким способом последовательность действий превращается в комбинационную схему 56 . На рис. 10.69 показан пример из жизни. Обратите внимание, что бывают состояния, из которых нет перехода ни в какое другое [* «конечные состояния» ] , например, в данном случае это «with diploma».

Рис. 10.69 Диаграмма состояний для школьного обучения

10.4.3.E Разработка машины состояний

Языки описания аппаратуры, используемые для текстового описания схемы для обоих видов программируемой логики ( cPLD и FPGA ), а также заказных кристаллов ( ASIC ) имеют удобные инструменты для описания машин состояний. В их числе синтаксические конструкции if - elseif - else , которые позволяют задавать условия переходов и сигналы на выходах по набору входных условий и номеру текущего состояния. Программа конвертирует текстовое представление в схему, собранную на привычных логических элементах и триггерах.

Ещё одно замечание о машинах состояния. Блок-схема на рис. 10.64 допускает двоякую реализацию.

- Состояние выходов машины может зависеть только от номера актуального состояния машины, а так как оно определяется сочетаниями уровней на выходах «Q», то текущая комбинация выходов и является номером состояния. Это машина Мура .

- Для каждого состояния машины её выходные сигналы зависят от сочетания выходов «Q» и входов комбинационной части, прячущейся под надписью «вентили или ПЗУ» . Это машина Мили 57 .

Машина Мура изменяет состояние только по фронтам тактового сигнала и, если выходы «Q» являются одновременно и выходами машины, то такая конструкция получается чисто синхронной. Машина Мили асинхронна ( меняет состояние без участия тактового сигнала ) и реагирует на изменение тактовых входов. В общем случае ей требуется меньше триггеров, потому что одному состоянию машины ( определяемому числом выходов «Q» ) может соответствовать несколько сочетаний её выходов.

==737

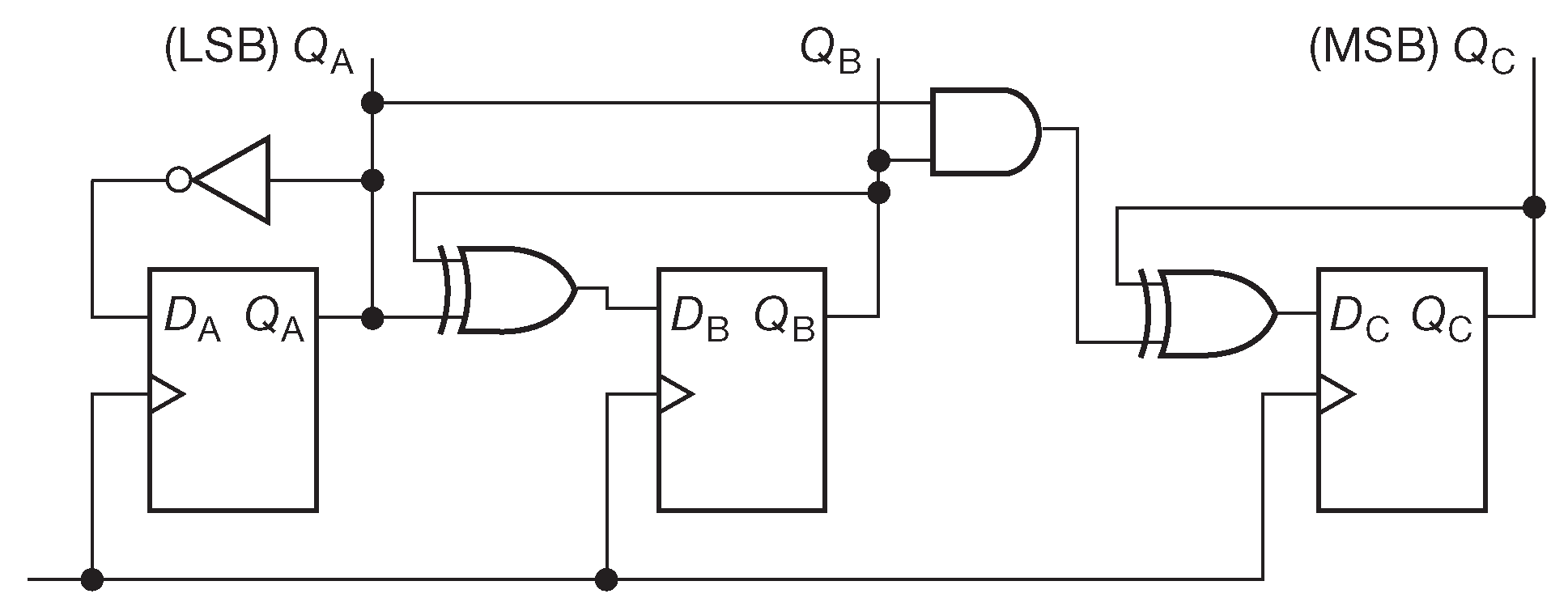

10.4.3.F Синхронный двоичный счётчик

Ранее был анонсирован возврат к старой схеме 3-разрядного счётчика пульсаций ( §10.4.2.E ) с целью превращения её в синхронную. Рис. 10.70 показывает результат работы. LSB переключается всегда, потому что всегда видит на входе собственное инвертированное состояние. Для всех следующих разрядов правило одно: переключаться надо, только когда все предыдущие разряды в единичном состоянии. Т.к. «ИСКЛЮЧАЮЩЕЕ-ИЛИ» является «управляемым инвертором», задача легко решается запитыванием входа «D» с выхода такого «инвертора». При этом на вход «включения инверсии» подаются собранные по «И» младшие разряды, а на «информационный» вход - собственный выход «Q». На языке описания аппаратуры всё это выглядит понятнее 58 .

Рис. 10.70 3-разрядный синхронный двоичный счётчик

QA. d = !QA.q QB. d = QB.q $ QA.q QC. d = QC.q $ (QB.q & QA.q)

Все выходы «Q» переключаются одновременно, как и требовалось 59 , что можно видеть на временнОй диаграмме 10.71 . На ней показан выход 3-разрядного синхронного двоичного счётчика, работающего на той же частоте, что и счётчик с рис. 10.63 . В таком виде легко опознать в разных состояниях числа от 0 до 7 .

Рис. 10.71 В синхронном счётчике, в отличие от асинхронного счётчика пульсаций ( рис. 10.62 ), все триггеры тактируются от одного сигнала. Здесь приведена временная диаграмма для 74HC161 – «4-разрядного синхронного счётчика», срабатывающего по восходящему фронту ( все прочие условия как на рис. 10.63 ). Из неё видно, что задержка «такт-выход» составляет 14 ns и одинакова для всех выходов. В итоге состояния выходов меняются одновременно

10.4.3.G Машины состояний в ПЛМ

Программируемая логика - это как раз то, что требуется для создания машины состояний. Есть масса триггеров и ещё больше логических элементов, связи между которыми могут быть настроены как требуется ( отсюда и термин «программируемая» ). Программное обеспечение включает инструменты, делающие разработку машин состояния рутинным делом. Поговорим об этом в §10.5.4 и в Части 11 .

10.4.4 Синхронизация

Интересным использованием триггеров в логике последовательного действия является синхронизация . Предположим, имеется некоторый внешний управляющий сигнал, который приходит в синхронную систему со всеми её тактовыми сигналами, триггерами и всем прочим. Требуется использовать данный сигнал для управления неким действием. Например, прибор на экспериментальной установке может сообщать, что данные готовы к передаче в компьютер. И прибор, и компьютер танцуют под разную музыку, иначе говоря, асинхронны друг к другу. Требуется организовать конструктивный диалог.

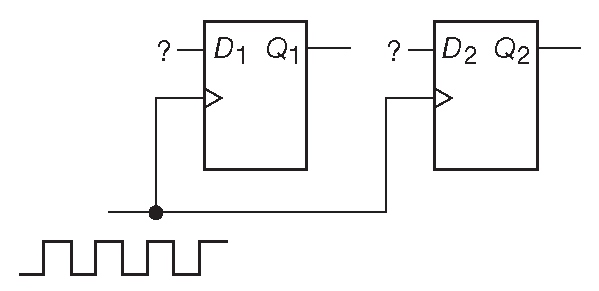

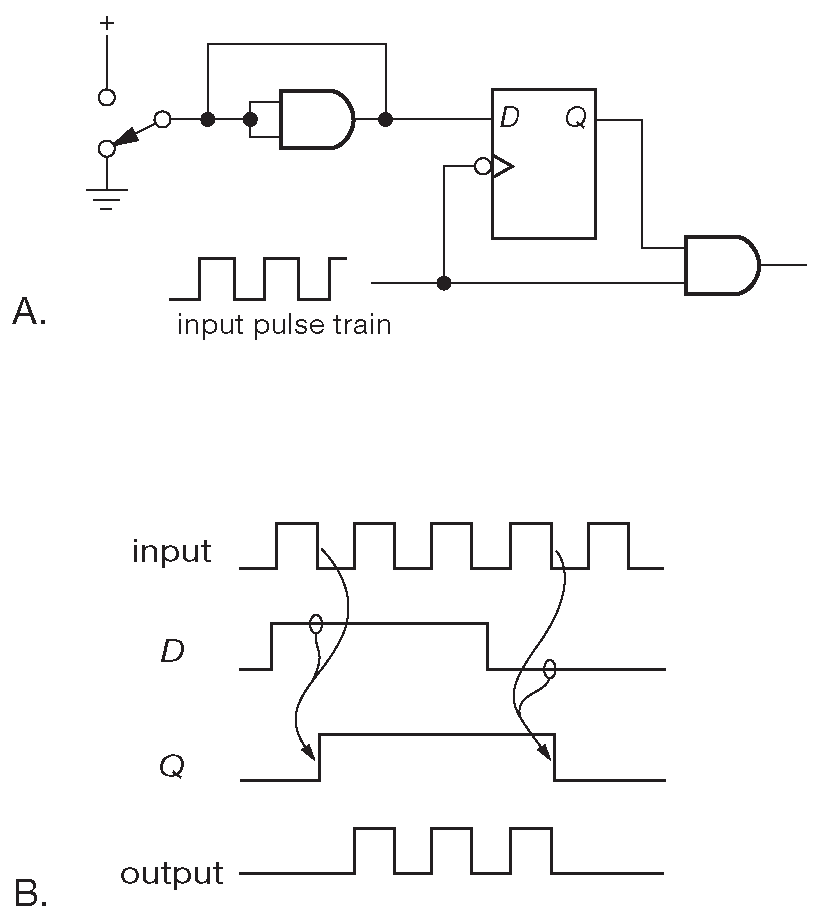

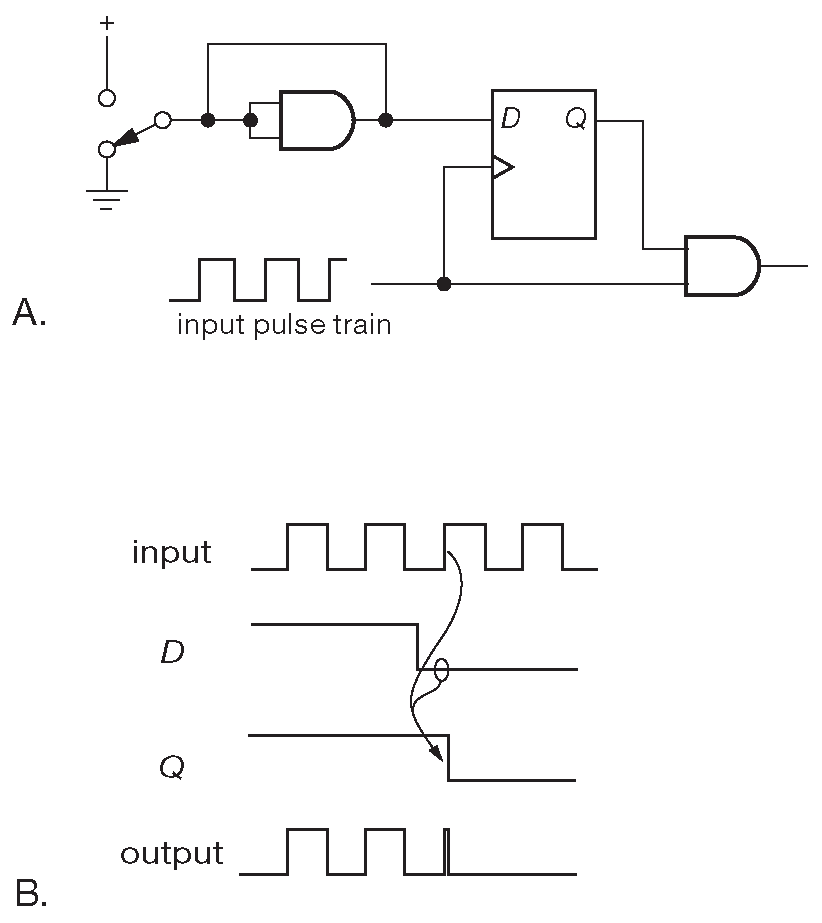

10.4.4.A Пример: синхронизатор импульсов

==738

В качестве примера вновь рассмотрим схему защиты от дребезга, которая включала и выключала линию тактирования ( рис. 10.51 , §10.4.1.A ). Схема переводила вентиль в разрешённое состояние, как только ключ замыкался, независимо от состояния тактового сигнала. Это создавало предпосылки для укорочения первого и последнего импульса. Проблема возникала из-за отсутствия синхронизации между ключом и импульсной последовательностью. Бывают ситуации, когда укорочение импульса недопустимо . В таких случаях требуется схема синхронизации, подобная 10.72 . Когда очищенный от дребезга сигнал с ключа приходит на вход «D» триггера, выход «Q» сохраняет прежнее состояние. Ситуация сохраняется до появления первого активного для триггера фронта на тактовой линии. Теперь через вентиль «И» проходят только целые импульсы. Изогнутые стрелки на временной диаграмме показывают последовательность событий. В частности видно, что изменение на выходе «Q» обусловлено состоянием «D» и происходит после прохода активного фронта.

Рис. 10.72 Синхронизатор импульсов. (A) Схема. (B) Временная диаграмма

10.4.4.B Логические гонки и неполноценные импульсы

Пример поднимает тонкую, но очень важную проблему. Что случится, если в схему поставить триггер, срабатывающий по восходящему фронту ? При аккуратном анализе станет ясно, что с началом тактового импульса [* восходящий фронт и немного после ] всё хорошо, но теперь неприятности переместились в конец импульса ( рис. 10.73 ). «Иголка» от нового фронта пробирается на выход, потому что выходная схема «И» остаётся открытой, пока выход триггера не перейдёт в НИЗКОЕ состояние, а произойдёт это только после задержки ( для серии «HC» - порядка 20 ns ). Налицо классический вариант логических гонок [* когда два сигнала соревнуются, кто быстрее доберётся до выхода ] . Проблему можно купировать, что и показывает пример 10.72 60 . Иголки, бегающие по схеме, - ужасная вещь. Помимо всего прочего малая длительность затрудняет их обнаружение осциллографом, и поэтому само их присутствие в схеме может оставаться в неизвестности. Они могут приводить к ошибочным переключениям триггеров, расширяться или сужаться до полного исчезновения при прохождении через цепочки логических элементов.

Рис. 10.73 Логические гонки могут порождать обрезанные импульсы ( “runt pulse” )

Упражнение 10.25

Покажите, что схема 10.72 иголок не создаёт.

Несколько замечаний о синхронизаторах. На вход данных триггера может идти сигнал не с ключа, а с другой логической схемы. Полно мест, скажем, в компьютерных интерфейсах, где асинхронный сигнал должен заводиться в тактируемую схему. В таких местах синхронизация на триггерах - идеальное решение. Неиспользуемые входы синхронизатора, как и в других логических схемах, должны подключаться к корректным логическим уровням. Например, «SET» и «RESET» должны быть в пассивном положении ( в ’74 это ВЫСОКИЙ, а в ’4013 - НИЗКИЙ уровень ). Входы, не влияющие на работу, можно подключать к любому логическому уровню.

==739

10.4.5 Моностабильный мультивибратор

В §7.2.2 было представлено устройство смешанных сигналов , собранное с использованием элементов аналоговой и цифровой техники, - моностабильный мультивибратор, также известный как «одновибратор» ( с упором на «одно-» ), см. табл. 7.3 на стр. 462 и табл. 7.4 на стр. 463 . Там же были выданы некоторые рекомендации, касающиеся их использования. Но существуют ситуации, когда одновибраторы - именно то, что требуется. Прервёмся, чтобы разобрать отличную иллюстрацию для этого тезиса - ждущий генератор импульсов.

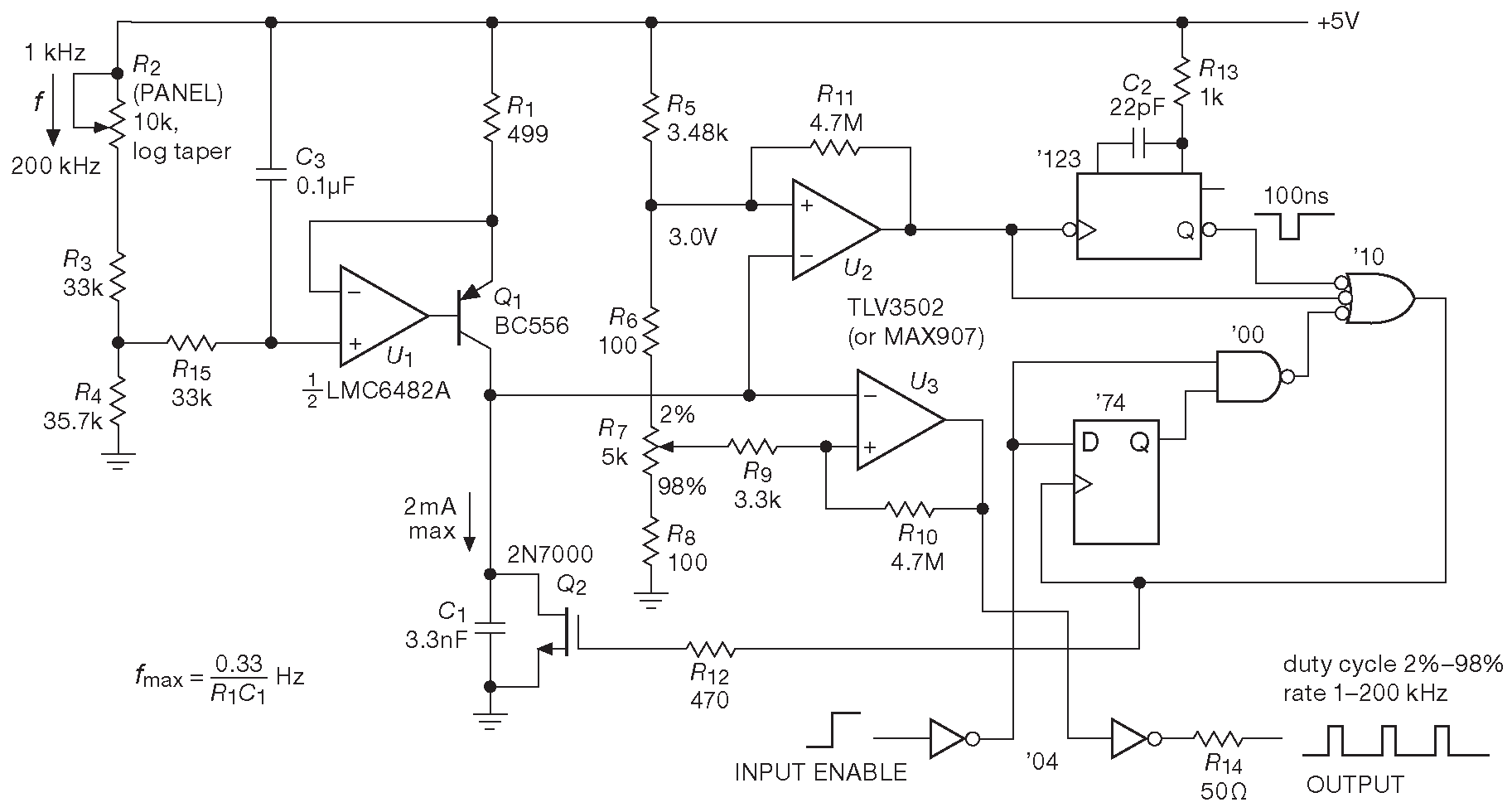

10.4.5.A Пример: ждущий генератор импульсов

На рис. 10.74 представлен генератор прямоугольных импульсов с независимой установкой частоты и скважности ( отношения ВЫСОКОГО состояния к периоду следования ). Входная схема позволяет запускать и останавливать выходную последовательность синхронно с внешним разрешающим сигналом. Источник тока \(U_1Q_1\) создаёт на \(C_1\) линейно меняющееся напряжение, скорость роста которого пропорциональна сопротивлению панельного потенциометра \(R_2\) . Когда напряжение на \(C_1\) достигнет порога компаратора \(U_2\) ( 3.0 V ), происходит запуск одновибратора и генерация импульса НИЗКОГО уровня длительностью 100 ns . Импульс открывает МОП ключ \(Q_2\) и разряжает \(C_1\) , приводя к появлению пилообразного сигнала с уровнями 0 и +3.0 V , частоту которого задаёт \(R_2\) . Компаратор \( U_3 \) превращает пилообразный сигнал в прямоугольные импульсы, длительность ВЫСОКОГО уровня которых плавно меняется от 2 до 98% резистором \(R_7\) . Оба компаратора имеют гистерезис несколько милливольт ( \(R_{10}\) и \(R_{11}\) ), позволяющий получить чистое переключение. TLV3502 - быстрый ( 4.5 ns ) сдвоенный КМОП компаратор с размахом входного сигнала, равным диапазону питания ( 0...5 V ), и RR выходами, см. табл. 12.2 на стр. 813 .

Рис. 10.74 Генератор импульсов, синхронизированных с запускающим сигналом. Вся логическая обвязка относится к КМОП серии «LVC»

Особенностью схемы является возможность синхронизации начала и конца выходной последовательности внешним управляющим сигналом. Вход «ENABLE» позволяет внешнему устройству запустить генератор с заданной фазой ( временем появления первого нисходящего фронта выходного импульса ) и остановить последовательность по окончании активного состояния выходного импульса.

Несколько дополнительных деталей.

- Дополнительный вход 3-входового «НЕ-ИЛИ» от компаратора \(U_2\) страхует от зависания схемы с полностью заряженным \(C_1\) .

- Длительность импульса одновибратора выбрана достаточно большой, чтобы гарантировать полный разряд \(C_1\) . Это время можно оценить, исходя из тока 2N7000 в режиме насыщения при напряжении на затворе 5V ( где-то 350 mA ) и сопротивление канала \( R_{ON} \) в конце разрядки ( 5 Ω ). Они дают две цифры 50 ns и 17 ns соответственно, из которых и выводится ( с запасом ) длительность 100 ns .

- 50-омный резистор на выходе обеспечивает «согласование источника» для 50-омного кабеля ( см. Приложение _H [* и §12.10 ] ).

- Схема построена таким образом, чтобы вершины пилообразного сигнала соответствовали самой низкой величине скважности. Дело в том, что в нижней части пилы наблюдается горизонтальный разрядный промежуток в 100 ns , а вершина имеет правильную форму.

- Частота генерации с хорошей точностью независима от вариаций напряжения питания, т.к. устанавливается логометрическим методом. Иначе говоря, и зарядный ток, и порог компаратора соотносятся в некоторой пропорции с одним и тем же питающим напряжением.

- Развязка для задающего частоту потенциала на входе \(U_1\) идёт на положительную шину питания, потому что именно она является опорным потенциалом для источника тока. На низкочастотной границе напряжение, подаваемое на \(R_{15}\) всего на 5 mV отличается от опорного уровня и очень чувствительно к шуму источника питания.

- Для \(R_2\) указана логарифмическая характеристика, потому что в противном случае низкочастотный конец диапазона слишком сильно сжимается.

10.4.6 Генератор одиночного импульса на счётчиках и триггерах

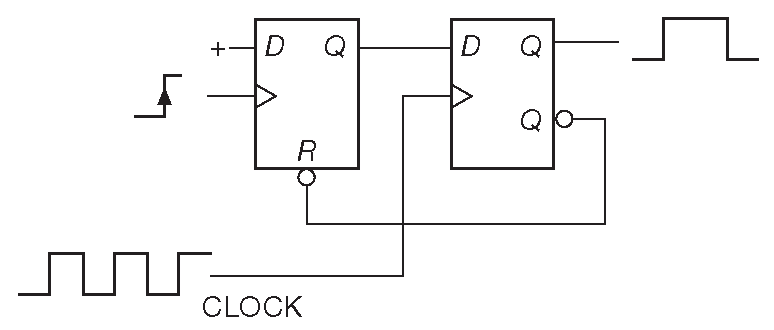

В §7.2.2 рассматривались методы получения одиночных импульсов и временнЫх задержек на одновибраторах, а также приводились некоторые предупреждения по использованию этих аналоговых отчасти устройств. Когда есть источник тактовых сигналов ( а сейчас это обычное дело ) можно собрать чисто цифровые варианты таких схем. На рис. 10.75 показано, как сделать свободный от иголок на фронтах одновибратор с длительностью импульса, равной периоду тактового сигнала. Не откажите себе в удовольствии, постройте временную диаграмму этой симпатичной схемы.

Рис. 10.75 Генератор одиночного импульса

Упражнение 10.26

Таки постройте её.

==740

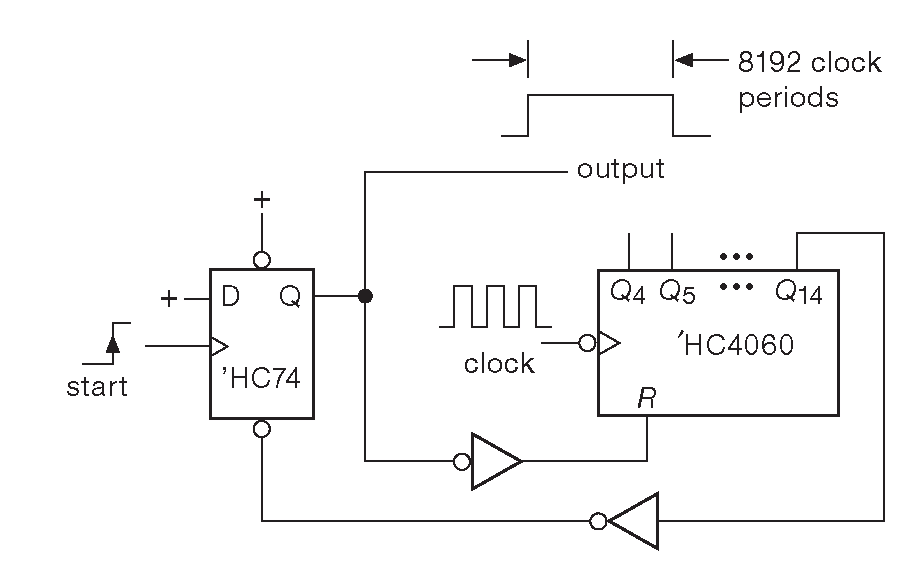

На рис. 10.76 показан другой вариант из триггера и счётчика [* более длинного, чем один разряд в схеме 10.75 ] , который можно использовать вместо аналоговых одновибраторов, чтобы получать длительные импульсы. ’4060 – «14-разрядный КМОП счётчик пульсаций» ( 14 последовательных триггеров ). Восходящий фронт сигнала START переводит выход D-триггера ’74 в ВЫСОКОЕ состояние, [* завершая состояние сброса ’4060 и ] разрешая работу счётчика. После 2n–1 тактовых импульсов его «Qn» перейдёт в ВЫСОКОЕ состояние и сбросит триггер и себя самого. Схема выдаёт точные импульсы, с выбором длительности по степеням 2 . ’4060 имеет внутренний генератор, который можно использовать для тактирования схемы, но детальное исследование показало, что точность его очень низкая, а в некоторых «HC» версиях он и вовсе не работает.

Рис. 10.76 Цифровой генератор длинных импульсов

Существуют законченные микросхемы, реализующие длительные задержки на счётчиках. ИМС ICM7240/50/60 фирмы Maxim содержат 8-разрядные двоичные или 2-разрядные десятичные/часовые делители и необходимую обвязку для получения задержек на целое число тактов входной частоты. Аналогичные возможности плюс предварительный делитель на 128 имеет ICM7242.

==740

44

Авторы предпочитают цеплять кнопку к земле, а не к шине +5V , по нескольким причинам.

(1) Земля удобный ( и «тихий» с электрической точки зрения ) путь возврата сигналов с переключателей и иных органов управления.

(2) Именно такой способ управления требовался биполярной логике, вход которой является источником вытекающего тока.

<-

45 Осторожные разработчики заменяют прямое соединение резистором, скажем 1 kΩ . Такой вариант исключает бросок тока при перескоке тумблера и возвращает проектировщику спокойный сон. [* См. рис. 12.16 и сопровождающий текст ] . <-

46 Эта расплывчатая формулировка может быть уточнена, что и будет сделано, когда произойдёт знакомство с понятиями время предустановки и время удержания в §10.4.2.C . <-

47 Или, возможно, несколько битов ( например, 8-разрядных данных ) набором D-триггеров в устройстве, называемом регистором . <-

48 Иногда неправильно называемые положительным фронтом и отрицательным фронтом соответственно. <-

49 Резкое изменение состояния буферного каскада, видимое на выходе, скрывает более интересную картину, когда внутренняя небуферированная схема балансирует на лезвии ножа между двумя уровнями, пытаясь решить в какое из них свалиться. <-

50 «Устойчивость к метастабильности» - это не то же самое, что «отсутствие метастабильности». Это как «водозащищённость» и «непромокаемость». <-

51 Серия LVC - самый лучший выбор для работы в диапазоне 1.8–3.3 V и, безусловно, самый быстрый вариант, см. рис. 10.26 . <-

52

Есть ещё две схемы для построения схем прямого счёта .

(1) Использовать выход «Q» предыдущего каскада как тактовый вход следующего, а «/Q» - в качестве внешнего вывода.

(2) Использовать выход «Q» для тактирования следующего каскада, срабатывающего по нисходящему фронту.

<-

53 По временнОй диаграмме видно, как из-за набегающей задержки между ступенями счёта текущее общее значение ( т.е. число, получаемое на вертикальном срезе временной диаграммы ) всегда некорректно. Данный факт можно не учитывать, если счётчик служит простым делителем частоты, или, если перед считыванием накопленного значения счёт останавливается. <-

54 Если всё, что требуется, - это просто входная частота, поделенная с некоторым коэффициентом, а взаимная фазировка входных и выходных сигналов не важна, счётчик пульсаций - вполне разумное решение. Он проще и работает с большей скоростью. <-

55 В примере нет входов управления, которые присутствуют, скажем, в счётчиках с изменяемым направлением счёта ( реверсивных ) или со сбросом. <-

56 Всегда доступен быстрый путь через таблицу переходов в ПЗУ. Кроме того, существуют программные средства, которые позволяют провести минимизацию и выдать схему на логических элементах. Но лучше всего использовать HDL ( языки описания аппаратуры для программируемой логики ), которые включают необходимые синтаксические конструкции, прямо предназначенные для задания состояний и условий для переходов. Такой способ не требует разрисовки логической схемы. <-

57 Их легко спутать. Возможно, полезна будет мнемоника “Moore--OutputsOnly” . <-

58 Здесь используется ABEL, а не более абстрактный Verilog, потому что первый «ближе к железу» и позволяет задавать входы, выходы и всё прочее. «$» означает операцию «ИСКЛЮЧАЮЩЕЕ-ИЛИ». <-

59 Хорошо, почти одновременно. На более глубоких уровнях разработки приходится заботиться о фазовых сдвигах - незначительных различиях во времени срабатывания у разных триггеров, работающих от общей линии тактирования. <-

60 Пример использует триггер, срабатывающий по нисходящему фронту, который трудно отыскать, но варианты под восходящий фронт создают на линии иголку. Что делать? Подумав немного можно дойти до правила исключения иголок. Уровень тактового сигнала, который разрешает логический элемент, должен идти перед фронтом, переключающим триггер . Хорошо, берём триггер, срабатывающий по восходящему фронту, и ставим инвертор на входе схемы «И». Появляется новая проблема - теперь в начале импульса. Потренируйтесь и попробуйте нарисовать схему, которая нормально работает с восходящим фронтом. <-