10.5 Интегральная логика последовательного действия

==740

Как и в случае комбинационной логики, стандартной практикой является размещение разных комбинаций триггеров и вентилей на одном кристалле с получением очередного представителя «стандартной логики». В следующих параграфах будет представлен краткий обзор наиболее интересных представителей. Но здесь следует вновь напомнить, что любые виды логических схем можно создавать с помощью программируемой логики ( Часть 11 ), которая поставляется в виде логических элементов определённого вида, связи между которыми задаются пользователем.

10.5.1 Защёлки и регистры

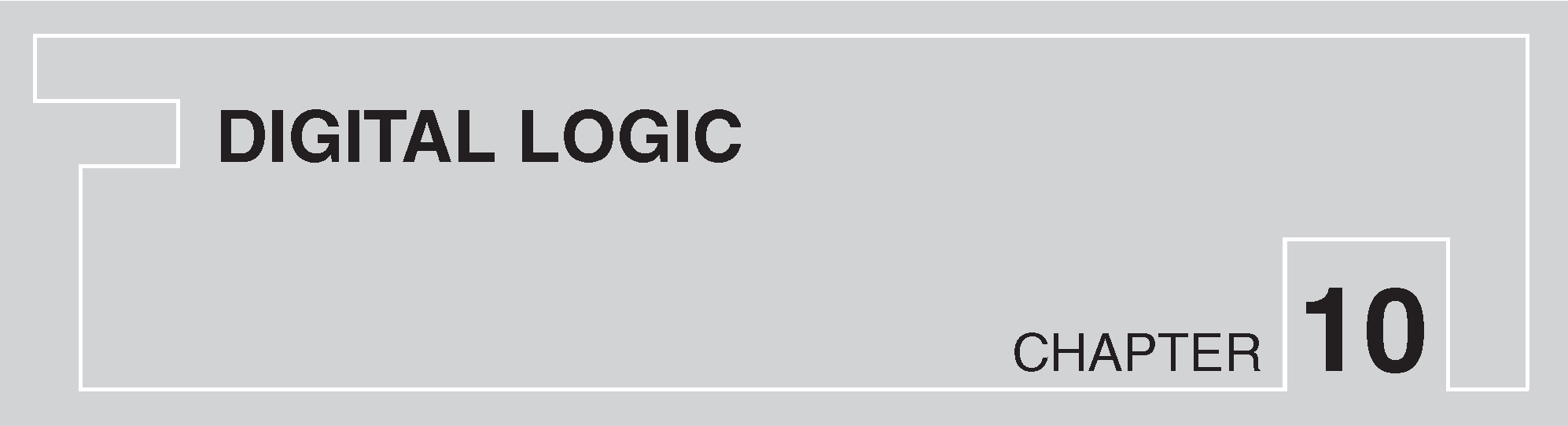

Защёлки и регистры используются чтобы «хранить» некоторую группу битов, даже если состояние источника данных изменилось. Регистр строится на D-триггерах, но обычный триггер имеет слишком много входов управления. Так как в регистре не нужны индивидуальные выводы тактирования и установки, эти линии можно запараллелить, уменьшив число служебных выводов и оставив больше места под линии данных. Благодаря таким мерам 8-разрядный регистр удаётся упаковать в 20-ногий корпус. Популярный регистр ’574 – «8-разрядный D-регистр, срабатывающий по восходящему фронту, с третьим состоянием». Очень похож на него ’273, но вывод переключения в третье состояние заменён сбросом. Если нужна большая разрядность, можно взять ’16374 ( 16 бит ) или ’32374 ( 32 бита ). На рис. 10.77 показан ’175 «счетверённый D-регистр с выходами обеих полярностей». Описание на Verilog для него приведено на рис. 10.78 .

Рис. 10.77 ’175 - 4-разрядный D-регистр

Рис. 10.78 Описание элемента ’175 на Verilog

// 4-bit D-register with true and complemented

// outputs, and with active-LOW asynchronous reset

reg [3:0] D;

reg [3:0] Q;

reg [3:0] QBAR;

wire CLKIN;

wire RESETBAR;

always @( posedge CLKIN or negedge RESETBAR )

if ( !RESETBAR ) begin

Q <= 4'b0000;

QBAR <= 4'b1111;

end

else begin

Q <= D;

QBAR <= ~D;

end

==741

Термин защёлка закреплён за особым видом регистров. Его выходы в разрешённом состоянии отслеживают состояние входов, а в запрещённом сохраняют последнее значение. Но из-за частых ошибок при использовании термина к нему добавили определение «прозрачная» . Например, ’573 – «8-разрядная прозрачная защёлка», а ’574 – «8-разрядный D-регистр с третьим состоянием» [* и в точности такой же разводкой ] . Есть 16-разрядные ’16373 и 32-разрядные ’32373.

Есть и другие виды регистров, как «D-», так и защёлок.

- ОЗУ ( RAM англ. «память с произвольным доступом» ), которое позволяет читать и записывать большой массив регистров, но только один из них в каждый момент времени. Микросхемы оперативной памяти в основном используются в качестве рабочей памяти микропроцессорных систем ( см. Часть 14 [* §14.4 ] ).

- Адресуемые или многобитные защёлки, позволяющие записывать отдельные биты, оставляя остальные без изменения.

- Защёлки и регистры, встроенные в более крупные микросхемы, например, аналого-цифровые преобразователи. Такие устройства требуют минимального времени ( срабатывания по фронту ) на подключение к шине и хранят данные в своих внутренних регистрах.

Выбирая D-регистры и прозрачные защёлки, обращайте внимание на наличие и состав входов управления и на линейную разводку ( входы с одной стороны, выходы с другой ). Такое расположение выводов облегчает разработку печатной платы.

10.5.2 Счётчики

Счётчики можно собрать на простой цепочке регистров, но проще подобрать что-нибудь среди огромного разнообразия интегральных вариантов, некоторые из которых попали в табл. 10.5 . Ниже даётся описание свойств, влияющих на выбор.

10.5.2.A Размер или разрядность

Самая многочисленная группа среди счётчиков - 4-разрядные двоичные ( шестнадцатеричные или «делители-на-16» ) и двоично-десятичные ( «делители-на-10» ). Есть счётчики и длиннее - до 24 разрядов, но не все из них доступны на выводах корпуса. Хороший пример - 74LV8154. Это пара синхронных 16-разрядных счётчиков с регистрами, отдельными входами тактирования и 8-разрядным буфером с третьим состоянием, на который можно вывести любой байт на выбор. Есть счётчики «по-модулю-n», где n задаётся на входных линиях. Для некоторых задач, где не нужны промежуточные биты, а просто требуется большой делитель, подходят микросхемы ICM7240-60, MC14541 и MC14536, см. §7.2.4.D . Все счётчики, включая синхронные, можно каскадировать с соответствующим увеличением разрядности.

10.5.2.B Тактирование

==742

Самое важное разделение счётчиков идёт по виду тактирования: на счётчики пульсаций [* они же «счётчики-делители» ] и синхронные. В первых каждая следующая ступень тактируется от предыдущей ( рис. 10.62 и 10.63 ), а в синхронном все триггера щёлкают одновременно. В счётчиках пульсаций на выходах кратковременно появляются неправильные переходные сочетания разрядов, потому что триггера, расположенные ближе к началу, переключаются раньше последующих. Скажем, счётчик пульсаций, меняющий состояние с «7»( 0111 ) на «8»( 1000 ) проходит через состояния «6»( 0110 ), «4»( 0100 ) и «0»( 0000 ). При правильном использовании это проблем не вызывает, но, если некая логика использует выходы счётчика, как руководство к действию, то правильно работать она не будет. Здесь может помочь промежуточный D-регистр, чтобы проверка счётчика выполнялась только после фиксирующего состояние фронта [* надо ещё правильно момент для фронта выбрать, чтобы не получить «0» вместо «8» ] . Показания счётчиков пульсаций успокаиваются после счётного события больше, чем синхронные, потому что новое состояние передаётся по цепочке, накапливая задержку. Зато они могут переключаться с большей частотой ( при одинаковой скорости триггеров ). Счётчики пульсаций срабатывают по нисходящему фронту для облегчения каскадирования ( просто выход последнего разряда подключается к тактовому входу следующей микросхемы ). Синхронные счётчики срабатывают по восходящему фронту.

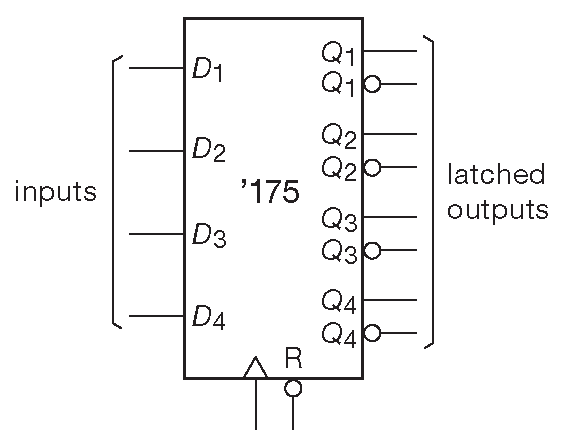

Авторы предпочитают синхронные модели ’160-’163 ( рис. 10.79 ). Это 4-разрядные счётчики, подходящие под любые задачи без особо хитрых требований. В выборку входят BCD и двоичные варианты с синхронным и асинхронным сбросом 61 . Их можно загружать с параллельной шины и просто каскадировать с помощью переноса и входов разрешения.

Рис. 10.79 Синхронные счётчики ’160-’163

10.5.2.C Реверсивные счётчики

Некоторые счётчики могут считать как вверх , так и вниз . Возможны два варианта управления:

- вход «U/D» , задающий направление счёта ( ’191 ) и

- пара тактовых входов - один «+1», а другой «–1» ( ’193 ).

Удобны 8-разрядные реверсивные модели ’579 и ’779.

10.5.2.D Загрузка и сброс

Большинство счётчиков имеют входные линии для загрузки начального значения. Это удобно, если требуется сделать счётчик «по-модулю-n». Операция загрузки может быть синхронной и асинхронной. В ’160-’163 она синхронная, т.е. данные будут загружены по следующему активному фронту тактового импульса, если линия «/LOAD» удерживается в НИЗКОМ состоянии. ’190-’193 имеют асинхронную загрузку «прямого действия» , т.е. данные загружаются в счётчик по сигналу LOAD, независимо от событий на тактовом входе. Иногда эта операция называется «параллельная загрузка», т.к. все биты пишутся в счётчик одновременно.

Table 10.5 Selected Counter ICsa Part number (74xxx) Supply voltage Bits w D o C o L_ -C o c >. CO U/D BCD Sync clear ^max DIP avail? min (V) max (V) min @ Vcc (MHz) (V) HC4024 2.0 6.0 7 no - - - 30 4.5 • HC4040 2.0 6.0 12 no - - - 30 5 • VHC4040 2.0 6.0 12 no - - - 150 5 - HC4060 2.0 6.0 14b no - - - 28 4.5 • LV4060 1.2 5.5 14b no - - - 99c 3.3 (•) HC40103 2.0 6.0 8 • D ’102 • 15 4.5 • 74HC161 2.0 6.0 4 • - ’162 ’163 30 4.5 • 74AC161 1.5 6.0 4 • - - ’163 90c 3.3 - 74LV161 2.0 5.5 4 • - - ’163 165c 3.3 - 74LVC161 1.2 3.6 4 • - - ’163 200c 3.3 - 74HC191 2.0 6.0 4 • • ’192 ’193 30 4.5 • 74AC191 1.5 6.0 4 • • - - 133c 5 - 74HC590 2.0 6.0 8d • - - - 33 4.5 • Notes: (a) all are binary, async reset, count up, unless otherwise marked. (b) no output pins for bits 0, 1,2, and 10. (c) typical. (d) with 3-state outputs.

==743

Операция сброса - это тоже один из вариантов параллельной загрузки. Большинство счётчиков имеет асинхронный сброс прямого действия, но есть и синхронные модели. Скажем, ’160 и ’161 имеют асинхронный сброс, а ’162 и ’163 - синхронный.

Повтор примера: «делитель-на-3»

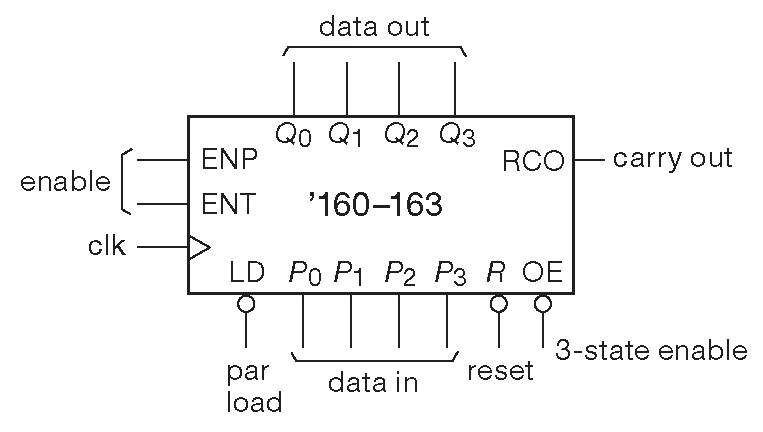

Задержимся ненадолго, чтобы разобраться с разницей между синхронным и асинхронным сбросом. Явных преимуществ нет ни у одного варианта, поэтому выбор определяется задачей. Но, скажем, четвёрка ’160-’163 включает оба варианта при одинаковой цене. Предположим, что требуется собрать «делитель-на-3» из синхронных счётчиков ’161 или ’163 ( эта же задача решалась ранее в §10.4.3.B ). Так как обе микросхемы считают только вверх, возьмём элемент «И-НЕ», чтобы ловить состояние «=3» и заведём его выход на активный низкий вход «/RESET». Получается, что мы проходим состояния «0», «1», «2», а на шаге «3» происходит немедленный сброс. Для такой схемы нужен элемент ’161 с асинхронным входом сброса ( рис. 10.80A ).

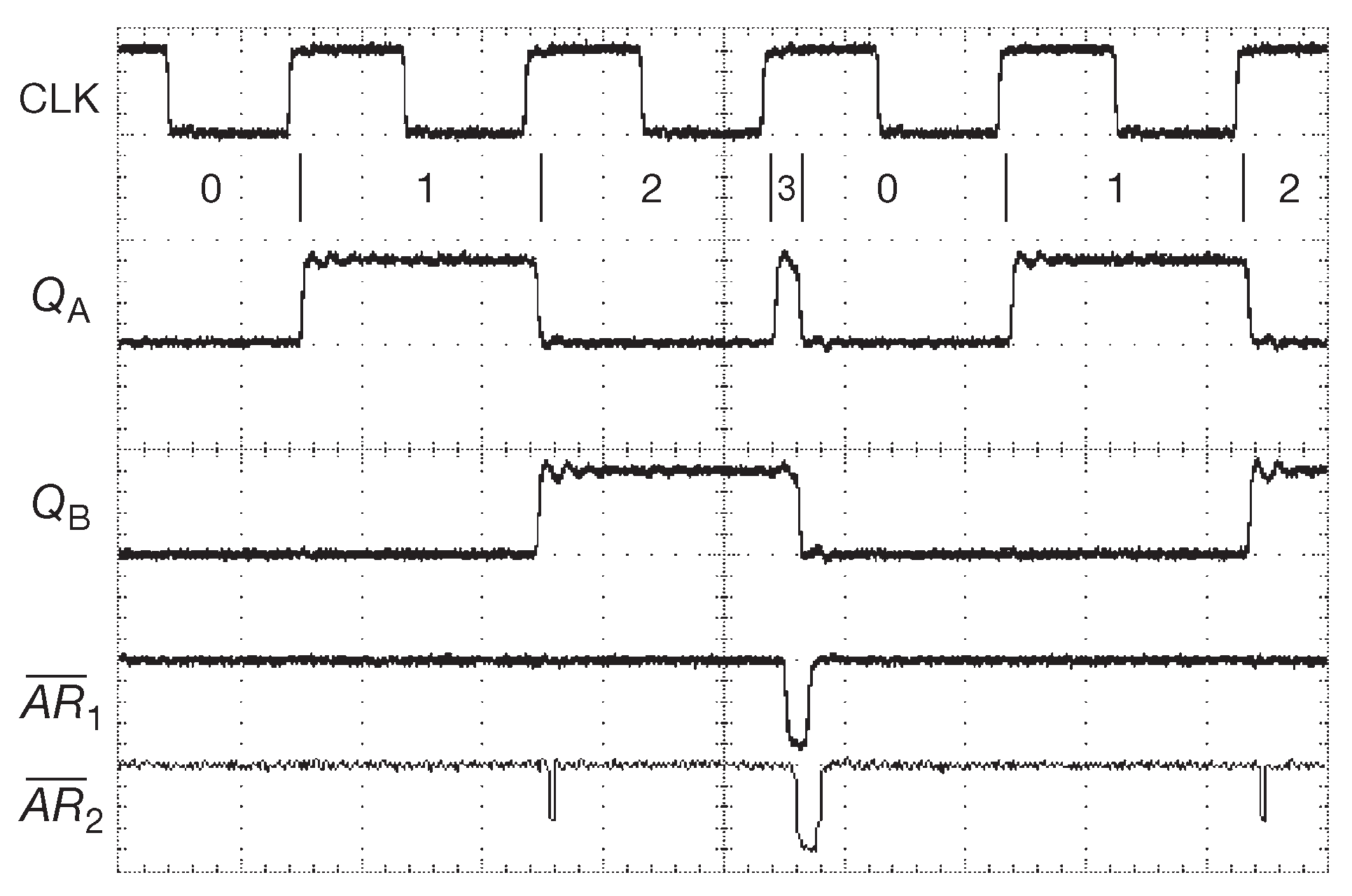

Рис. 10.80 Две схемы «делителя-на-3» из 4-разрядных синхронных счётчиков. (A) С асинхронным сбросом ( ’161 ). (B) С синхронным сбросом ( ’163 ). Схемы были собраны на ИМС серии «LV-A» с питанием +3.3 V . ВременнЫе диаграммы показаны на рис. 10.81 и 10.82

Схема, в общем, работает, но есть нюанс. Посмотрите на рис. 10.81 , на котором показаны результаты работы схемы на частоте 12 MHz . Хорошо видно, как счётчик проходит состояния «0», «1» и «2». Затем сразу после середины экрана происходит перескок в состояние «3» ( «QA» и «QB» оба ВЫСОКИЕ ) и одновременно на выходе схемы «И-НЕ» появляется сигнал сброса /AR1 , который сбрасывает счётчик. Проблема в том, что /AR1 деактивирует в том числе и сам себя: сброс счётчика выключает /AR1 . Получается, что импульс на входе сброса будет короче минимально допустимого, что приведёт к неполной инициализации триггеров микросхемы. [* Ну, типа, один триггер уже сбросился и выдал 0 , который выключает «И-НЕ», а второй ещё думает ] 62 .

Рис. 10.81 ВременнАя диаграмма работы «делителя-на-3» ( рис. 10.80A ). Помеха у сигнала /AR2 появляется в результате дополнительной емкостной нагрузки на выводе «QA» ( 39pF ). По горизонтали 40 ns/div , по вертикали 4V/div

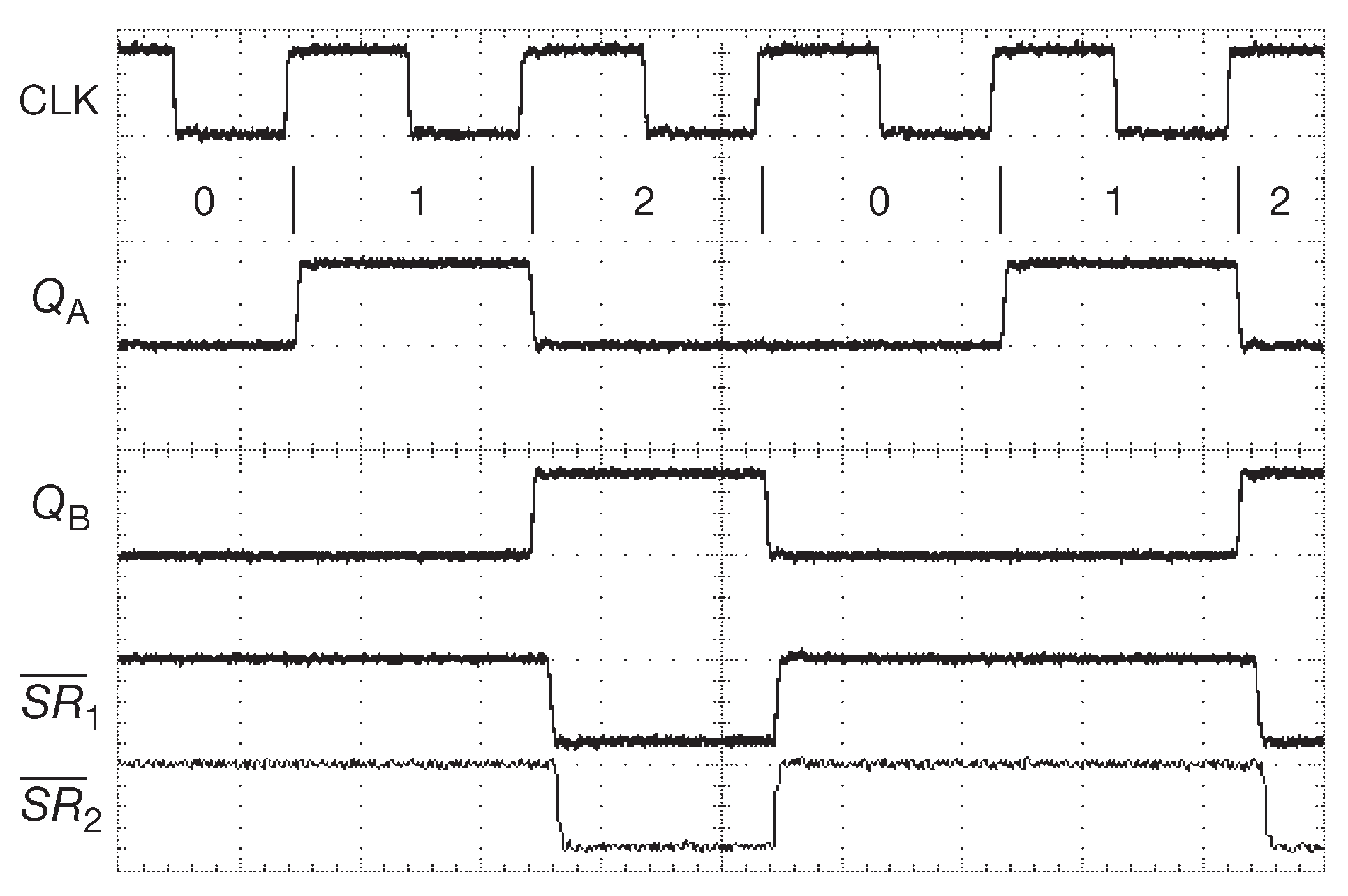

Рис. 10.82 ВременнАя диаграмма работы «делителя-на-3» по схеме 10.80B . Условия измерения как на рис. 10.81

Осциллограф выявляет ещё одну потенциальную опасность. Луч «/AR2» соответствует выходу схемы «И-НЕ» в ситуации, когда выход «QA» видит бОльшую емкостную нагрузку, чем вывод «QB» ( для измерения использовались 39 pF на землю ). Чуть задержанный «QA» пытается создать ложное состояние «3» при переходе «1»→»2». В данном случае условия для срабатывания недостаточны для преждевременного сброса счётчика, но это явный источник возможных проблем.

Синхронный сброс ( рис. 10.80B ) - более надёжный вариант. Счётчик сбрасывается восходящим фронтом, пришедшим после появления нужного уровня на выводе сброса. В таком случае требуется ловить состояние «=2», а не «=3» ( т.е. «n–1», вместо «n» ) 63 . ВременнАя диаграмма показана на рис. 10.82 . Иголок и укороченных импульсов на ней нет. Нет и при дополнительной емкостной нагрузке на выводе «QA» ( на диаграмме это сигнал «/SR2» ).

==744

Мы вернёмся к этой проблеме в §10.6.3 в приложении к генератору n-импульсной последовательности.

10.5.2.E Прочие опции счётчиков

Некоторые счётчики позволяют зафиксировать состояние на выходе с помощью прозрачной защёлки. В разрешённом состоянии счётчик ничем не отличается от обычного. Имейте в виду, что любой счётчик с параллельной загрузкой может защёлкивать состояние, но он не может при этом продолжать счёт, как модель с фиксацией. Комбинация из счётчика и регистра - достаточно удобна и позволяет работать с прежним значением, начав, например, новый цикл счёта. В частотомерах это позволяет избавиться от мерцания дисплея и не показывать каждый раз все числа от нуля до нового показания, но обновлять его после полного цикла измерения [* зато по счёту от нуля можно прикинуть интенсивность процесса ] .

Бывают счётчики с третьим состоянием на выходах. Такие ИМС удобны, когда данные надо выдавать на общую шину для отображения или передачи куда-либо. Можно назвать ’560/561, ’590 и ’779. Последний является 8-разрядным синхронным двоичным счётчиком с совмещёнными входами-выходами, что позволяет ужать корпус до 16 выводов, и третьим состоянием. ’593 похож, но имеет 20 ног. Если надо использовать счётчик в паре с индикатором, то можно взять комбинированную модель с защёлкой и драйвером 7-сегментного индикатора, например, 74C926 на 4 цифры 64 .

10.5.3 Сдвиговые регистры

Если соединить цепочку D-триггеров так, чтобы выход «Q» одного шёл на вход «D» следующего, а тактовые линии запараллелить, то получится сдвиговый регистр . В каждом такте последовательность нулей и единиц сдвигается, проходя от входа «D» первого триггера до выхода «Q» последнего. Как и в обычном D-триггере, данные, присутствующие на входах в момент прихода фронта, попадают на выход с задержкой распространения, поэтому схема может наращиваться без каких-либо побочных эффектов. Сдвиговые регистры требуются для преобразования параллельных данных ( n бит одновременно выставлено на n параллельных линиях ) в последовательные ( один бит за другим по одной линии ) и обратно. Как и счётчики, сдвиговые регистры бывают очень разные. Наиболее важные параметры поясняются ниже.

10.5.3.A Параметры

- Размер и организация

-

Стандартные длины - 4 и 8 разрядов, но есть варианты и длиннее ( 64 и более ) 65 .

Сдвиговые регистры обычно имеют ширину 1 бит, но встречаются и сдвоенные, счётверённые и сшестерённые. Большинство регистров сдвигает данные только в одну сторону, но встречаются и реверсивные ( ’194 и ’299 ).

- Входы и выходы

-

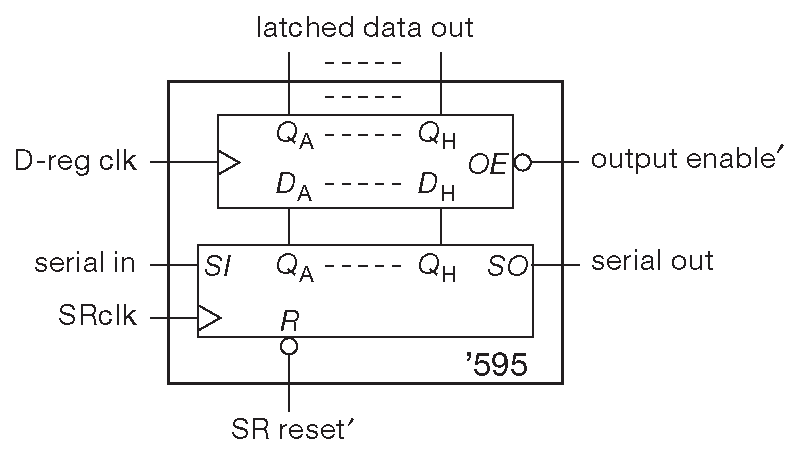

Небольшие регистры могут иметь параллельные входы или выходы и обычно таки имеют. Пример: ’395 – «4-разрядный сдвиговый регистр с параллельной загрузкой и чтением, с третьим состоянием выходов». Длинные регистры имеют только последовательную загрузку/чтение, например, вход и выход последовательных данных плюс некоторые отводы от промежуточных узлов. Единственным способом совмещения параллельной загрузки/чтения является мультиплексирование линий данных ( наличие третьего состояния ). Например, ’299 - 8-разрядный регистр в 20-ногом корпусе. Некоторые сдвиговые регистры имеют защёлки на параллельных линиях, что позволяет продолжать сдвиг пока данные считываются или загружаются. Очень хорошим примером служат ’595 - 8-разрядный сдвиговый регистр ( рис. 10.83 ), доступный во множестве семейств ( «AHC(T)», «F», «ACT», «HC(T)», «LV», «LVC» и «VHC» ). Его очень удобно использовать для распараллеливания длинного последовательного слова от микроконтроллера 66 . Дополняет такую задачу ’597 - 8-разрядный сдвиговый регистр с параллельной загрузкой, позволяющий передать данные в микроконтроллер через одну последовательную линию.

Как и у счётчиков, сигналы загрузки и очистки могут быть и синхронными ( ’323 ) и асинхронными ( ’299 ).

Рис. 10.83 ’595 - 8-разрядный сдвиговый регистр с выходной защёлкой. Удобная ИМС для получения дополнительных линий управления в малоногом микроконтроллере. TPIC6595 - вариант с открытым стоком на выходах ( до 45V и 250 mA )

==745

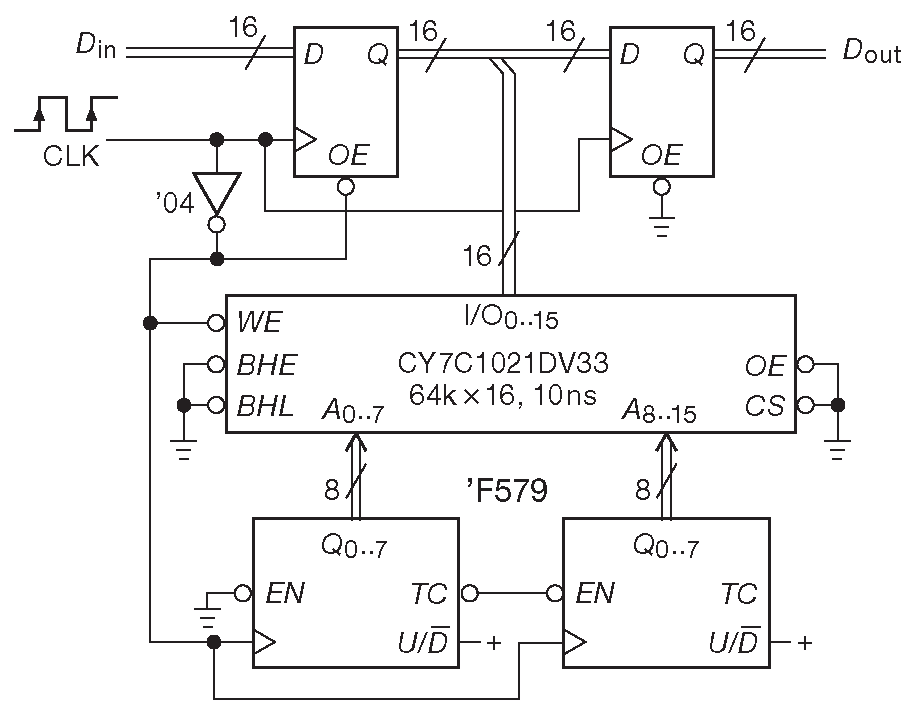

10.5.3.B ОЗУ в качестве сдвигового регистра

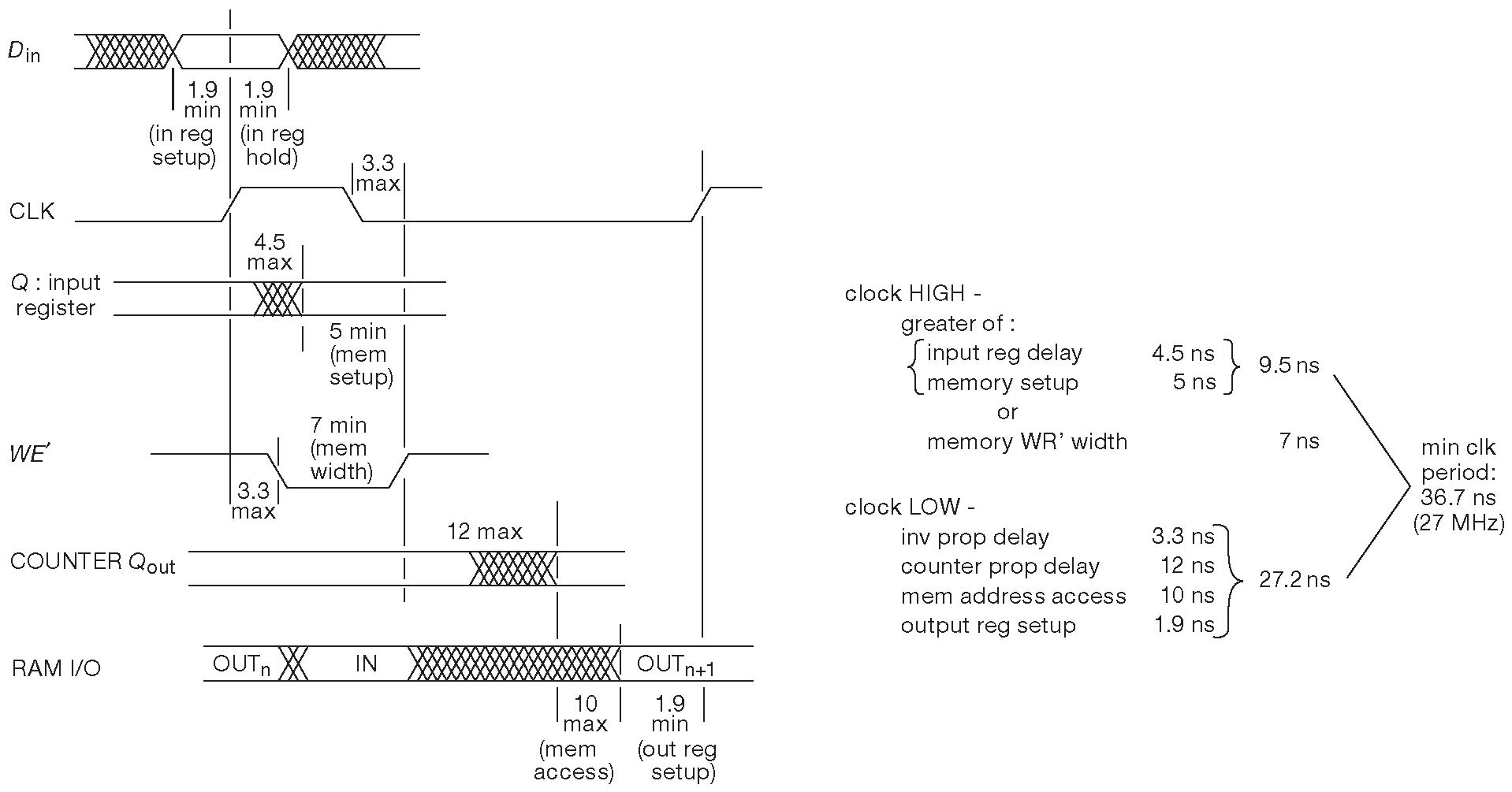

Микросхемы оперативной памяти можно использовать в качестве сдвиговых регистров ( обратный вариант невозможен ). Потребуется внешний счётчик адреса. Идею иллюстрирует рис. 10.84 . Пара каскадированных 8-разрядных синхронных счётчиков выдает последовательные адреса для массива статической памяти 64k×16 . Такая комбинация работает как сдвиговый регистр длиной 65536 слов 16-разрядной ширины. Комбинация из быстрых счётчиков 67 и ОЗУ позволила достичь скорости 27 MHz ( см. временнУю диаграмму на рис. 10.85 ), которая сравнима со скоростями мелких сдвиговых регистров из стандартной логики. ( Полезно, кстати, повторить вычисления. Это хороший пример на учёт времени предустановки и удержания, распространения и доступа к памяти ).

Рис. 10.84 Длинный и широкий сдвиговый регистр, собранный на ИМС оперативной памяти и счётчиках. Наклонная черта ( слэш ) отмечает параллельные линии. В данном случае 16-разрядная шина данных и две 8-разрядные шины адресов дают в итоге 65536 слов шириной 16 бит

Рис. 10.85 ВременнАя диаграмма работы сдвигового регистра на микросхемах оперативной памяти ( рис. 10.84 ). Для самого неудачного сочетания временных параметров скорость тактирования составила 27 MHz

Упражнение 10.27

Похоже, на схеме 10.84 выходные данные идут из той же ячейки памяти, в которую пишутся входные. Но схема работает как обычный сдвиговый регистр на 65536 элементов. Объясните как такое возможно.

10.5.4 Программируемые логические устройства

Проектирование цифровых устройств неуклонно смещается в сторону программируемых пользователем микросхем, содержащих от сотен до сотен тысяч вентилей и триггеров 68 , связи между которыми задаёт пользователь. Проектирование ведётся на языке описания аппаратуры, проходит программную обработку с получением файла связей и загружается в микросхему через последовательный интерфейс ( обычно JTAG ). В Части 11 этот процесс расписан подробнее, но будет неправильно завершить данную часть без краткого анонса.

10.5.4.A Минусы

Перед использованием этих микросхема придётся изучить язык описания аппаратуры Verilog или VHDL. Потребуется программирующий адаптер или иное устройство для загрузки микросхемы. Наконец, все эти микросхемы упакованы в корпуса для поверхностного монтажа, затрудняющие макетирование.

10.5.4.B Плюсы

Можно обойтись без HDL и нарисовать схему в программе «схемного ввода». Такие пакеты поставляются как производителями микросхем, так и сторонними производителями ( §11.3.3.A ). Вдобавок, для многих задач программируемая логика является настоящей палочкой- выручалочкой. Приведём самые известные.

- Машины состояний

- ПЛМ - естественная площадка для построения синхронных машин состояний. Глупо набирать горсть триггеров и микросхем жёсткой логики, когда компактный и недорогой программируемый кристалл сделает всю работу в одиночку.

==746

- Замена «жёсткой» логики

- Во многих схемах можно найти скопления вентилей, триггеров, счётчиков, кратко именуемых именуемой «жёсткой» логикой или «логической обвязкой» . Программируемые микросхемы могут уменьшить число корпусов более чем на порядок.

- Универсальность

- Иногда бывает, что в ходе разработки возникает какая-нибудь шероховатость, которую хотелось бы подкорректировать, но сроки вынуждают завершать работу «как есть». Программируемая логика позволяет вернуться к проекту позднее и переделать начинку, не трогая внешней разводки, что было бы невозможно с жёсткой логикой. С ПЛМ схема становится формой программы 69 .

- Возможность модификации

- ПЛМ позволяет собрать устройство, а затем выпускать его другую модификацию, просто изменив микропрограмму.

- Комплектование и скорость разработки

- Программируемая логика позволяет не только быстрее вести разработку, но и сократить число складских позиций, заменив десятки наименований микросхем средней степени интеграции одним чипом ПЛМ.

- Система на кристалле ( SOC )

-

Большие микросхемы программируемой логики ( например, вентильные матрицы ) имеют внутри достаточно ресурсов для размещения всего проекта целиком. В частности они позволяют использовать стандартные интерфейсы ( Ethernet, USB и пр. ), память и даже процессор внутри одной вентильной матрицы. В этом направлении ведут два пути.

- Если требуемая функция добавляется в исходный текст на HDL с последующим превращением в связи внутри массива триггеров и вентилей, то это «программная реализация» . В неё можно включать функциональные блоки, полученные из какого угодно источника. Такие куски кода называются «интеллектуальной собственностью» ( IP ).

- Такие функции могут быть внутри микросхемы в виде аппаратных блоков ( в этом случае их нельзя изменить ). Это «аппаратная реализация» . Подробности в Части 11 .

10.5.5 Прочая логика последовательного действия

Непрерывный прогресс полупроводниковой индустрии, которая в рабочем порядке размещает миллионы транзисторов на одном кристалле 70 , позволяет создавать сложные и удобные устройства в одной недорогой микросхеме. Некоторые из них упомянуты ниже просто для примера.

==747

- Память «первым-вошёл-первым-вышел»

-

Микросхемы памяти вида «первым-вошёл-первым-вышел» ( FIFO ) чем-то похожи на сдвиговые регистры, в которых данные, поступившие на вход, приходят на выход в той же последовательности. Важное различие заключается в том, что по сдвиговому регистру информация продвигается по мере поступления на вход нового слова в сопровождении тактового импульса. В FIFO данные проваливаются на выход сразу. Запись и чтение управляются различными сигналами [* и может идти с разной скоростью - это их основное назначение ] . FIFO отслеживает лишь, сколько поступило на вход и сколько прочитано на выходе 71 .

FIFO используют для буферизации асинхронных данных. Классический пример - буфер клавиатуры ( или любой другой источник данных: магнитный диск или быстрый сетевой порт ) в компьютере или неторопливом приборе. С FIFO нет потери данных, даже если компьютер не готов отвлекаться на новый байт, как только тот появится. С буфером надо просто избегать переполнения. Популярная универсальная серия 7201—7206 - линейка микросхем с шиной 8 разрядов. Отличаются глубиной. 72V01—72V06 - КМОП FIFO с питанием +3.3 V , шириной 9 разрядов и глубиной от 0.5 до 16k слов. Максимальная скорость 40 MHz и нулевое время прохождения на выход ( этим они сильно отличаются от старых схем на основе сдвиговых регистров ). Бывают двунаправленные FIFO [* две очереди, направленные встречно, в общем корпусе ] , синхронные и широкие ( до 72 бит ).

FIFO не нужен, если устройство, которому передаются данные, успевает их забрать до прихода новой порции. На компьютерном языке это значит, что максимальная латентность меньше минимальной задержки между элементами данных. Отметим, что, если приёмник не способен работать со средней скоростью поступления данных, то FIFO ему не поможет.

[* Т.е. представим ситуацию, при которой приёмное устройство спит сладким сном в течение года, а источник раз в неделю отправляет байт данных в FIFO глубиной 54 элемента ( скорость передачи 1 байт в неделю ). Если приёмник, хорошо погуляв на встрече 2020 года, очнётся на майских праздниках 2021 ( 70 недель ), то обнаружит, что часть данных потеряна ( скорость приёма 54/70=0.77 байт в неделю ). Отказываться от алкоголя в такой ситуации - не вариант. Надо просто увеличить глубину буфера ].

- Цифровые вольтметры

- В одном кристалле можно собрать законченный цифровой вольтметр ( DVM ). Кстати, на торговых площадках такие чипы можно обнаружить в разделе «драйверы дисплеев» . Он будет включать источник опорного напряжения, высокоимпедансные дифференциальные входы, драйвер ЖКИ и ещё по мелочи. Примером может служить MAX1495 - интегрированный 4.5-знаковый вольтметр в корпусе 7×7 mm . Он потребляет порядка миллиампера от одного источника 3...5 V . Популярна ИМС ’7135 ( Intersil и Maxim зовут её ICL7135, Microchip - TC7135, а TI - TLC7135 ). Это 4.5-знаковый вольтметр, работающий с 7-сегментными светодиодными индикаторами от +5V . ’7136 - 3.5-знаковый вольтметр под 7-сегментные ЖКИ.

- Устройства специального назначения

- Это отличная коллекция из БИС ( микросхем большой степени интеграции ) ( LSI ), которые дополняют очень сложные задачи. В их число входят радиосвязь ( например, синтез частоты ), цифровая обработка сигналов ( цифровые фильтры, корреляторы, схемы быстрого преобразования Фурье ), последовательная передача данных ( UART, модемы, сетевые интерфейсы, преобразователи последовательных протоколов ) и т.д. Такие ИМС используются в связке с микроконтроллером и не способны работать в одиночку.

- Потребительский рынок

- Полупроводниковая индустрия любит делать микросхемы для массового потребительского рынка. Здесь можно найти однокристальные часы, калькуляторы, детекторы задымления, музыкальные синтезаторы и т.д. Корпуса современных радио- и телеприёмников, проигрывателей дисков и т.п. стоят почти пустые: спасибо современным БИС. Задачи синтеза и распознавания речи превратились в рутинную деятельность, и теперь GPS навигатор может понимать голосовые команды и говорить сам 72 . Автомобили набиты десятками процессоров, управляющих двигателем, тормозами, навигацией и т.д. Даже зубная щётка имеет процессор с парой тысяч строк кода 73 .

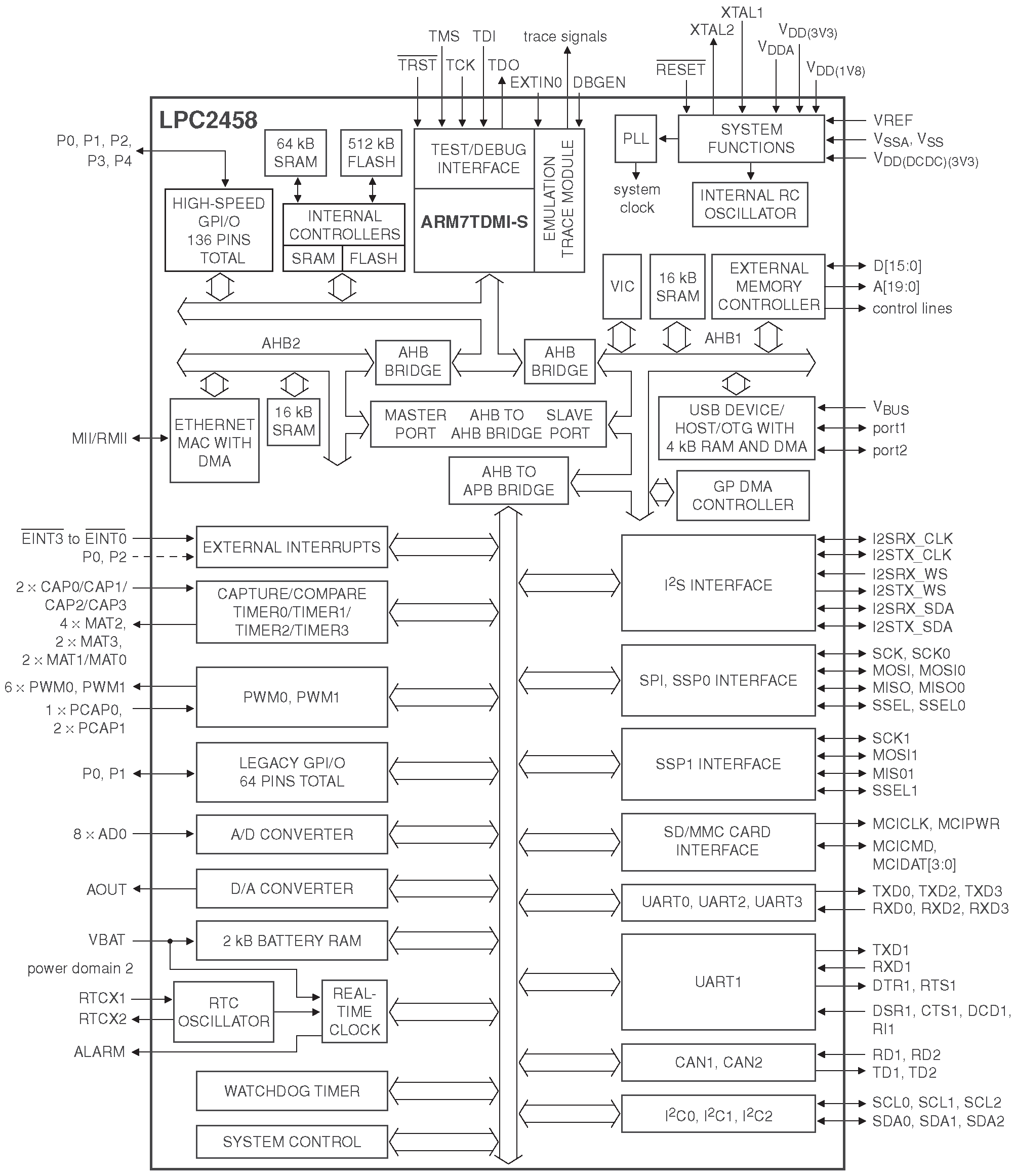

- Микропроцессоры

- Наиболее впечатляющим примером возможностей СБИС ( сверхбольших интегральных схем ) ( VLSI ) являются микропроцессоры - однокристальные компьютеры. На одном полюсе находятся «числомолотилки», типа восьмиядерного Itanium фирмы Intel с 3 миллиардами транзисторов на борту, с сотнями внутренних регистров, поддержкой петабайт памяти и возможностью групповой работы в 512-разрядной конструкции. На другом полюсе - недорогие кристаллы для полностью автономной работы. На рис. 10.86 показан пример - ARM7 LPC2458 фирмы NXP ( бывшей Philips ): 512kB/64kB памяти, 72 MHz , 10/100 Ethernet, USB 2.0, 10-bit A/D и D/A, 2×PWM, 4×UART, 2×CAN, SPI, 2×SSP, 3×I2C, I2S, 136 линий ввода-вывода общего назначения и контроллер внешней памяти. Стоит около $10 74 . Такие процессоры предназначены для задач управления, а не вычислений общего вида.

==749

Рис. 10.86 Анонс для Части 15 . Недорогой микроконтроллер, набитый массой интересных вещей. Вытащено из документа LPC2131_32_34_3638_4 ©NXP B.V 2007

==748

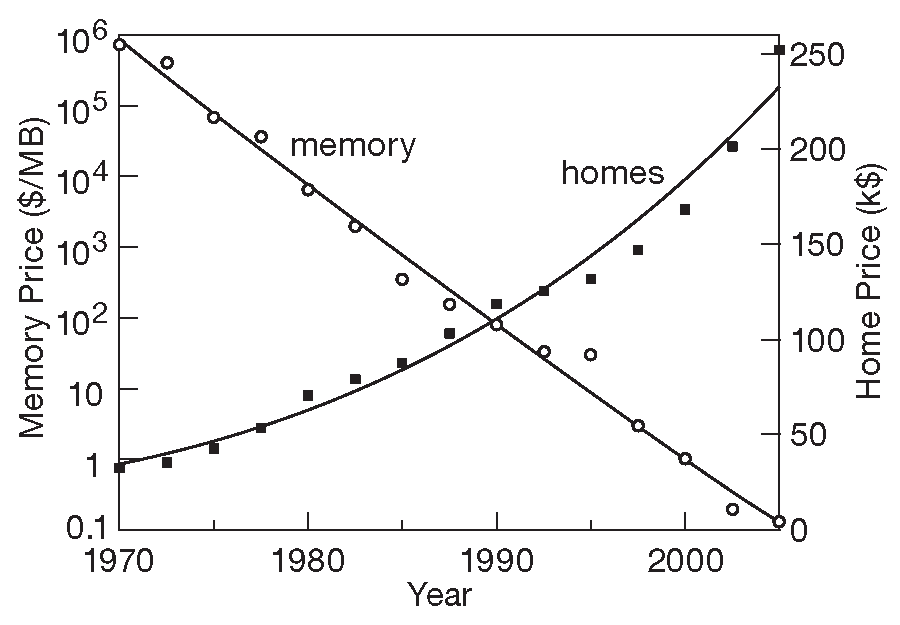

- Микропроцессорная революция и не думает замедляться, по-прежнему показывая удвоение вычислительной мощности и объёмов памяти каждые 18 месяцев ( сейчас это 8Gb на чип, при написании второй редакции было 1Mb , а первой - 16kb ) ( «закон Мура» ). Цена при этом катастрофически упала ( рис. 10.87 ). Ближайшие годы обещают новые удивительные события в области процессоров, памяти, устройств отображения и передачи данных.

Рис. 10.87 Закон кремниевой долины. 35 лет компьютерная память дешевеет в два раза каждые 18 месяцев. Для сравнения медианная стоимость новых домов в США много десятилетий соответствует кривой экспоненциального роста. ( Последние события показывают опасность самонадеянного предположения о продолжении такой тенденции )

==748

61 Если вход «/R» в активном состоянии, то счётчик с синхронным сбросом дождётся следующего активного фронта, который уже проведёт сброс, а счётчик с асинхронным сбросом обнулится одновременно с сигналом на «/R», независимо от событий на тактовом входе. <-

62 Счётчик работает хорошо, но вы же не хотите, чтобы маленькие острые иголки бегали по схеме, правда? <-

63 Вообще-то для синхронного сброса достаточно было инвертировать «QB» и подать его на «/SR», полностью игнорируя «QA» ( а почему? ). Но для ясности было решено проводить полное декодирование состояния QA=0 И QB=1 ( сигнал /SR1 ) . <-

64 Не без горечи было принято решение исключить из рассмотрения необычный TIL306/7 - счётчик с индикатором на корпусе. Чтобы узнать счёт достаточно взглянуть на микросхему! Другой отличный пример - ICL7216 фирмы Intersil – «8-знаковый универсальный счётчик на кристалле» ( 10 MHz , встроенный драйвер для 7-сегментных индикаторов ). Он получил свою долю славы во втором издании на стр. 526, но ныне снят с производства. Такую функцию можно собрать самостоятельно в вентильной матрице или ПЛМ ( см. Часть 11 ). Фирма Maxim до сих пор выпускает ICM7217 – «4-знаковые реверсивные счётчики с мультиплексным драйвером светодиодного индикатора» и ICM7218/7228 - 8-символьные драйверы светодиодных индикаторов. <-

65 Есть даже регистр переменной длины ’4557. Он может менять длину от 1 до 64 ступеней. Размер выбирается 6-битным кодом на выводах управления. <-

66 Микроконтроллеры рассматриваются в Части 15 , где будет приведён пример такой конструкции. <-

67 ’579 есть только в 5-вольтовой логике. Остальная схема питается от +3.3 V , но, т.к. вся логика является 5V-совместимой ( см. §12.1.2.A ), проблем с передачей сигнала не возникает. <-

68 Иногда поддержанные специализированными микросхемами типа ОЗУ, передатчиков и процессоров. <-

69 Правильнее микропрограмма - что-то среднее между слишком статичной аппаратурой и слишком изменчивыми программами. <-

70 Миллиарды в больших процессорах ( CPU ), графических чипах ( GPU ) и вентильных матрицах ( FPGA ). <-

71 FIFO можно реализовать программным способом, повторив в коде идеи аппаратной реализации. Для этого в ОЗУ надо завести кольцевой буфер и пару указателей для записи и чтения. <-

72 Один из авторов, будучи ребёнком, улучшил говорящую Nissan Maxima, нанятую на лето, чуть увеличив её словарный запас. Замене подверглись выражения типа «дверь не заперта», «бак пуст» и т.д. Новый вариант звучал «вы едите в динозавра». <-

73 Взгляните на MC9RS08KA фирмы Freescale Semiconductor. Он имеет внутри генератор на 10 MHz и 2kB памяти, будучи при этом «маленьким настолько, что может поместиться в голове электрической зубной щётки» и предназначен для «решения проблем ухода за собой». Стоит менее $0.40 в количествах. <-

74 LPC1768 фирмы NXP - малопотребляющий кристалл, активно используемый при прототипировании. Он обладает почти всеми возможностями LPC2458, кроме контроллера внешней памяти. Число линий ввода-вывода сократилось до 70 ( выразим надежду, что это не будет слишком жёстким ограничением ). Удобный для пайки 100-ногий корпус QFP с шагом 0.5 mm . Отметим 12-разрядный АЦП, 10-разрядный ЦАП и 6 каналов PWM общего назначения. <-