14.4 Типы памяти

==1014

В §14.1.2 упоминалось, что компьютеру нужна быстрая память со «случайным доступом» ( т.е. такая, в которой доступ к конкретному элементу памяти не требует перемотки носителя, как это происходит в устройствах с последовательным доступом - ленточных накопителях ). Такая память чаще всего имеет вид модулей динамической оперативной памяти . Это тонкие узкие печатные платы о 240 контактах, которые вставляются в слоты памяти на материнской плате. В настоящее время активнее всего используется форм-фактор SODIMM с размерами 3×13.3 cm , заполненный микросхемами памяти общей ёмкостью, исчисляемой гигабайтами. Шина данных в таких сборках может иметь ширину 64 или 72 разряда. Это компоненты, обычно встречающиеся на коммерческих материнских платах. Требуется просто подобрать нужную модель памяти 26 , для чего приходится изучать справочные данные на материнскую плату и спецификации предложений от фирм Corsair, Crucial, Kingston.

Но, если хочется разобраться в том, как это всё работает, или требуется спроектировать вычислительную систему, использующую внешнюю память, потребуется разобраться в том, как память работает. В этой главе разбираются различные виды памяти: статическая и динамическая оперативная, а также постоянная, включая «флэш-ОЗУ».

14.4.1 Постоянная и оперативная память

==1015

Во многих задачах память, сохраняющая записанные в неё данные при пропадании питания, не нужна. Скажем, компьютер каждый раз заново грузит в рабочую память операционную систему, приложения и данные в ходе начальной инициализации. Здесь отлично работает обычная оперативная память. Сами приложения, операционная система и исходные данные должны, понятно, где-то храниться, пока питание выключено. Именно для таких задач используется постоянная память. Обычно это накопители в виде жёстких дисков ( с вращающимся магнитным носителем ) или твердотельных дисков ( название «диск» перешло по наследству, а физически такое хранилище выглядит как набор микросхем флэш-памяти ) 27 . Оперативная память быстрее, имеет большую ёмкость, ресурс ( количество циклов стирание-запись до появления ошибок ) и цену за единицу информации, если сравнивать с современными технологиями постоянной памяти. Оба вида оперативной памяти - и статическая SRAM, и динамическая DRAM – «помнят» записанные в них данные, пока есть питание 28 , а флэш и EEPROM ( а также некоторые современные технологии ) позволяют хранить информацию и в его отсутствие.

14.4.2 Статическая и динамическая память

Статическая память хранит данные в массиве триггеров, а динамическая - в виде заряда на конденсаторе. Бит данных, записанный в статическую оперативную память, будет храниться в ней, пока его не перезапишут, или пока не отключится питание. В динамической памяти данные исчезают примерно за секунду, если их не «освежать». Иначе говоря, DRAM всегда пытается забыть данные, и предотвратить это можно только периодическим обращением ко всем рядам двухкоординатного массива элементов хранения. Например, в DRAM объёмом 1 Gb надо обращаться к каждому из 8192 рядов каждые 64 ms ( т.е. 1 ряд в 7.8μs ).

Вы, возможно, захотите узнать, почему вообще находятся желающие использовать динамическую память? Дело в том, что отсутствие триггеров существенно увеличивает плотность хранения информации и в десятки раз снижает стоимость единицы объёма.

Теперь вы недоумеваете, кому вообще нужна статическая память? ( В «динамичности» вам не откажешь ). Основным преимуществом SRAM является простота использования: нет ни циклов регенерации, ни забот о временных соотношениях сигналов ( циклы регенерации конкурируют с обычными циклами обращения и требуют корректной синхронизации ). Поэтому для небольших систем с несколькими микросхемами памяти SRAM будут удобнее. Нулевое потребление статической памяти в отсутствие обращений делает её естественным выбором в батарейных устройствах ( у DRAM имеется существенный динамический ток холостого хода из-за постоянной регенерации ). Существует даже статическая память со встроенной батарейкой, которая продолжает сохранять данные в отсутствие внешнего питания. Она может служить альтернативой обычной постоянной памяти при существенно лучших параметрах скорости доступа и без ограничения числа циклов стирания-записи. Ещё одним достоинством является наличие очень быстрых асинхронных версий с временем доступа менее 8 ns и синхронных вариантов с тактовой частотой 400 MHz и более. Есть, наконец, и псевдостатическая память PSRAM, которая сочетает низкую стоимость и высокую плотность DRAM с простым интерфейсом SRAM ( это динамическая память со встроенным модулем регенерации ). Разберём их все подробнее.

==1016

14.4.3 Статическая память

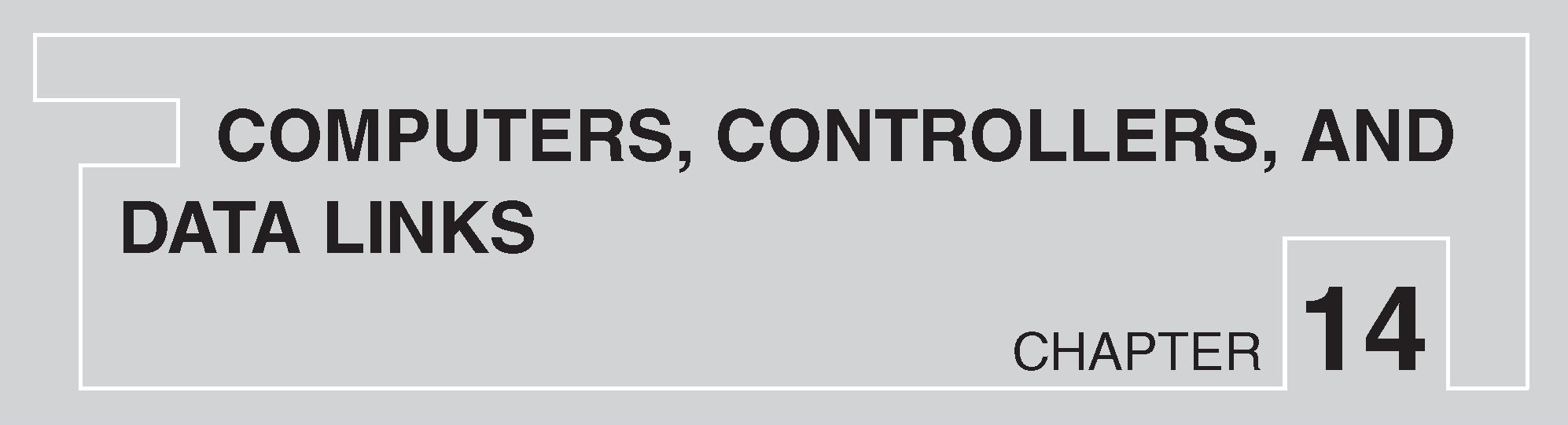

Статическая память сохраняет каждый бит в триггере ( рис. 14.20 ). Сам триггер состоит из двух встречно-параллельных инверторов, собранных на комплементарных p- и n-МОП ключах, и подключён к двум шинным трансляторам. Последние передают состояние триггера на две дифференциальные линии бита , При чтении линии бита заводятся на вход дифференциального усилителя с защёлкой на выходе, а при записи «передавливают» состояние триггера. Такая конфигурация зовётся «6T» по числу используемых транзисторов.

Рис. 14.20 Статическая память хранит каждый бит в 4-транзисторном триггере, который считывается/пишется через пару однотранзисторных ключей. «WL» - линия выбора слова, «BL» - линия бита

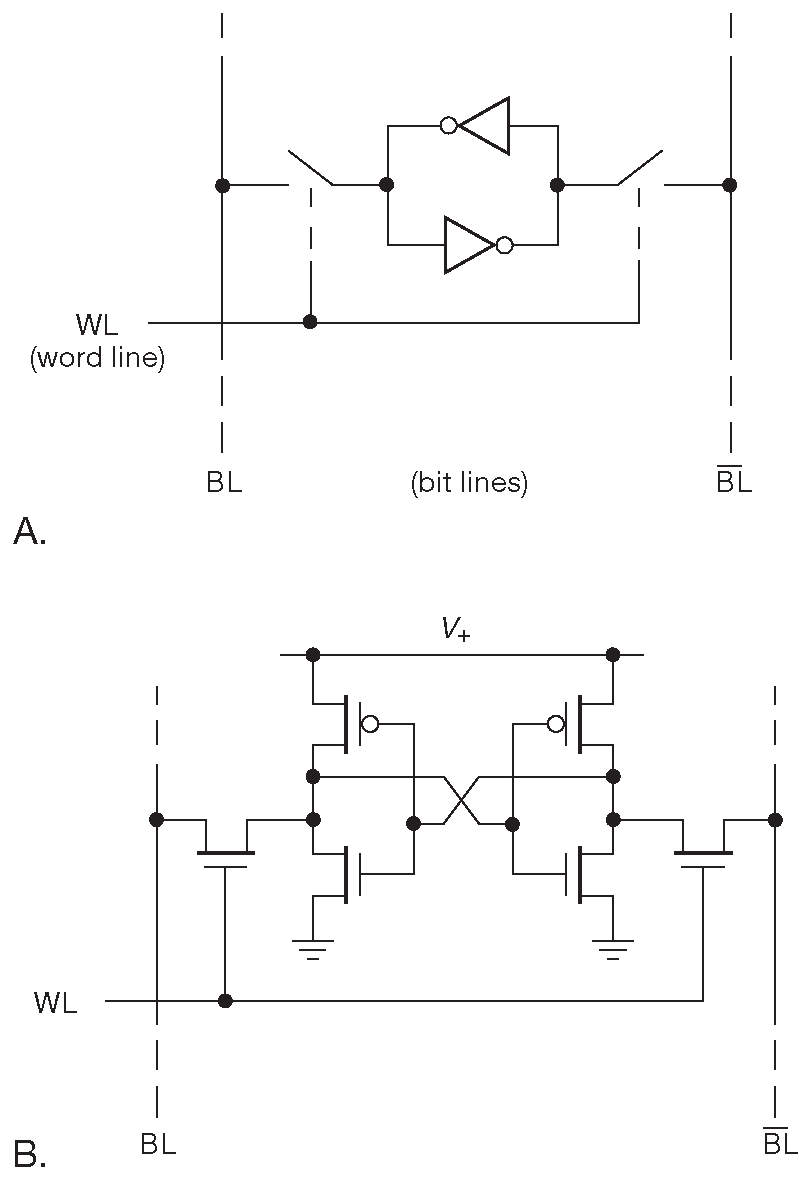

Как и во всех прочих типах памяти, одиночные триггеры в SRAM организуются в слова, считываемые или записываемые параллельно в ходе одного цикла. Ширина слова может быть от 8 до 32 бит, а с учётом бита чётности 9, 18 или 36 разрядов. Слова организуются в двухкоординатные массивы ( рис. 14.21 ) так, чтобы каждое слово определялось координатами ( адресом ) в массиве. На рисунке показана память на 4 Mb ( 512K 8-разрядных слов 29 ), организованная в 8 блоков ( по числу разрядов в слове ) по 1024 рядов и 512 колонок каждый.

Рис. 14.21 Асинхронная SRAM выполнена в виде массива 6-транзисторных битовых ячеек с n-разрядным параллельным адресом и простым стробированием сигналами «WE'», «CS'» и «OE'». Наиболее распространены слова шириной 8 и 16 разрядов

14.4.3.A Временная диаграмма асинхронной статической памяти

==1017

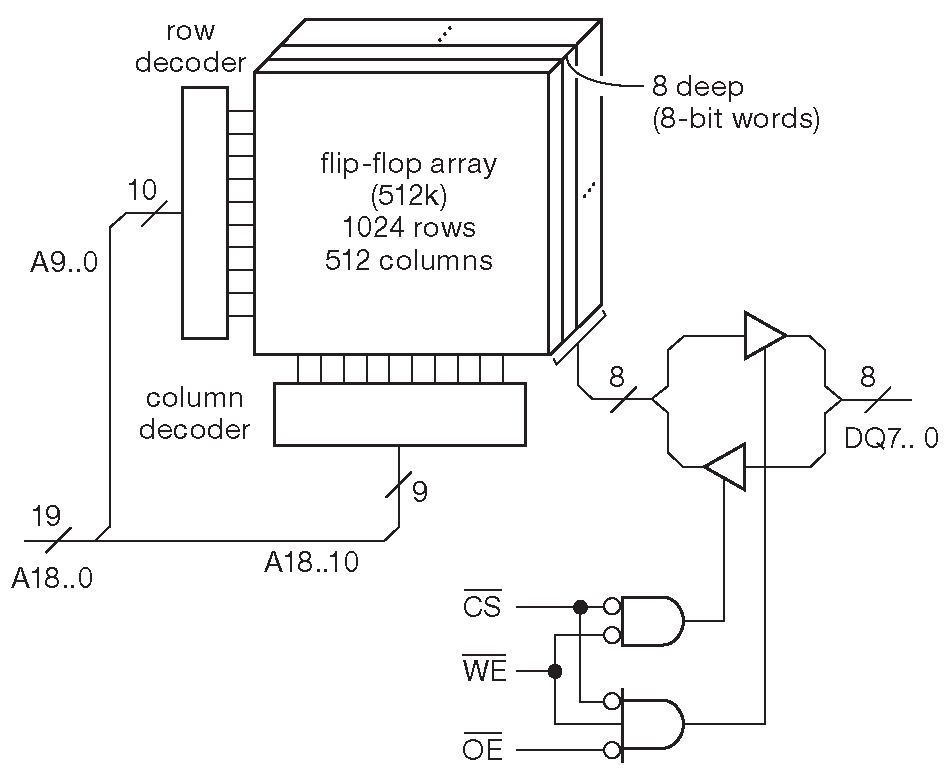

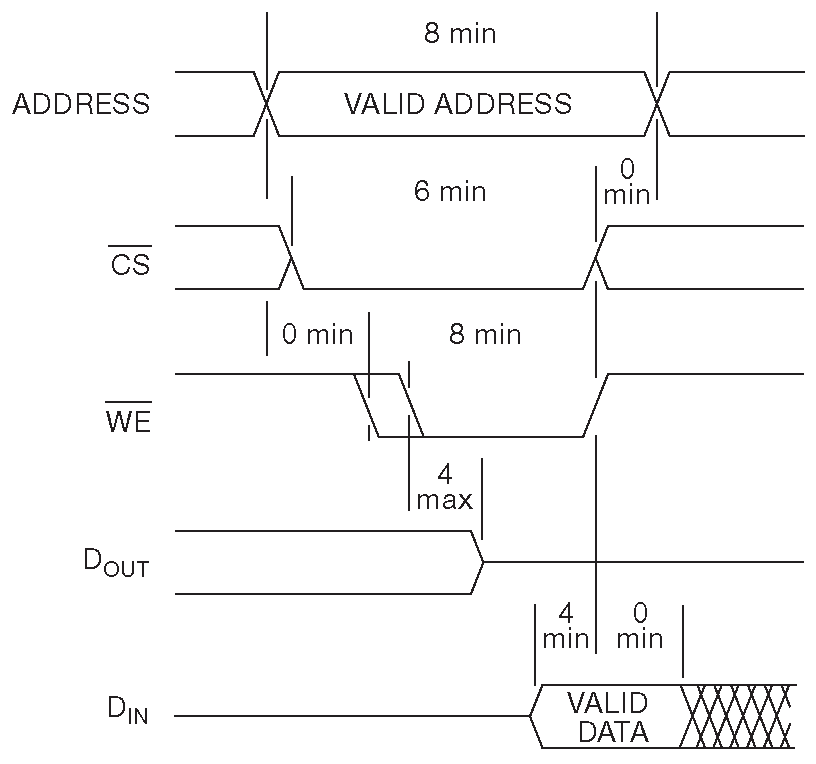

Классическая статическая память является асинхронной, т.е. входа тактирования у неё нет. Нужно просто подать сигналы, выдержав правильные временные соотношения, и данные будут записаны ( или считаны ). Использовать элементарно: для чтения слова надо выставить адрес, активировать сигнал «CE'» ( разрешение кристалла ) и «OE'» ( разрешение выхода ). Запрошенные данные появятся на выходах с третьим состоянием на позднее, чем через \(t_{AA}\) ( время выборки адреса ). Для записи подаётся адрес, данные и «CE'», а затем - после \(t_{AS}\) ( времени установления адреса ) - подаётся импульс разрешения записи «WE'». Данные защёлкиваются в памяти по заднему фронту «WE'». По рис. 14.22 и 14.23 видно, что быструю статическую память ( \(t_{AA}\)=8 ns , \(t_{AS}\)=0 ns ) можно использовать в качестве внешнего кэша. «Скорость» памяти устанавливается по времени между подачей адреса и появлением правильных данных для этого адреса ( для чтения ) или по завершении цикла записи ( для записи ). Предполагается, что прочие сигналы ( «CS'», «WE'» или «OE'» ) подаются в нужное время.

Рис. 14.22 Цикл чтения асинхронной памяти ( «WE'» удерживается в ВЫСОКОМ состоянии ). Показанные времена ( в ns ) - гарантированные цифры для наихудших условий для быстрой памяти K6R4008V1D-08 ( Samsung, 512 KB , 8 ns

Рис. 14.23 Цикл записи для той же памяти, что и на рис. 14.22

Микросхемы статической памяти сейчас имеют максимальный объём 16 Mb и размер слова от 1 до 32 разрядов. Есть варианты с раздельными входными и выходными шинами, низкопотребляющие: ∼1μA в режиме ожидания, 1 mA при обращении с частотой 1 MHz . А есть микросхемы двухпортовой памяти: два независимых набора линий адреса, данных и управления, имеющих доступ к одному массиву ячеек памяти и «семафорам», помогающим избегать столкновений при обращении с разных портов.

Отметим, что, независимо от прочей схемотехники, линии данных статической памяти не обязаны идти на одноимённые линии в процессоре ( или любом ином устройстве, к которому надо подключить оперативную память ). В данном случае связи можно вести как угодно, т.к. путь данных и при записи и при чтении будет одним и тем же.

[* То же самое можно сказать и о линиях адреса ОЗУ. Но! Оба эти утверждения не верны в случае ПЗУ всех видов, т.к. записываются такие микросхемы в одном месте, а считываются в другом. Или как минимум оба места должны придерживаться одной схемы разводки. Это один из методов защиты ПО встраиваемых систем, использовавшийся во времена микроконтроллера i8031 и внешних микросхем программной памяти. Кроме того, нельзя путать линии DDR памяти: эти микросхемы получают внешние команды конфигурации, поэтому ни линии адресов, ни линии данных в этих ИМС не равнозначны. С другой стороны, найти сейчас микроконтроллер без внутренней программной памяти крайне сложно, а подключить DDR модуль «на коленке» не получится, поэтому указанные сведения вам, скорее всего, в жизни не пригодятся ].

14.4.3.B Псевдостатическая память

Преимуществом статической памяти является простая схема управления и низкое потребление. Но 6-транзисторный триггер занимает больше места, чем однотранзисторная ячейка динамической памяти. В итоге её цена выше, а плотность информации ниже. Зато более ёмкая динамическая память нуждается в регенерации, а мультиплексированная шина адреса усложняет подключение.

==1018

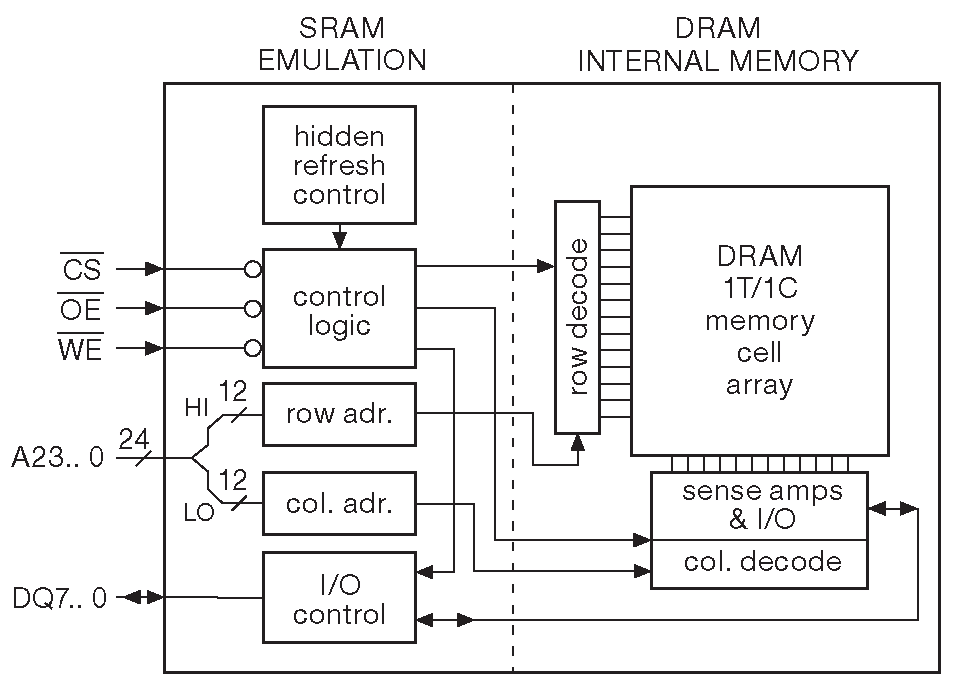

Псевдостатическая память сочетает в себе лучшие стороны двух технологий: массив ячеек динамической памяти снабжается схемой регенерации и внешним интерфейсом, имитирующим обычную статику ( рис. 14.24 ). В настоящий момент можно найти PSRAM объёмом до 128 Mb . Некоторые модели прямо совместимы по разводке с асинхронной статической памятью. Время случайного доступа составляет ∼50 ns , но ниже ( ∼20 ns ) при последовательном постраничном считывании. Регенерация скрыта от внешнего наблюдателя и не интерферирует с внешним обменом данными. Из-за постоянной активности схемы регенерации ток покоя имеет величину порядка 100 μA . Есть и режим «выключения», при котором потребление падает до нескольких микроампер, но отключение регенерации вызывает полную потерю записанных данных.

Рис. 14.24 «Псевдостатическая» оперативная память. Для наружного наблюдателя выглядит как обычная асинхронная память, но внешний интерфейс скрывает истинное положение вещей: обычные динамические ячейки «1T1C» снабжены дополнительной логикой и схемой регенерации

Ток холостого хода PSRAM заметно выше, чем у обычной статической памяти, но остаётся в допустимых рамках для мобильных устройств, типа сотовых телефонов, имеющих батарею высокой ёмкости. В результате псевдостатика вытесняет обычную асинхронную SRAM, исключая области с очень низким потреблением или очень высоким быстродействием ( <10 ns ).

14.4.3.C Синхронная статическая память

В Части 11 авторы пели осанну синхронной логике, имеющей массу преимуществ в области шума ( все сигналы устаканиваются до прихода активного фронта ), предсказуемости временных характеристик, отсутствие метастабильности [* см. §10.4.2.D ] и т.д. А раз так, зачем использовать асинхронную память ?

А никто не обязывает её использовать. Ничто не мешает обернуть массив асинхронной памяти синхронной машиной состояний с синхронными же регистрами данных. Так можно получить синхронную SRAM 30 . Т.к. речь идёт о тактируемой системе, скорость синхронной SRAM выражается в мегагерцах максимальной рабочей частоты . На данный момент цифры лежат в диапазоне 100...400 MHz , а объём одного кристалла от 1 до 72 Mb . Ширина слова варьируется кратно 9 разрядам: 9, 18, 36 или 72 бита, где каждый 9-ый разряд отвечает за чётность.

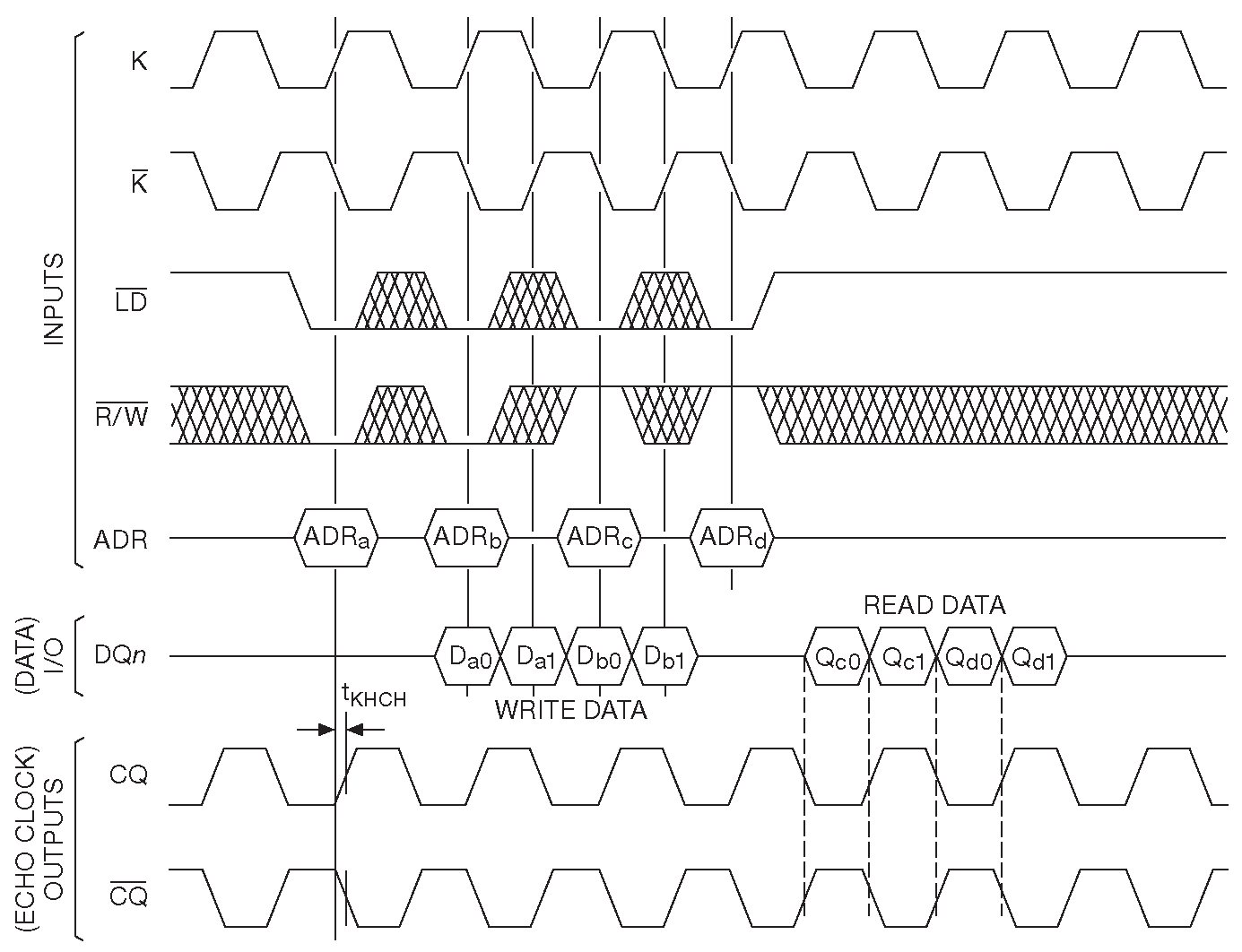

Синхронная память ( и статика, и динамика ) - более сложная штука, чем асинхронные предшественники. Ситуация осложняется обилием режимов работы, например, удвоенной скоростью выдачи данных: достаточно удобным методом ускорения блочной передачи данных ( каковой предполагает использование обоих фронтов тактового сигнала, см. рис. 14.25 ). Но, чтобы воспользоваться удобствами, приходится разбираться со всеми этими режимами и их настройкой. А ещё потребуется источник чистого тактового сигнала ( дифференциального ), потому что пакеты идут с промежутком всего несколько наносекунд. Иначе говоря, синхронная SRAM предложена для увеличения скорости и пропускной способности, поэтому плюсы синхронных операций идут в комплекте с минусами быстрого тактирования и жёстких временнЫх ограничений.

Рис. 14.25 Временная диаграмма синхронной SRAM с двойной скоростью выдачи данных ( DDR ), тактируемой и при записи, и при считывании. Данные синхронизируются по два слова ( два соседних адреса ). При записи входные данные должны присутствовать при обоих фронтах тактового сигнала «K/K'» уже через один такт после фиксации адреса. При чтении данные задерживаются на 1.5 цикла после фиксации адреса и выдаются в сопровождении фронтов на «восстановленном» тактовом сигнале «CQ/CQ'» ( он формируется из «K/K'» и учитывает накопленную задержку \(t_{KHCH}\) )

14.4.4 Динамическая память

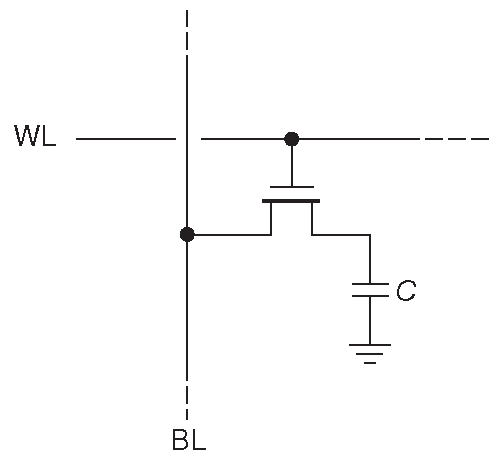

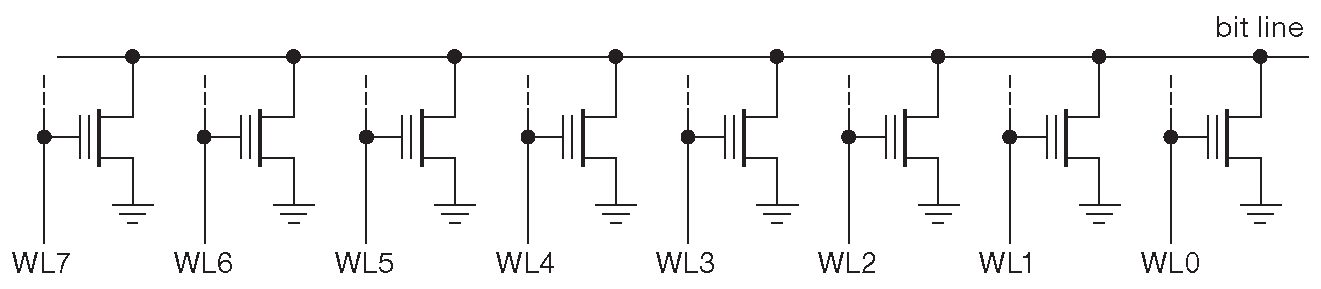

Как отмечалось ранее, можно сильно выиграть в ёмкости, если использовать 1-транзисторную ячейку памяти, хранящую информацию в небольшом конденсаторе, а необходимость проводить периодическую регенерацию данных не пугает. Такой способ хранения называется «динамической» памятью, а базовая ячейка именуется «1T1C» ( рис. 14.26 ). Это рабочая лошадка современной подсистемы временного хранения данных, имеющая ёмкость несколько гигабит на кристалл. Поставляется модулями ёмкостью до 16 GB ( 128 Gb ) 31 .

Рис. 14.26 Ячейка динамической памяти «1T1C». Каждый бит хранится в виде заряда на конденсаторе ( ∼1V на обкладках заряженного и 0V для разряженного ). Состояние конденсатора считывается, пишется и регенерируется по линии «BL», когда по линии управления «WL» подаётся активный уровень. Типичная величина ёмкости 30 фемтофарад

Подобно статической памяти, классическая DRAM является асинхронной , но её временная диаграмма гораздо запутаннее простой и понятной диаграммы SRAM. Причём картина усложняется ещё больше, если дополнить её циклами регенерации. Из динамической памяти можно сделать синхронный вариант ( SDRAM ), если встроить асинхронный массив ячеек памяти в синхронную машину состояний. На данный момент асинхронная динамическая память стала достоянием истории, тем не менее, заглянуть ей внутрь будет полезно.

14.4.4.A Асинхронная динамическая память

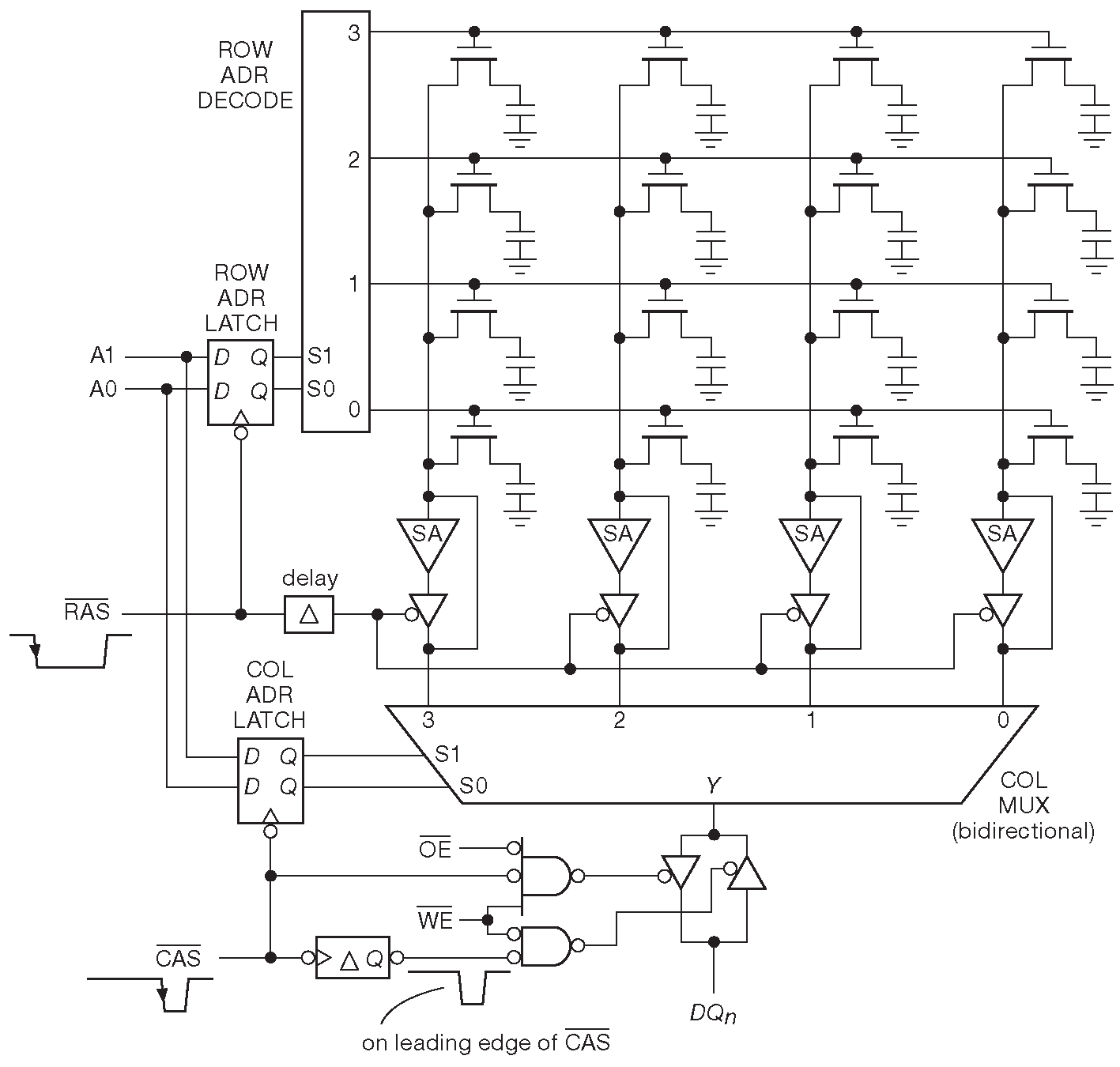

На рис. 14.27 в упрощённой форме показана DRAM на 16 слов шириной 1 бит, что недостаточно для работы, но удобно для разбора принципов работы. Каждый n-МОП транзистор содержит внутри конденсатор величиной примерно 30 fF между каналом ( стоком ) и землёй. Все транзисторы организованы в массив 4 ряда по 4 элемента. Драйвер рядов с защёлками на каждом выходе ( старшая половина адреса ) используется для подачи ВЫСОКОГО уровня на выбранные затворы массива транзисторов, включая их и подсоединяя соответствующие конденсаторы к вертикальным линиям, а через них к усилителям считывания ( SA ) с фиксацией выхода. Выход одного из усилителей подключается через заданный канал двунаправленного мультиплексора ( младшая половина адреса ) к буферам шины данных. Таким образом, число линий адреса динамической памяти уменьшается в 2 раза за счёт мультиплексирования старшей и младшей половины [* и по той же причине добавление одного адресного разряда к внешней шине учетверяет объём памяти ] .

Рис. 14.27 Архитектура асинхронной динамической памяти ( здесь показан массив 4×4 «слов» величиной 1 разряд ). Адресные линии мультиплексированы, и адреса столбцов и рядов защёлкиваются внутренними схемами. Усилитель считывания с фиксацией выхода ( SA ) считывает ( и «освежает» ) состояние ячеек выбранного ряда в ходе цикла чтения. В цикле записи выходы внутренних усилителей «передавливаются» буферами внешней двунаправленной шины «DQn»

==1019

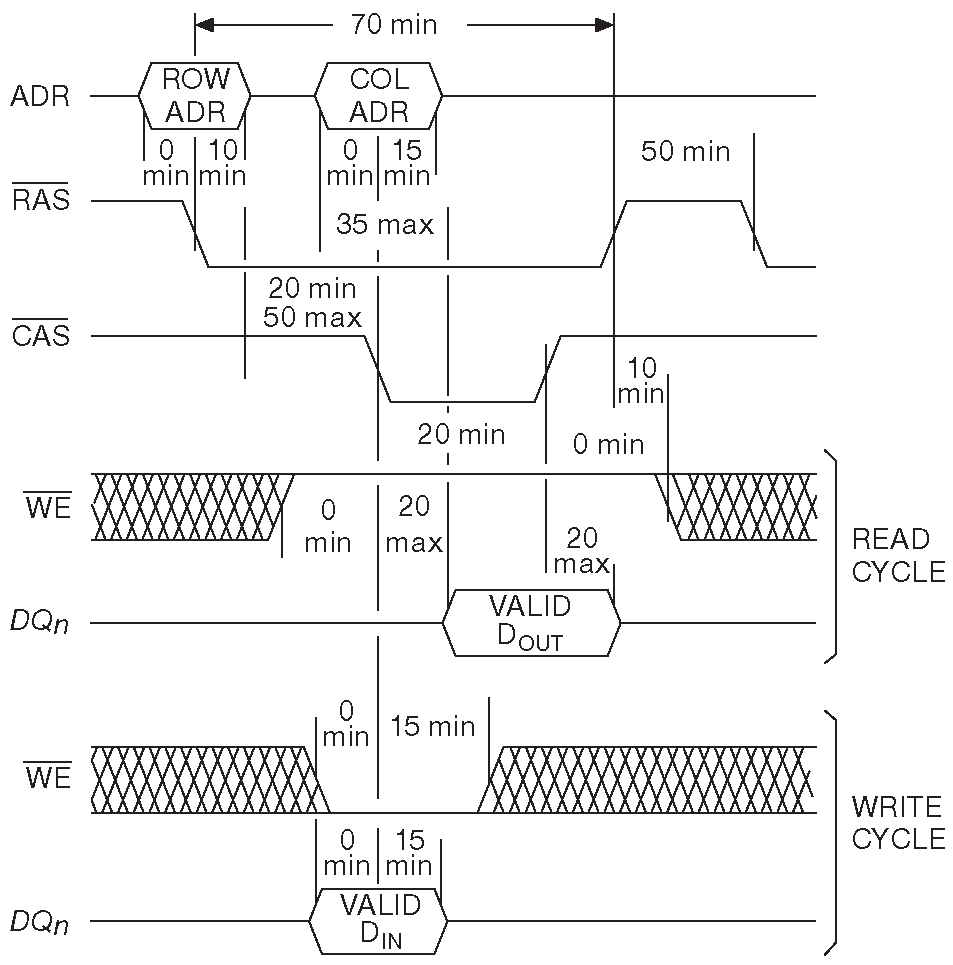

Теперь, как она работает. Начнём с цикла чтения. Будем считать, что какие-то конденсаторы ( каждый для своего бита ) уже получили заряд в предшествующих циклах записи и либо имеют заряд ( потенциал ∼1V ), либо не имеют его. Базовый цикл чтение-запись по одному адресу для асинхронной DRAM со скоростью 70 ns показан на рис. 14.28 32 . Адресные линии мультиплексированы. Старшая половина ( ряд ) передаётся первой и сопровождается стробом ряда ( «RAS'» ), с помощью которого адресные биты фиксируются, переводя затворы выбранных транзисторов в активное состояние и подключая конденсаторы к усилителям считывания. На схеме изображены неинвертирующие усилители с обратной связью, но на самом деле они выполнены в виде триггера, который начинает цикл в сбалансированном состоянии и переходит в несбалансированное за счёт инжекции заряда из конденсатора 33 . В течение первой части цикла усилитель считывания делает две вещи: защёлкивает состояние, соответствующее заряду конденсатора в своей ячейке выбранного ряда и «регенерирует» заряд, подавая защёлкнутый уровень обратно на конденсатор.

Рис. 14.28 Временная диаграмма асинхронной динамической памяти. «RAS'» и «CAS'» - адресные стробы для мультиплексированного адреса. Как и в асинхронной статической памяти, входные/выходные данные не привязаны ни к какому тактовому фронту. Вместо этого гарантируется, что задержка их появления не превысит цифру для наихудшего случая ( на рисунке изображена «70-наносекундная» память )

==1020

Во второй половине цикла динамической памяти адресные линии задают младшую половину адреса, которая защёлкивается по стробу адреса колонок ( «CAS'» ). Зафиксированная младшая половина адреса подаётся на линии выбора мультиплексора колонок, который подключает к выходу нужный усилитель считывания. Рассматривается цикл чтения, следовательно, «WE'» в пассивном состоянии, и сигнал с выхода усилителя считывания проходит на выход «DQ0». Т.к. память асинхронная , правильное состояние появляется на выходе с некоторой гарантированной задержкой относительно установившегося адреса и фронтов стробирующих сигналов. В отличие от синхронной DRAM, в микросхеме отсутствует сигнал общего тактирования.

Цикл записи аналогичен, но «WE'» активируется где-то рядом с фронтом «CAS'». Низкий уровень «WE'» превращает линию «DQ0» во входную, а значит, сигнал с шины данных передавит состояние усилителя считывания на выбранном канале, а уже защёлкнутое в усилителе значение зарядит или разрядит конденсатор хранения.

Схема 14.27 имеет некоторую особенность. Как только ряд выбран ( RAS-полуцикл ), и выбрана колонка для чтения, нет никаких причин повторять адрес ряда, если требуется читать другие колонки того же ряда. Эта мысль является основой «страничного режима» и «расширенного вывода данных». Идея очень продуктивная, ведь большая часть обращений к памяти выглядит как выборка по смежным адресам ( последовательные команды, работа со строками, массивами и т.д. ).

==1021

14.4.4.B Синхронная динамическая память

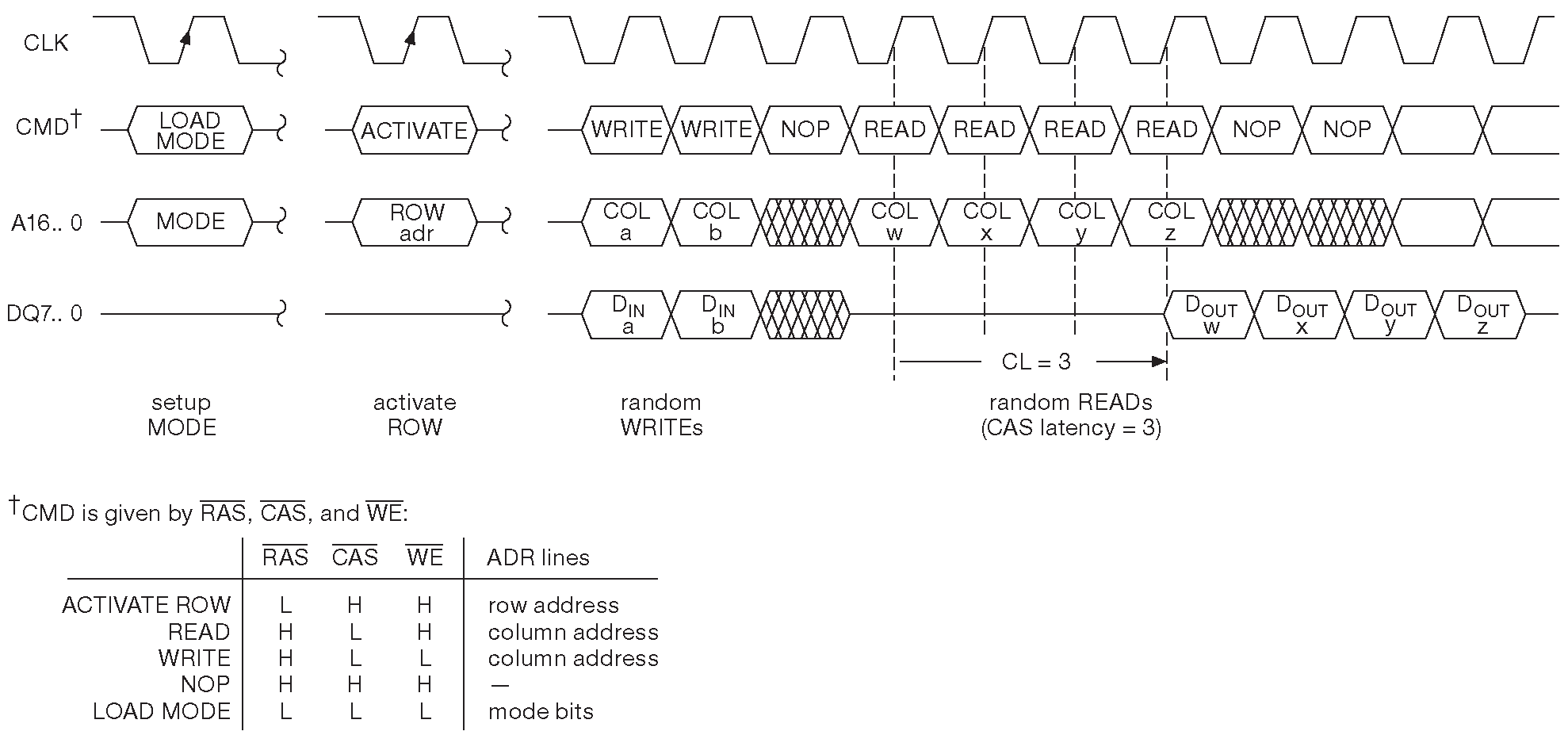

Современная динамическая память имеет синхронную архитектуру ( SDRAM ). Внешний тактовый сигнал 34 синхронизирует работу внутренней машины состояний, которая обрамляет асинхронный массив динамической памяти. Исходная SDRAM с однократной скоростью выдачи данных прошла несколько этапов развития ( DDR, DDR2 и т.д., где первая «D» отвечает за удвоенную скорость передачи данных ). Фронты тактового сигнала синхронизируют загрузку половин адреса и движение данных. Обычный режим работы синхронной DRAM – «пакетный» , когда несколько последовательных слов из ячеек памяти с одним адресом ряда выдаются в виде непрерывной последовательности ( см. описание MODE ниже ).

В отличие от асинхронной DRAM, синхронная версия дьявольски сложна и даже имеет набор «команд» ( которые также надо синхронизировать ), задающих детали взаимодействия. Команда определяется тремя битами, которые, возможно, в насмешку над асинхронной DRAM называются «RAS», «CAS» и «WE». Но теперь эти три линии устанавливаются до появления активного фронта и задают поведение схемы в момент его прохождения. Пять основных команд показаны на рис. 14.29 . «ACTIVATE ROW» загружает адрес ряда, «READ» и «WRITE» загружают адрес колонки и инициализируют передачу данных 4-, 8- или 16-разрядными словами ( в зависимости от разрядности кристаллов памяти ) по активному фронту ( для SDR, рис. 14.29 ) или на удвоенной скорости по обоим фронтам ( для DDR ).

Рис 14.29 Синхронная динамическая память использует внешний интерфейс, работа которого синхронизирована с внешним тактовым сигналом, а доставшиеся в наследство линии «RAS», «CAS» и «WE» используются для передачи 3-разрядных команд. На рисунке показан случайный обмен ( как противоположность «пакетному» ) с SDR SDRAM, т.е. с однократной скоростью передачи. Пакетная передача используется гораздо чаще. При этом данные из нескольких последовательных CAS-адресов выталкиваются последовательными фронтами тактового сигнала ( для памяти с удвоенной скоростью - DDR - данные передаются по обоим фронтам тактового сигнала

Обратите внимание на последовательность событий при чтении. Данные выходят из микросхемы с частотой тактового сигнала, но между подачей адреса колонки и появлением данных есть задержка в несколько тактов. Эта задержка именуется «латентностью CAS». На рис. 14.29 показано, как она выглядит для случая CL=3 . Каждая конкретная микросхема сообщает минимальную латентность CAS для некоторой частоты тактирования ( каталожным наименованием модели ). Например, MT47H128M8HQ-25E - DDR2 SDRAM объёмом 128 MB с шириной слова 8 разрядов, упакованная в корпус BGA, с CL=5 при частоте \(t_{CLK}\)=2.5 ns . Остальная вычислительная система должна знать реальную латентность CAS ( предполагается, что цифры попадают в допустимые пределы ). Требуемое значение передаётся в кристалл командой «LOAD MODE» ( входы «RAS», «CAS» «WE» в момент прихода тактового фронта в НИЗКОМ состоянии, а собственно режим индицируется адресными линиями ). MODE включает не только латентность CAS, но также одноадресную/пакетную передачу ( с пакетами длиной 2, 4 или 8 последовательных слов ) и ещё несколько узкоспециальных опций. На следующем уровне сложности приходится учитывать латентность цикла записи , которая довольно логично именуется «WL» и требует учёта, т.е. вставки задержки между снятием адреса колонки и подачей данных на вход.

Сам факт внешнего тактирования синхронной DRAM переводит понятие скорости доступа в термины частоты . Скажем, обозначение «DDR3-1600» соответствует SDRAM, удовлетворяющей требованиям стандарта DDR3 и выдающей данные на обоих фронтах тактового сигнала частотой 800 MHz . ИМС, выпускаемые в момент выхода книги, имели скорость 400...1600 MT/s ( мегатрансферов в секунду ), содержали до 4 Gb на кристалл и имели ширину слова данных 4, 8 или 16 разрядов. Следующее поколение DDR4 поднимает скорость до 1600...3200MT/s , а ёмкость до 16 Gb .

14.4.5 Постоянная память

==1022

Память, не требующая питания для хранения информации ( NVM ) - совершенно необходимая в мире вычислительных систем вещь. В ней хранится:

- стартовый ( startup / boot ) код/настроечные параметры,

- программное обеспечение и

- данные ( текст, музыка, фото и т.п. ). Память, разбиравшаяся до настоящего времени для таких задач не подходит, т.к. «забывает» все записанные данные при отключении питания.

Одним из решений будет внешняя батарейка, не позволяющая питанию пропадать. Такой вариант с резервным источником подкрепляется наличием малопотребляющей памяти и используется для сохранения настроек в компьютерах ( где их чаще всего упоминают в качестве «КМОП настроек» ). Кроме того, батарейная статическая память не подвержена ограничениям, свойственным постоянной памяти: неторопливое стирание ( временной масштаб - миллисекунды ), большое, но всё же ограниченное число циклов записи ( \(∼10\space^5...10\space^6\) ). Против работает само наличие батареи, за зарядом которой, к тому же, необходимо присматривать 35 .

Другое решение - использование памяти, не требующей питания в режиме хранения. Здесь, как и в области динамической памяти происходят активные подвижки. Все современные устройства используют некоторую форму хранения заряда на «плавающем затворе» МОП транзистора. На таком принципе построена флэш-память, составляющая основу USB и SSD накопителей. Технология имеет впечатляющие параметры: ёмкость измеряется уже в терабитах, время хранения превышает десять лет, а цена ниже $0.50 за гигабайт. Но хранение заряда на плавающем затворе имеет свои недостатки, и основные - ограниченное число циклов стирания-записи ( ресурс ) и относительно медленная запись ( и стирание ): масштаб времени - миллисекунды. И наоборот, обычная статическая и динамическая память имеет неограниченное число циклов стирания-записи и очень высокую скорость передачи данных - десятки наносекунд. Некоторые технологии постоянного хранения, появившиеся в последнее время исправляют некоторые перечисленные недостатки. К таким технологиям относятся ферроэлектрическая ( FRAM ), магниторезистивная ( MRAM ) и память на разнице фаз ( PRAM )

Рассмотрим сначала некоторые прежние технологии хранения, а затем разберём самый массовый на данный момент вариант – флэш-память с плавающим затвором.

==1023

14.4.5.A Архаичные технологии постоянной памяти

- Масочные ПЗУ

- Они были первыми. Это просто вентили со связями, жёстко заданными при производстве. Они не предусматривают возможности модификации. Информация хранится в простой таблице соединений, рассчитанной только на считывание данных ( отсюда и термин «память только для чтения» ). Метод по-прежнему используется для создания простых таблиц преобразования в заказных микросхемах и гарантированно не нуждается в питании для хранения данных, но не вполне отвечает современным представлениям об удобстве.

- PROM

- Программируемая память только для чтения. Её можно было записать один раз. Ещё одно название – «память на пережигаемых перемычках», потому что внутри она выглядела как набор предохранителей ( металлических или полупроводниковых ), которые нужно было пережигать, оставляя только требуемые связи. Появление перепрограммируемых ( стираемых ) технологий памяти полностью вытеснило PROM с рынка.

- EPROM

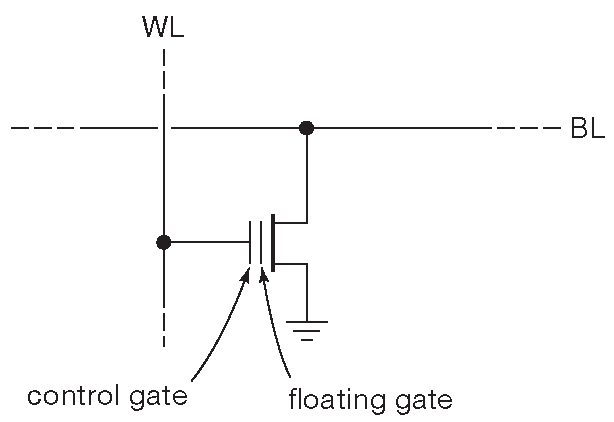

- Следующей была стираемая программируемая память. Теперь информация хранилась в маленьких конденсаторах в формате плавающего затвора, скрытого слоем диэлектрика. Заряд затвора меняет пороговое напряжение МОП транзистора ( рис. 14.30 ). Эта же технология хранения используется по сию пору во флэш-памяти. [* См. ещё одно применение этой технологии - опорный источник с плавающим затвором, см. §9.10.4 ] . Для считывания используется «контрольный затвор»: когда конденсатор заряжен и имеет отрицательный потенциал за счёт набежавших электронов, порог переключения равен нескольким вольтам, а при разряженной ёмкости затвора порог переключения уходит в отрицательную область, т.е. транзистор начинает проводить ток даже при 0V на контрольном затворе. Прямой электрической связи с конденсатором хранения нет, поэтому для стирания и записи информации требуется особый приём. При записи отрицательный заряд попадает на затвор с помощью «инжекции горячих электронов» ( CHE ), каковая предусматривает включение транзистора при повышенном напряжении на затворе ( 12...27 V ). Для снятия заряда при стирании требовалось облучать кристалл ультрафиолетовым светом ( отсюда ещё одно название – «УФ-память» ), т.е. процесс проходил в формате «кристалл за раз». Керамический корпус с кварцевым окошком существенно увеличивал стоимость и габариты, а процесс стирания-записи требовал извлечения микросхемы из целевого устройства, поэтому с появлением технологии электрического стирания ультрафиолетовая память быстро сошла со сцены.

Рис. 14.30 Ячейка с «плавающим затвором». Используется в микросхемах постоянной памяти вроде EEPROM и флэш. Данные записываются на плавающий затвор за счёт эффекта туннелирования или инжекции «горячих» электронов. Накопленный в результате заряд изменяет пороговое напряжение, а линия данных ( «BL» ) и управления ( «WL» ) позволяют обнаружить изменения. Утечка с плавающего затвора столь мала, что данные гарантированно хранятся более 10 лет, не требуя питания и регенерации

- OTP EPROM

- Однократная стираемая программируемая память. Необычное и несколько противоречивое название «однократно программируемая стираемая память только для чтения» ( пример инженерного юмора, который непонятен непосвящённым ). OTP EPROM стала ответом на слишком высокую стоимость керамического корпуса ультрафиолетовой памяти. Решение получилось довольно прямолинейным: кристалл УФ-памяти упаковали в дешёвый пластиковый корпус. Недостаток у него всего один, но какой! Пластиковый корпус совершенно непрозрачен, поэтому однажды записанные данные нельзя стереть. Проблема решалась отладкой программы на УФ вариантах памяти, а серийные устройства собирались на OTP в пластиковых корпусах. Этот вариант памяти исчез вместе с УФ моделями [* ещё бы: кристалл-то один ] .

14.4.5.B Электрически стираемая постоянная память

Современная эра постоянной памяти началась с появлением электрически стираемой программируемой памяти только для чтения 36 - EEPROM или E²PROM . Больше никаких ртутных ламп! Теперь не надо вынимать-вставлять ИМС: память стала программируемой в схеме . Для разрядки плавающего затвора в ней используется повышенное напряжение, при котором начинает работать квантово механический феномен - туннельный переход . Частица с недостаточной для преодоления потенциального барьера изолятора энергией может при определённых обстоятельствах оказаться на другой его стороне 37 . Официальное название «туннелирование Фаулера-Нордхайма» , которое часто сокращается до F-N. EEPROM имеют на кристалле схему накачки заряда, повышающую напряжение до требуемого при программировании УФ-памяти или для снятия заряда через F-N туннелирование. Вот и секрет внутрисхемного программирования.

==1024

EEPROM используют двухтранзисторную ячейку, которая позволяет стирать и программировать отдельные биты. Гибкость получается замечательная, но схема занимает место, на котором можно было бы хранить данные. Развитие инженерной мысли привело к флэш-памяти с однотранзисторной ячейкой. Более высокая плотность хранения данных тянет за собой необходимость работы с блоками памяти, используя вывод подложки.

EEPROM и флэш-память имеют умеренную живучесть - \(10\space^5...10\space^6\) циклов стирания-записи. И стирание, и запись - медленные операции ( ∼10 ms ), чтение гораздо быстрее ( ∼100 ns ). Хотя основную долю постоянной памяти занимает флэш-память, возможность работы с отдельными байтами и даже битами делает EEPROM очень удобными для хранения небольших объёмов данных, например, калибровочных параметров. Скажем, в напольных весах измерение может идти в фунтах или килограммах и корректироваться по таблице поправок в зависимости от температуры окружающей среды. EEPROM для такого рода задач обычно включают в состав микроконтроллера ( Часть 15 ), но можно взять и отдельную микросхему. Обычно такие кристаллы упаковываются в компактный корпус SC-70, DFN и т.д., поддерживают какой-то последовательный протокол ( SPI, I2C, UNI/O, Microwire ) и имеют ёмкость до 1M бит. Неплохой выбор предлагают Atmel и Microchip. Цена вполне приемлема: EEPROM с интерфейсом I2C и ёмкостью 1Kb стоит $0.17 в количествах, а на 64K в два раза больше.

14.4.5.C Флэш-память

Флэш-память не поддерживает побитное и побайтное стирание-запись, доступное в EEPROM, и работает с объёмами, кратными блоку. Зато такая память быстрее сотрёт много байт ( «мгновенное стирание» - отсюда и название [* flash - вспышка ] ). Модификация мелких порций данных невозможна, но внешний интерфейс, включающий буфер на статическом ОЗУ может успешно скрывать данный факт. Зато кристалл имеет гораздо больший объём, особенно если выполнен по технологии NAND ( сейчас доступны микросхемы ёмкостью до терабита , хотя внутри не один кристалл, но целый их набор ). Флэш-память бывает двух видов NOR и NAND.

- NOR флэш

- Организация ячеек памяти NOR флэши показана на рис. 14.31 . Это исходная форма флэш-памяти. Все транзисторы включены параллельно, поэтому при чтении надо запрещать посторонние каналы. Запись в плавающие затворы выполняется инжекцией «горячих» электронов подобно тому, как это делается в EPROM. Стирание, как и у всех видов флэш-памяти, выполняется поблочно. На подложку подаётся повышенное напряжение, которое создаёт условия для туннельного эффекта F-N с участием плавающих затворов. Типичные размеры блоков 4...64 KB , причём часто в одной микросхеме используется сектора нескольких разных размеров. NOR флэш подключается через простой внешний интерфейс, подобный SRAM памяти ( иногда можно выбирать между синхронным и асинхронным доступом ) и может использоваться в системе непосредственно. Но ограниченное число циклов записи и стирание, кратное размеру сектора, диктует необходимость рассмотрения такой памяти, как памяти только для чтения. Современные ИМС NOR флэши имеют объём 1 Mb...1 Gb.

Рис. 14.31 NOR флэш с параллельной организацией ячеек

==1025

- NAND флэш

- В отличие от NOR, NAND память проектировалась на замену накопителям данных, вроде жёстких дисков. Именно этот тип микросхем используется в «USB-дисках», SD-картах , CF-накопителях , твердотельных дисках ( SSD ), а также в программной памяти микроконтроллеров ( Часть 15 ). Термин NAND проистекает из вертикальной ( последовательной ) организации битовых ячеек ( рис. 14.32 ). Считывать их надо, подавая ВЫСОКИЙ уровень на все затворы, кроме нужного, каковой и будет определять проводимость всей цепочки в соответствии со степенью заряженности своего плавающего затвора. Эффект туннелирования используется и при стирании, и при записи. Стирание выполняется посекторно. Увеличение плотности упаковки на первый взгляд неочевидно, но при последовательном соединении не требуется разделение контактов стока и истока в соседних транзисторах, а явно заданные выводы нужны только на концах цепочки. Чтобы уменьшить число выводов в NAND памяти используют последовательный интерфейс управления и посекторное стирание. Стоит учесть, что в законченных устройствах, подобных USB накопителям, к микросхемам памяти прилагается контроллер памяти, который полностью скрывает от внешнего наблюдателя временнЫе параметры операций стирания и записи. Спецификация SD-карт памяти оговаривает поддержку двух протоколов: собственно протокола SD-карты и последовательного SPI, который есть в большинстве современных микроконтроллеров 38 . Контроллер памяти, используемый во флэш-накопителях, занят не просто преобразованием последовательного протокола обмена в параллельный протокол памяти, но, кроме того, присматривает за равномерным расходованием ресурса каждого блока, чтобы сгладить эффекты старения изоляторов от эффекта туннелирования. Вдобавок, контроллер выискивает плохие ячейки, фиксирует их в специальной таблице и перенаправляет новые обращения по резервным адресам.

Рис. 14.32 NAND флэш-память с последовательным включением ячеек

Производители NAND памяти дерзко увеличивают плотность хранения с помощью метода, называемого «ячейки с многоуровневым зарядом» ( MLC ). Иначе говоря, технология предполагает дробный заряд изолированного затвора и его оценку при считывании с использованием некоторых пороговых уровней. На данный момент используется четыре ( MLC ) и восемь ( TLC ) уровней, т.е. 2 или 3 бита на транзистор [* см. фазовое кодирование сигнала в каналах связи ## ] . ( Может, стоит ввести для таких ячеек обозначение «½T» и «⅓T» ? ). Конструкция не из простых: данные должны храниться на частично заряженных изолированных затворах, причём заряд не должен меняться слишком сильно как минимум несколько лет. [* Не с таким ли изменением заряда связаны проблемы с длительным хранением данных на выключенных SSD накопителях ? ] Чтобы оценить масштаб, прикиньте: 0.3 фемтофарады должны растянуть потерю ( или приток ) 3000 электронов на примерно \(3×10\space^8\) секунд ( 10 лет ). Один электрон в день ! Как это вообще может работать ?! 39

Современная NAND флэш имеет ёмкость до 1 Tb на микросхему ( зарядовая схема MLC в сочетании с несколькими кристаллами в едином корпусе ), или по 16 байт на каждого жителя Земли 40 .

14.4.5.D Будущее постоянной памяти

Флэш-память - отличная штука. Но у неё ограниченное число циклов стирания-записи, а само это действие отнимает много времени. Идеальной постоянной памятью была бы статическая память, не нуждающаяся в питании. Она должна допускать случайный доступ по любому адресу при чтении и записи с одинаково высокой скоростью, неограниченное число циклов смены информации и длительное хранение.

На данный момент исследования идут в нескольких направлениях, и ниже перечислены наиболее перспективные.

- Ферроэлектрическая память ( FRAM, FeRAM или F-RAM )

- Ферроэлектрики - аналоги ферромагнетикам. Они хранят состояние магнитной поляризации. Основная идея: создать аналог 1T1C ячейки, заменив конденсатор кусочком ферроэлектрического материала ( плёнка толщиной несколько молекул стронция поверх титаната висмута ). Так же, как в динамической памяти, бит записывается с помощью поля, приложенного к элементу хранения. Отличия в чтении: оно «деструктивное» и выполняется через подачу тока записи одновременно с наблюдением за поведением элемента ( меняется или нет его состояние: при смене состояния возникает импульс тока 41 ). FRAM может обеспечить скорость чтения/записи на уровне десятков наносекунд, хранение в течение десятков лет и очень высокий [* хотя и не бесконечный, как у SRAM и DRAM ] ресурс. Fujitsu и Cypress выпускают FRAM в виде ИМС с последовательным ( SPI или I2C ) и с параллельным интерфейсом ( эмуляция SRAM ), объёмом до 4 Mb . Заявленное число циклов считывания \(10^{14}\). Например, MB85RE4M2T имеет время доступа на чтение и запись 150 ns , срок хранения 10 лет при 85°C и \(10^{13}\) циклов считывания ( это 300 лет по 1000 циклов запись-чтение в секунду.

==1026

- Магниторезистивная память ( MRAM )

-

Магниторезистивный эффект - изменение электрической проводимости материала под действием магнитного поля. Разные варианты этого явления ( «гигантский магниторезистивный эффект» , «туннельная магниторезистивность» ) используются в считывающих головках магнитных дисков. Такие головки имеют существенные преимущества перед традиционными магнитными катушками ( в катушке ЭДС меняется пропорционально изменению потока, на не самой величине этого потока ) и «виновны» во взрывном увеличении ёмкости жёстких дисков в последние годы. Сейчас возможно формировать на кристалле магниторезистивные элементы в готовом для использования виде ( с ферромагнетиком ). Писать в него можно импульсом тока, а считывать с помощью магниторезистивного эффекта.

MRAM была в разработке многие годы и уже присутствует на рынке. Например, компания Everspin, отпочковавшаяся от Freescale, предлагает 8- и 16-разрядную MRAM ёмкостью 16 Mb . Например, MR2A16A - 16 -разрядная память на 4 Mb с интерфейсом асинхронной SRAM, скоростью записи и чтения 35 ns , временем хранения 20 лет и заявленным неограниченным числом циклов стирания-записи. Цена в розницу $20. MRAM предлагают Hitachi, Hynix, IBM/TDK, Infineon, Samsung и Toshiba/NEC ( вроде, уже есть 1 Gb MRAM ). MRAM - не конкурент флэш-памяти: цена слишком велика, а технология всё ещё в разработке, но присматривать за ней будет полезно.

- Память на разнице фаз ( PRAM или PCM )

- Некоторые металлические сплавы ( халькогенидное стекло ) имеют большую разницу электрических сопротивлений в кристаллическом и аморфном ( стеклоподобном ) состоянии. Это свойство можно использовать для создания элемента памяти. Изменение фазового состояния производится с помощью нагрева. Может показаться, что нагрев протекает медленно и постепенно, захватывая большие объёмы, но в нанометровых масшабах процесс протекает локально и очень быстро ( десятки наносекунд ). Над фазовой памятью работают компании Samsung, Micron, IBM и STMicroelectronics. Первые прототипы уже появились ( 128 Mb PRAM фирмы Numonyx ). Заявок на бесконечное число циклов пока нет, но потенциально эта технология позволяет создать память высокой плотности с быстрым доступом.

14.4.6 Итоговый обзор памяти

Подводя черту под затянувшимся обсуждением, можно сделать несколько итоговых наблюдений.

-

Во-первых, все проблемы с памятью обычно уже решены.

- Микроконтроллеры ( Часть 15 ) уже имеют на борту постоянную ( флэш ) и оперативную SRAM, а часто и постоянную EEPROM ( параметры, настройки и т.д. ).

- Материнские платы компьютеров используют SDRAM в виде вставных модулей ( SODIMM и др. форматы ). При общении с ними требуется только следовать руководствам по подбору моделей.

- Программируемая логика ( FPGA ) без внутрикристальной флэш-памяти загружает конфигурацию из специальной последовательной памяти, протокол общения с которой подробно расписан в руководстве пользователя. [* К сожалению, того же нельзя сказать про формат прошивки ] .

- Проще всего работать с асинхронной статической памятью либо имитирующими её разновидностями, например, псевдостатической. Скорость доступа для обычной SRAM и PSRAM составляет 50 ns , а для быстрой статики - менее 10 ns . Последнюю можно использовать в качестве внешней кэш-памяти. Микропотребляющая статика может хранить данные, расходуя всего ∼1μA тока, а при умеренной частоте обращения потребляет около 1 mA .

- Синхронная статическая память имеет более сложное управление, но работает быстрее ( до 400 MHz и с удвоенной скоростью выдачи данных ). Хорошо подходит для внешнего кэша.

- Синхронная динамическая память, а конкретно модели с удвоенной частотой выдачи данных, являются основной оперативной памятью современных компьютеров. Чаще всего оформляется в виде модулей, но в законченных устройствах - роутерах, игровых приставках, дисплеях - отдельные микросхемы распаиваются прямо на плату.

- Флэш с организацией NAND - современный победитель в номинации постоянной памяти большой ёмкости ( USB накопители, CF, SD карты и твердотельные заменители жёстких дисков - SSD ). Она же хранит программы в микроконтроллерах и одноплатных вычислительных устройствах ( потребительская электроника, видеосистемы, сетевые устройства и т.п. ). Особенно удобна в использовании постоянная память с последовательным интерфейсом, которая может оформляться как в виде отдельных ИМС, так и виде SD-карт ( имеющих SPI-совместимый протокол обмена и удобных для подключения к микроконтроллеру напрямую ).

==1027

- Флэш-память с организацией NOR имеет все преимущества обычной асинхронной памяти и допускает непосредственное исполнение записанного в неё кода.

- EEPROM с возможностью побайтового изменения данных очень удобна для хранения параметров и настроек, когда объём последних невелик.

- Есть надежда, что новые технологии позволят создать постоянную память с неограниченным числом циклов стирания-записи-чтения. ( Такая память уже была: это память на магнитных кольцах. В ней всё отлично, если времена обращения в микросекундах, емкость в килобайтах, а цена в килодолларах устраивают [* ещё и энергопотребление/тепловыделение в ваттах, соответственно, медные теплоотводы и вес в килограммах ] . Но все развращены скоростью, плотностью и низкой ценой полупроводниковых решений. Пути назад нет ).

==1027

26 Имеющую слишком много параметров: форм-фактор ( SIMM, RDIMM, SODIMM ), число контактов ( 200, 204, 240 ), ширина шины данных, наличие ECC, наличие буфера, поколение памяти ( SDR, DDR, DDR2, DDR3, DDR4 ), частота тактового сигнала ( например, PC3-10600 ) и скорость передачи данных, латентность CAS, напряжение питания, одно- или двустороннее исполнение, регистровый или нерегистровый выход и чётность. Возможных вариантов буквально сотни, причём большая часть не подойдёт какой-то конкретной материнской плате. Для примера, данная сноска писалась на машине с четырьмя банками памяти по 1 GB 64-разрядной DDR2 PC2-6400, латентность CL=4 ( 5-5-5-15-2T ), напряжение питания 1.9 V небуферированной SDRAM без контроля чётности и без ECC, упакованной в SODIMM с 240 выводами. <-

27 В небольших системах, например, в микроконтроллерах, которые рассматриваются в Части 15 , «накопителем» чаще всего выступает обычная флэш-память, помещённая прямо на кристалл процессора. <-

28 В оперативной памяти нет износа - содержимое можно читать и писать без ограничений. <-

29 Книга следует общеупотребительному стилю наименований: «Mb» - мегабит или \(2^{20}\) битов ( примерно на 5% больше, чем десятичный миллион ( \(10\space^6\) ). Пуристы предпочитают для \(2^{20}\) префикс «Mi» ( произносится «mebi» - сокращение от «mega binary» ), оставляя «мега» за давно знакомым десятичным миллионом. [* Правило используется без фанатизма. Пуристы негодуют ] . С другой стороны, «мебибайт» звучит, как будто у говорящего каша во рту. <-

30 Аналогичной модификации можно подвергнуть и динамическую память, получив синхронную DRAM самых разных форм и расцветок: SDR - однократной скорости, DDR - удвоенной скорости, DDR3, DDR4 и т.д. - удвоенной скорости с улучшенными параметрами. <-

31 Правильнее сказать в этом месяце . Закон Мура продолжает неумолимую поступь уже четвёртое десятилетие, и указанные выше цифры устареют раньше, чем высохнут чернила на рукописи. <-

32 Есть дополнительные режимы, сопровождающиеся словами «страничный», «с расширенной выдачей данных», которые позволяют читать данные из нескольких последовательных ячеек памяти. <-

33 В реальной жизни дело обстоит ещё сложнее. Усилители считывания дифференциальные , и массив конденсаторов включается «через ряд»: система организована так, чтобы линии рядов активировали либо чётные, либо нечётные ячейки. Отключённые в данном цикле ячейки задают «опорный» уровень дифференциального усилителя ( \(V_{DD}\)/2 ), позволяя получить разный знак при ΔV заряженной и разряженной ячейки относительно опорного уровня. Реальная разница получается меньше ожидаемых ±0.5 V . Она уменьшается за счёт паразитных емкостей самого усилителя и линий связи ( ∼200 fF ). Разработчики ИМС памяти ориентируются на цифру ΔV>100 mV , которая позволяет надёжно отличить «0» от «1». <-

34 На таких высоких частотах он может быть только низковольтовым дифференциальным ( «CK & CK'» ) <-

35 Что не вполне тривиальная задача. Авторам встречались материнские платы именитых марок, забывавшие все настройки уже после нескольких часов отсутствия сетевого напряжения. Довольно неудобное обстоятельство, т.к. в КМОП часах хранится порядка 25 необходимых параметров [* не считая времени ] . Скорее всего, проблема появлялась из-за микросхем с повышенным током утечки или слишком высоким минимальным уровнем напряжения хранения. <-

36 Другое имя EAROM – «электрически изменяемая память только для чтения». <-

37 Аналогия из макромира [* в книге уже встречалась столь же наглядная аналогия, см. примечание #34 на стр. 40 ] . Требуется передать оксикарту через Киберпасс , но из-за плохой подготовки оксов у вас нет. Надеясь на чудо, вы суёте карту в считыватель. Согласно принципам квантовой механики, существует ненулевая вероятность, что карточка исчезнет из вашей руки и появится на другой стороне киберпасса. Для оксикарты эта вероятность исчезающе мала ( и это ещё мягко сказано ! ), но подобная схема неплохо работает в случае электронов, способных проскочить на глубоко запрятанный затвор. [* Что, и здесь Лебовский !? ] . <-

38 Реальный обмен данными с SD-картой - занятие не самое простое. Процесс состоит из множества элементарных операций: чтения, стирания, записи, проверки состояния и т.п. С другой стороны, он вполне однозначен, а библиотеки под популярные микроконтроллеры ( Часть 15 ) AVR и ARM упрощают задачу. <-

39 Тем не менее, это реальная технология. Несколько гигабайт картинок и текста этой редакции книги неоднократно путешествовали между домом и офисом в виде набора из частично заряженных фемтоамперных емкостей. <-

40 Можно сделать обоснованное предположение, что, когда вы будете читать этот текст, число байт в одной микросхеме многократно превысит число жителей земли. <-

41 Процесс аналогичен общению с памятью на магнитных кольцах из технологического мезозоя. Их состояние выяснялось путём перемагничивания с известной полярностью при одновременной фиксации факта изменения состояния ( по появлению импульса тока записи ), если таковое имело место. Затем при необходимости прежнее состояние восстанавливалось. <-