12.1 (I) Сопряжение КМОП и ТТЛ

==790

12.1.1 Логические семейства краткая историческая справка

В доисторические времена в ранние 1960-е годы отчаянные люди, не желающие собирать логические элементы из отдельных транзисторов, сражались с резисторно-транзисторной логикой ( RTL ). Это было простое семейство, предложенное фирмой Fairchild. У него была низкая нагрузочная способность и плохая помехоустойчивость. На рис. 12.1 проблема явлена в графическом виде. Порог переключения всего на одно падение \( V_{BE}\) выше уровня земли, а нагрузочная способность в некоторых случаях ограничивалась всего одним входом, причиной тому была пассивная подтяжка к положительному питанию и низкоомная нагрузка. То было время малой степени интеграции, и самым сложным элементом был сдвоенный D-триггер, способный переключаться на скорости 4 MHz ( если хотите изучить справочные данные самостоятельно, то его обозначение MC790P ). Авторы героически собирали схемы на RTL элементах. Иногда они сбивались только от того, что рядом кто-то включил паяльник.

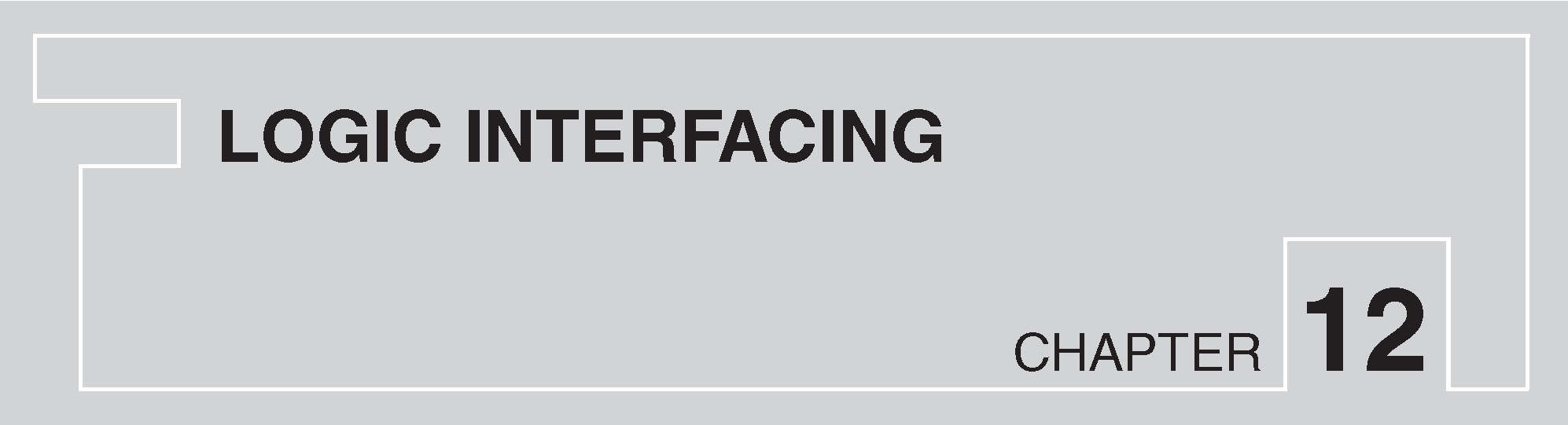

Рис. 12.1 Упрощённая схемотехника нескольких логических семейств

RTL логика вымерла, как только Signetics представила диодно-транзисторную логику ( DTL ), и сразу же Sylvania выкатила SUHL - универсальную скоростную логику имени себя, чуть позже названную транзисторно-транзисторной ( TTL ). Signetics выпустила пользовавшуюся популярностью серию 8000 - DCL Utilogic ( «Путилогика - выбор настоящего дезигнера» ). ТТЛ быстро превратилась в серию 74 в соответствии с фирменным обозначением компании Texas Instruments. Что интересно, биполярная ТТЛ логика на настоящий момент стала достоянием истории, но обозначение «74» и сейчас живее всех живых, перейдя по наследству к КМОП преемникам. На входах логических элементов этого семейства стояли источники вытекающего тока ( в RTL вход потреблял ток ), а логический порог составлял 2\( V_{BE}\) . Выходы обычно делались по псевдосимметричной ( «push-pull» или «totem-pole» ) схеме ( рис. 12.1 ). DTL и TTL начали эру 5-вольтовой логики ( RTL работала при +3.6 V ), работающей на частоте до 25 MHz и имеющей коэффициент разветвления 10 ( десять входов на один выход ). Дезигнеры тут же изменили свой выбор, предпочитая продаться за скорость, надёжность и предложенный набор функций ( подумать только! есть даже делитель на десять в одном корпусе! ). Что ещё может понадобиться разработчику?! ТТЛ будет жить в веках!

Но разработчики - ненасытные твари. Они хотят больше скорости. Они хотят меньшего потребления. И они получат всё. По отдельности. В скоростном сегменте появилась форсированная серия 74Hxx с удвоенной скоростью за удвоенную мощность. Этот феноменальный результат был достигнут за счёт гениального технического приёма: номиналы всех резисторов в ИМС были уменьшены в два раза. Маломощный вариант ТТЛ - серия 74Lxx имела по сравнению с оригинальной 74xx в 4 раза меньшее быстродействие при в 10 раз меньшей мощности. Другое семейство – эмиттерно-связанная логика ( ECL ) имеет и в самом деле высокое быстродействие ( 30 MHz в момент первого появления ). Она использует отрицательный источник питания [* –5.2 V и 0V ] и небольшую разницу между логическими уровнями ( –0.9 и –1.75 V ), потребляет много тока ( 30 mW/вентиль ) и поэтому существует только в виде ИМС малой степени интеграции. [* Упоминающийся в этой части PECL - это обычный ECL, тупо перенесённый в положительную область, т.е. с питанием 0V и +5.2 V ] .

==791

Первое КМОП семейство - серия 4000 было создано фирмой RCA. У него было нулевое потребление в статическом режиме и широкий диапазон питания ( от +3 до +12 V ). Выходной сигнал доходил до обеих шин питания, а входы не потребляли тока. Но при всех этих достоинствах она имела малое быстродействие ( 1 MHz при 5V ) и очень высокую цену ( $20 за корпус с четырьмя вентилями ). Несмотря на высокую цену, на этом семействе выросло целое поколение разработчиков батарейных устройств, просто потому что никаких альтернатив не существовало. Эти ребята хорошо знали, что значит статическое электричество, потому что входы серии 4000 были очень к нему чувствительны.

Таким образом, к началу 1970-х ситуация выглядела так: были две основные линейки биполярной логики ( ТТЛ и ЭСЛ ) и одно КМОП. Все ТТЛ серии были совместимы между собой, но выходы маломощной 74L’ тянули всего 3.6 mA и могли работать только на два входа стандартной 74’ ( 1.6 mA в состоянии НИЗКОГО уровня ). Совместимость между разными семействами не было, если исключить подтяжку на шину питания, которая позволяет передать сигнал из ТТЛ на КМОП с питанием +5V , а выход КМОП, в свою очередь, мог потянуть один вход ТТЛ.

==792

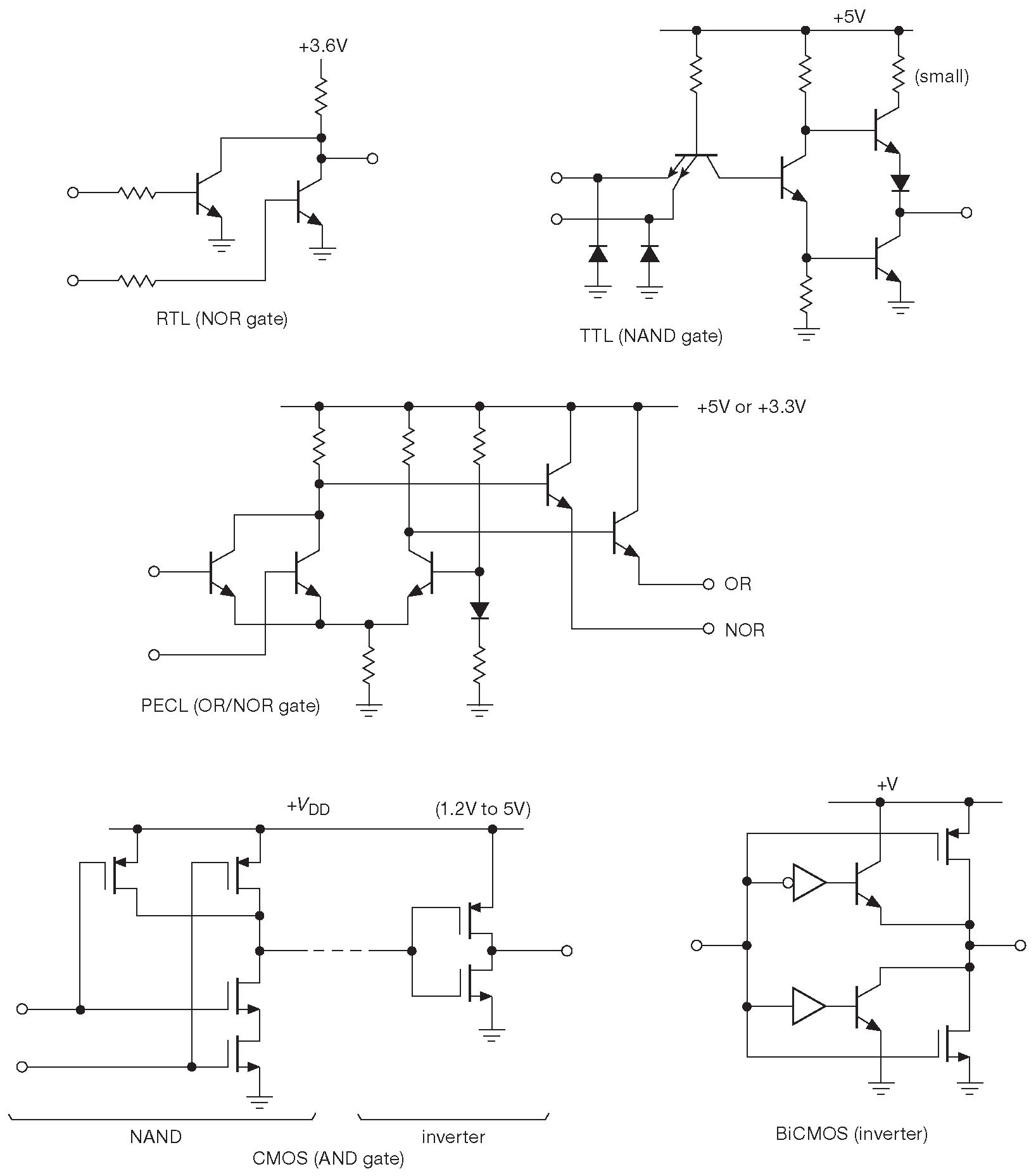

На протяжении 70-х годов шло постоянное улучшение ситуации на всех направлениях. В ТТЛ появилась ненасыщающаяся серия с диодами Шоттки 74S’ , которая предложила 3× увеличение скорости за 2× питание, и сразу убила 74H’. Затем появилась серия маломощных Шоттки - 74LS’ , которая удавила классические 74’, т.к. имела такое же быстродействие при 5× меньшем потреблении. Жизнь с 74S’ и 74LS’ была прекрасна, но Fairchild выпустила 74F’ . Она была в 2× раза быстрее и имела в 3× меньшее потребление, чем 74S’, плюс имела всякие дополнительные удобства, облегчающие разработку. Texas Instruments - разработчик оригинальной серии 74’ выпустил парочку новых: 74AS’ и 74ALS’ . Первое шло на смену 74S’, второе - 74LS’. Все ТТЛ серии имели одинаковые логические уровни и достаточную мощность выхода, что позволяло использовать их в одной схеме совершенно свободно. Табл. 10.1 и рис. 12.2 показывают скорость и мощность всех цифровых микросхем.

Рис. 12.2 Задержка вентиля различных логических семейств в зависимости от рассеиваемой мощности. Потребление зависит от напряжения питания и частоты переключения: \( P=C_{pd}·Vcc^2·f\) , где \( C_{pd}\) называется «ёмкостью, рассеивающей мощность» ( \( C_{pd}\) не включает ёмкость внешних соединений и нагрузки ). КМОП семейство допускает работу в широком диапазоне напряжений, а биполярная логика работает при оговоренных уровнях питания ( +3.3 или +5V ). Серии, отмеченные курсивом доступны в корпусе DIP. См. также табл. 10.1 и рис. 12.3

Тем временем серия 4000 эволюционировала в улучшенную 4000B с более широким диапазоном питания ( 3...18 V ), усиленной защитой входов и более высоким быстродействием ( 3.5 MHz при 5V ). Появилась серия 74C, которая по внутреннему устройству повторяла 4000B, а по разводке микросхем - серию 74, чтобы получить дополнительные преимущества от фантастической популярности последней. ЭСЛ пошёл по пути ECL II, ECL III, ECL 10'000 и ECL 100'000. Рабочая частота последней достигала 500 MHz .

На начало 1980-х ситуация была следующей. Большая часть разработок шла на 74LS’ с добавлением 74F’ ( или 74AS’ ) в местах, где требовалось повышенное быстродействие. Те же схемы ТТЛ использовались в качестве «обвязки» для n-МОП процессоров, входы и выходы которых совпадали по уровням с ТТЛ. Малопотребляющие разработки велись на 4000B или 74C’, которые совпадали друг с другом по входам и выходам. На скоростях выше 100 MHz царили ЭСЛ. Схемы, использующие разные семейства встречались редко, исключая отдельные сочетания КМОП-ТТЛ и ТТЛ-ЭСЛ.

В 80-х появились КМОП микросхемы, совместимые по скорости и нагрузочной способности с ТТЛ. Первыми были 74HC’ . У них было быстродействие 74LS’ при по-прежнему нулевом потреблении в статике. Затем появились 74AC’ со скоростью 74F’ и 74AS’. Их выходы переключались между потенциалами питания, а порог переключения располагался посередине. Т.е. новые серии сочетали лучшие параметры предшественников ТТЛ и КМОП и вскоре полностью заместили биполярные ТТЛ. Но на стыке между новыми сериями и старой логикой были определённые проблемы с совместимостью: минимального гарантированного напряжения выходного ВЫСОКОГО уровня биполярных ТТЛ и сложных микросхем, выполненных по n-МОП технологии, не хватало для переключения 74HC’ и 74AC’, которым требовалось не менее 3.5 V .

==793

Для решения этой проблемы были созданы серии 74HCT’ и 74ACT’ с порогом переключения ТТЛ. В течение 80-х ИМС большой степени интеграции ( LSI ) и сверхбольшой степени интеграции ( VLSI ) - микропроцессоры, память и т.п. перешли с технологии n-МОП на КМОП. У них сильно снизилась потребляемая мощность и появилась совместимость с КМОП логикой по входам/выходам. Всё это происходило на фоне увеличения быстродействия и сложности. В сегменте сверхбыстрых схем появилась арсенид-галлиевая технология ( GaAs ), предложенная компаниями GigaBit Logic и Vitesse. Здесь скорость подошла к 3 GHz .

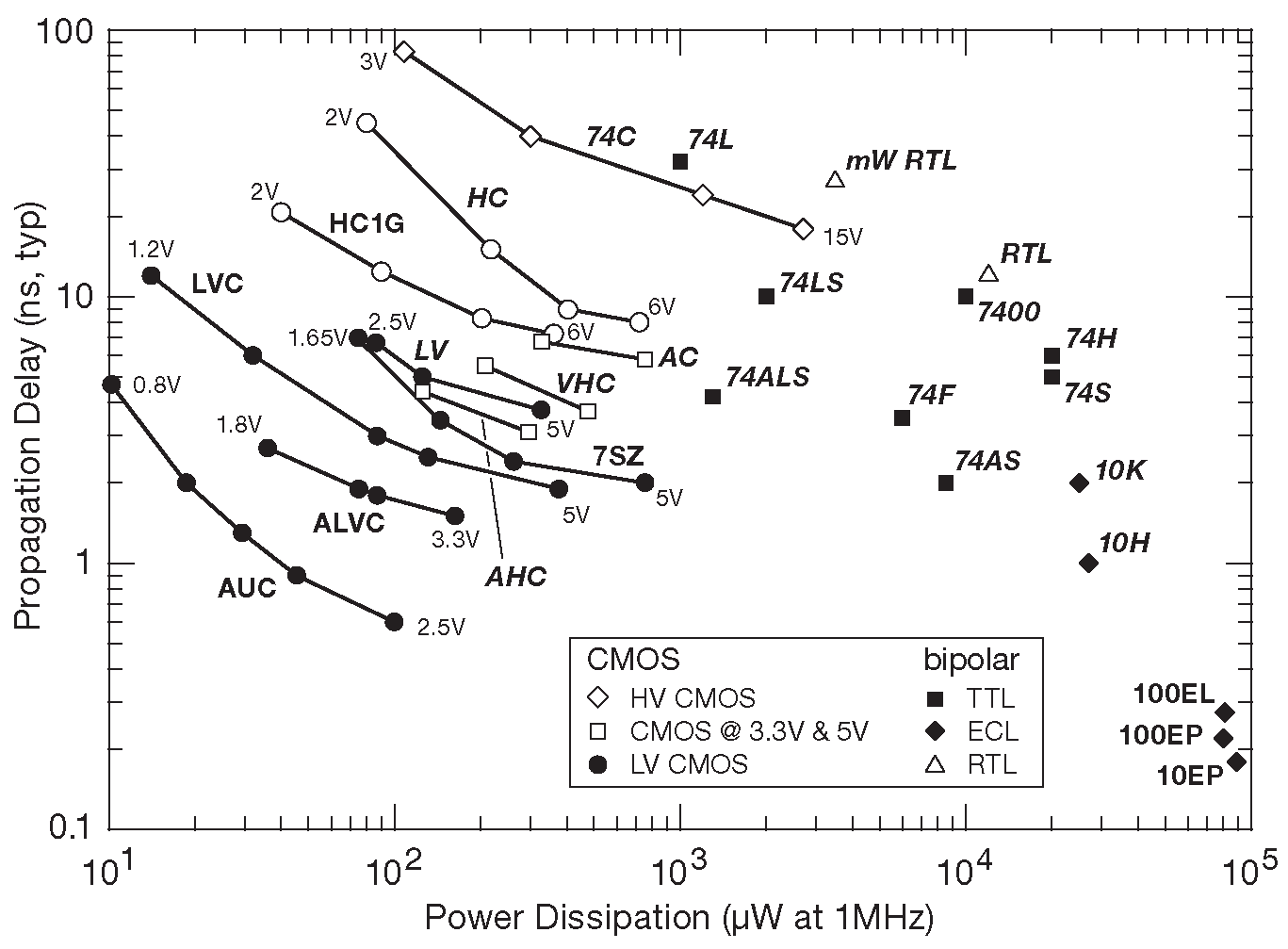

Следующие двадцать лет ситуация развивалась поступательно. Основные изменения касались увеличения производительности КМОП за счёт масштабного уменьшения геометрических размеров кристаллов. Во-первых, за счёт уменьшения геометрических размеров стало возможно разместить на той же площади больше транзисторов. Это позволило наладить выпуск мощных процессоров, памяти большого объёма и сложных специализированных микросхем ( например, видео ). Общее число транзисторов на одном кристалле перешагнуло миллион и вплотную приблизилось к миллиарду. Во-вторых, масштабное сокращение размеров увеличило быстродействие, понизило рабочее напряжение и потребляемую мощность в пересчёте на один вентиль _1 . Появились новые серии низковольтной КМОП логики 74LVC’, 74AUC’ и т.д., см. рис. 12.3 . Задержка распространения сигнала ( от одного вывода до другого ) в них снизилась до субнаносекундных величин, повысив рабочую частоту до сотен мегагерц.

Рис. 12.3 Скорость вентилей в зависимости от напряжения питания для популярных логических семейств. Максимальное время задержки распространения \( t_{pd}\)(max) показано для стандартного напряжения питания каждого семейства. ( В качестве грубой оценки «типичные задержки» составляют 35...75% от \( t_{pd}\)(max)). Кружками отмечены серии, для которых \( V_{in}(max)\) ограничено напряжением питания \( V_{supply}\space\) , а данные указаны для 25°C . Ромбами - серии с «5V-совместимыми» входами ( \( V_{in}\) < 5.5 V , независимо от уровня питания ), а данные приводятся для «промышленного» температурного диапазона ( –40...+85°C ). Квадратами – «3.3 V-совместимые» ( \( V_{in}\) < 3.6 V ) в «промышленном» диапазоне температур. Некоторые серии, например LVC’, имеют выходные каскады, которые в отсутствие питания не оказывают влияния на подключённые сигнальные линии. Графики предполагают нагрузочную ёмкость \( C_L\) =50 pF для 5 и 3.3 V, 30 pF для 2.5 и 1.8 V, 15 pF для 1.5 V и ниже ( исключение: маркировка ** для 50 pF и * для 15 pF ). КМОП серия 4000 включалась при +15 V , когда \( t_{pd}(max)\) =70 ns . Очень немногие члены семейства LVC’ могут работать при +5V . Быстрые ( и прожорливые ) биполярные ЭСЛ серии, работающие только при 5V , не показаны. Максимальная задержка на вентиль 600 ps ( 10E’ ), 440 ps ( 10EL’ ) и 320 ps ( 10EP’ ). Некоторые серии развились в «улучшенные» версии, например, LVC’ - LVCE’, которые работают при напряжениях вплоть до 1.4 V и на 30% быстрее. См. также рис. 10.22 и §10.2.3

Новые быстрые КМОП серии стремительно размножались, порождая целый зоопарк из десятков обозначений. Многие новые разработки функционируют при низких напряжениях, например, для 74LVC’ это от 1.8 до 5V , их входы допускают сигналы, превышающие уровень положительного питания. Упомянутая 74LVC’ является «5V-совместимой», т.е. допускает на входе уровень +5V независимо от величины напряжения питания, см. рис. 12.3 . Высокая степень интеграции современных VLSI компонентов практически не требует использования стандартных логических микросхем. Лишь иногда возникает нужда в одиночных вентилях. Данная ситуация вызвала появление отдельных логических элементов, упакованных в небольшие корпуса. Такие микросхемы имеют торговое название TinyLogic, Little Logic, MiniGate или PicoGate.

Преимуществом мелких корпусов является низкая индуктивность выводов питания, снижающая «выбросы по земле» ( см. §10.8.3 и рис. 10.99 ) и прочие симптомы переходных процессов, порождаемых резкими фронтами, проходящими через сложные реактивные составляющие нагрузок и соединений. Токовые иголки стали серьёзной проблемой в 90-х, когда разработчики столкнулись с сочетанием новых семейств 74AC’, 74ACT’, 5-вольтовым питанием и таким же размахом сигналов, а так же стандартными корпусами DIP с угловым расположением выводов питания. Некоторые производители микросхем ( особенно TI ) пытались снизить остроту проблемы, добавляя дополнительные выводы питания в центр корпуса. В итоге стандартные элементы получали новые обозначения ( типа 74AC11004 для стандартного инвертора ’04 ) и новые корпуса ( DIP20 вместо DIP14 в данном случае ). Другие фирмы пытались создать «тихие» варианты логических микросхем за счёт контролируемой скорости нарастания выходных сигналов ( серия 74ACTQ’ от FSC/NSC ). Ситуация существенно улучшилась при переходе на низкие уровни питания, корпуса для поверхностного монтажа с низкой индуктивностью выводов и новые методики разводки печатных плат ( использование многослойных плат с выделенными слоями питания и земли ). С активным внедрением низковольтовых дифференциальных шин передачи сигналов ( LVDS ) проблема исчезла практически полностью, как за счёт противофазного изменения направления токов, так и из-за общего низкого уровня сигналов ( ∼0.4 V ).

Все КМОП семейства стандартной логики, начиная с 4000, HC’, LVC’, AUC’ и далее везде, имеют нулевое потребление в «статике» ( т.е. когда состояние элемента не изменяется ). Типовой ток в таком режиме меньше микроампера. Но КМОП схемы имеют большой «динамический» ток при переключении состояний. Он является комбинацией двух эффектов:

- броски от сквозного тока между шинами питания при переключении внутренних каскадов в момент перехода сигнала через пороговый потенциал и

- ток перезарядки внутренних и внешних емкостей.

Динамический ток пропорционален частоте переключения и рядом с максимальными рабочими частотами может соперничать с потреблением биполярной логики, см. Часть 10 и рис. 10.27 . Следует отметить, что, хотя многие VLSI компоненты ( FPGA и cPLD, см. Часть 11 ) выполнены по КМОП технологии, они часто имеют заметный ток покоя. Ситуация постепенно меняется из-за выраженной тенденции к использованию микропотребляющих компонентов в устройствах с батарейным питанием.

==794

Завершим краткую историческую справку некоторыми рекомендациями.

- В простых цифровых схемах, которые можно легко собрать на макетной плате, не требующие ( и не предполагающие ) умопомрачительных скоростей, используйте 74HC’ или 74HCT’ ( последнюю - для совместимости с «ТТЛ уровнями» и сигналами, приходящими с 3.3-вольтовых схем ). Данные серии можно заменить на 74AC’/ACT’/ACTQ’, если нужно больше скорости. Но не стоит забывать о помехах в цепях питания.

- Для низковольтовых систем с микроконтроллерами или иными сложными ИМС, где требуются небольшая обвязка или отдельные быстрые вентили, используйте универсальную серию 74LVC’, но учтите, что она выпускается только в корпусах для поверхностного монтажа. Эта серия удобна для связи цифровых ИМС с разными уровнями питания.

- Если требуется иметь 5-вольтовые выходы в низковольтовых схемах ( например, для управления светодиодами или твёрдотельным реле ), используйте 74HCT’.

- Если нужна быстрая последовательная линия передачи, используйте дифференциальные драйверы и приёмники LVDS ( или низковольтовый PECL - LVPECL ) или SERDES - последовательно-параллельные преобразователи.

- Если нужен широкий диапазон питания, например, устройство с прямым подключением к батарее «9V» , а скорость не важна, используйте старую серию 4000B.

- И, наконец, используйте cPLD, микроконтроллеры, FPGA, а не дискретную логику: это экономит выводы, упрощает разводку и даёт свободу при проектировании.

12.1.2 Входные и выходные характеристики

==795

Цифровые логические семейства проектируются так, чтобы выходной сигнал микросхемы можно было подавать одновременно на много входов того же семейства, запитанного от того же напряжения. Типичная нагрузочная способность составляет не менее 10 входов. Это значит, что выход логического элемента, например, триггера можно завести на 10 входов, причём сигнал останется в оговоренных спецификацией пределах _2 . Другими словами, разработку цифровых схем можно вести, нечего не зная об электрических параметрах используемых микросхем, до тех пор, пока соединяются между собой только логические микросхемы одной серии. На практике это означает, что разработчику можно не волноваться о событиях на входах и выходах.

Но как только возникает нужда в подключении к цифровой схеме внешнего сигнала, безразлично, цифрового или аналогового, либо в выведении логического сигнала на внешнее устройство, возникает необходимость вникнуть в детали. Более того, знать параметры входов и выходов необходимо и в том случае, когда в схеме смешиваются элементы разных семейств, либо вентили одной серии, но с разными уровнями питания. Сопряжение логических микросхем разных семейств между собой - не академический вопрос. Ответ не него необходим при подключении к VLSI или при желании задействовать уникальные возможности конкретной микросхемы конкретной серии. В следующих параграфах будут детально разбираться параметры входов и выходов, рассматриваться примеры соединения различных логических семейств и подключения цифровых схем к внешнему миру.

12.1.2.A Входные характеристики

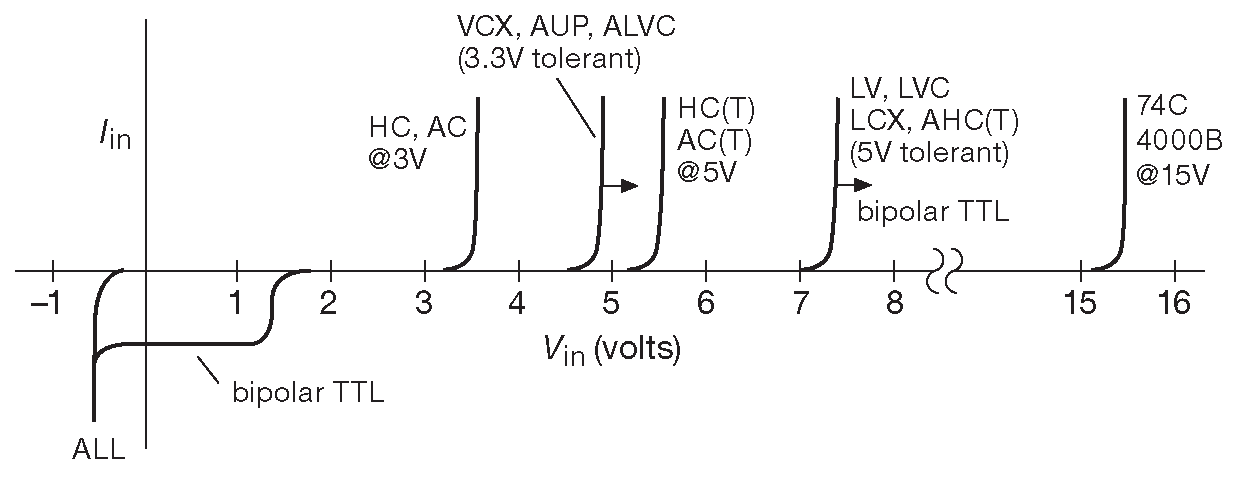

Графики на рис. 12.4 и 12.5 показывают важные параметры цифровых входов: входной ток и выходное напряжение ( для инвертора ), как функции входного напряжения. Графики будут продолжены за пределы нормальной рабочей области цифрового устройства, потому что в интерфейсных схемах входные сигналы легко могут выйти за уровни питания. Все графики предполагают, что КМОП и ТТЛ логика работает с выводом отрицательного питания, подключённым к земле.

Входной ток ( рис. 12.4 )

Рис. 12.4 Входной ток логического элемента в зависимости от напряжения на нём. Если исключить биполярные ТТЛ, то ни у одного семейства нет статического входного тока, если входной сигнал укладывается в номинальное напряжение. Во всех семействах есть внутренние защитные диоды на землю. В некоторых, например в 74HC’, они ограничивают входной сигнал ещё и на уровне положительного питания, т.е. сигнал, превышающий V+ более чем на одно падение на p-n переходе, вызывает появление входного тока через ограничительный диод. Более современные семейства, например, 74LVC’ и 74AUP’ используют защиту стабилитронного типа и допускают уход напряжения на входе за уровень положительного питания. Такое свойство называется «5-вольтовая совместимость» ( LVC’ ) или «3.3-вольтовая совместимость» ( AUP’ ). Описанное положение сохраняется, даже если питание на микросхему не подано ( а старая серия 74HC’ в таком случае начнёт ограничивать сигнал на уровне ( \( V_+\)+0.6 V ), заставляя ВЫСОКИЙ входной сигнал поднимать потенциал шины питания ) [* через защитный диод ]

БОльшая часть современных цифровых микросхем относится к КМОП логике. Её входы ток не потребляют, если напряжение на них попадает в диапазон земля-напряжение питания ( ток утечки затвора не уровне \(10^{-5}\)μA тип. не учитывается ) _3 . Для сигналов большего размаха вход выглядит как ограничительный диод на соответствующую шину питания ( 74HCT’ ) или как ограничительный стабилитрон, который позволяет сигналу выходить за уровень положительного питания ( «5V-совместимые» 74LVC’ ), подробности см. на рис. 12.3 и 12.4 . Пиковые токи через ограничительный элемент, превышающие 20...50 mA , разрушают его и вызывают эффект, известный как «тиристорное защёлкивание» ( §10.8.3.B ). Спецификации указывают соответствующие цифры в разделе «Предельные максимальные значения» .

==796

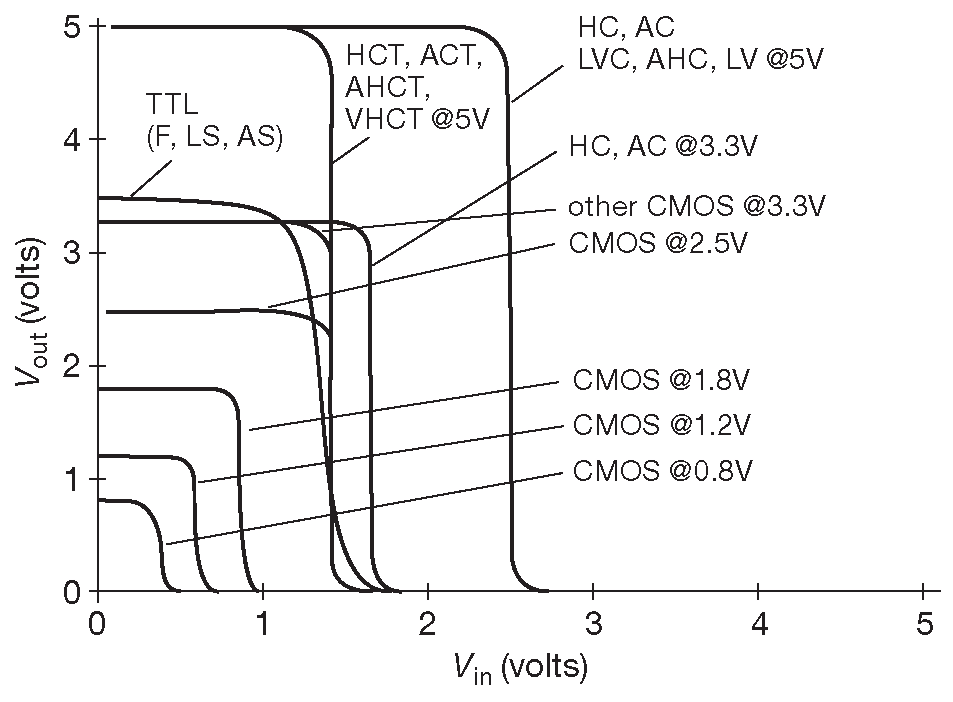

Порог переключения ( рис. 12.5 и 12.6 )

Рис. 12.5 Зависимость выходного напряжения от напряжения на входе ( «функция передачи» ) для логических инверторов нескольких популярных серий. В общем случае КМОП семейства, рассчитанные на питание 2.5 V или менее, имеют порог переключения на половине питания. БОльшая часть логических микросхем и сложных кристаллов, типа микроконтроллеров или программируемой логики, рассчитанных на более высокие напряжения питания, следуют спецификации ТТЛ. В соответствии с ней порог переключения располагается где-то между уровнями 0.8 и 2.0 V ( типовое значение 1.3—1.5 V ). Серии HC’/AC’/4000B - исключения. Их порог лежит на половине питания

Напряжение переключения логического состояния ( граница между НИЗКИМ и ВЫСОКИМ уровнями ) зависит как от конкретного логического семейства, так и от уровня питания ( для тех ИМС, у которых допускается широкий диапазон напряжений, см. рис. 12.3 ). В данном вопросе решающее слово остаётся за справочными данными, но общее представление о ситуации дать можно.

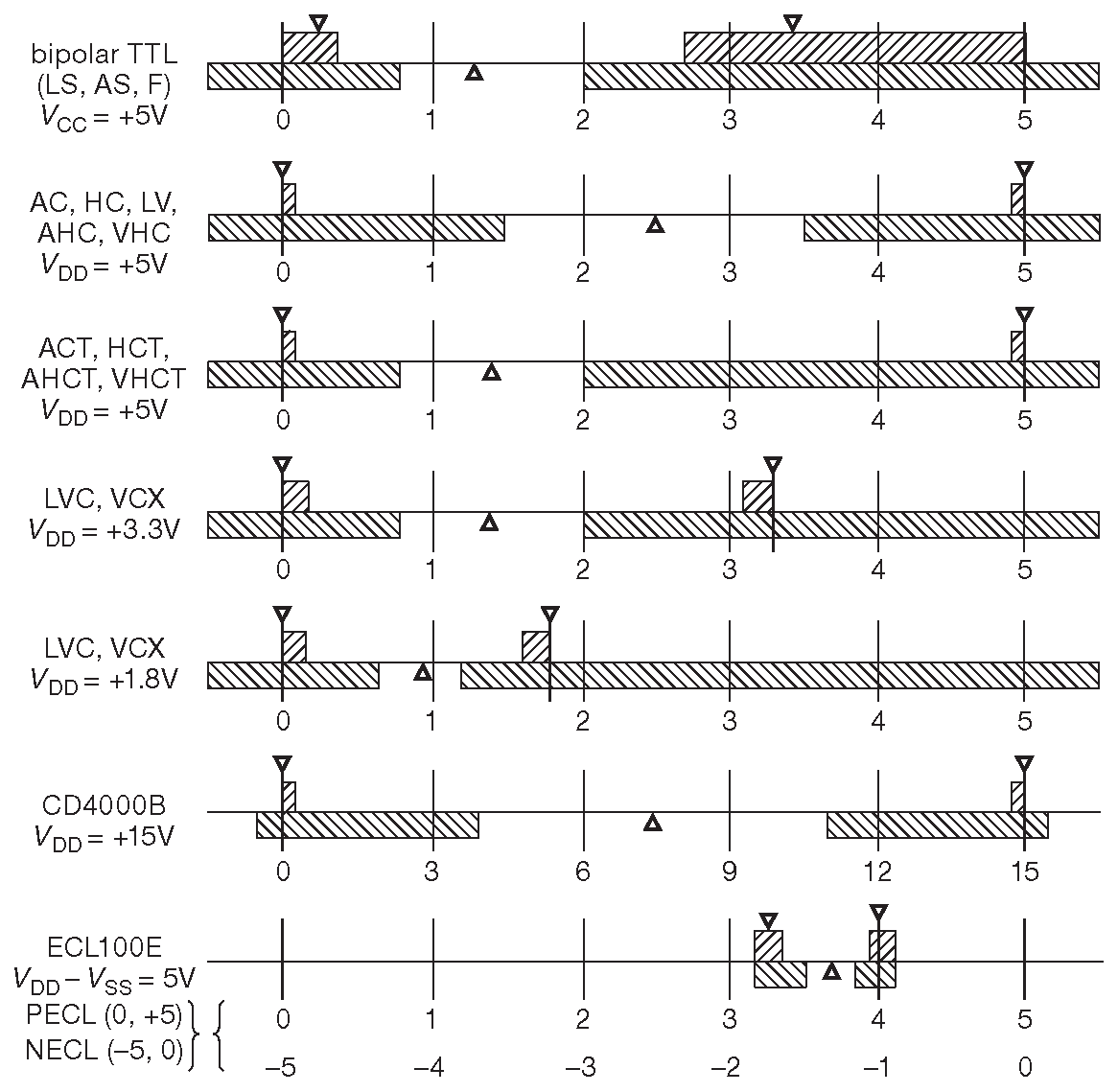

Рис. 12.6 Диапазоны напряжений, соответствующие ВЫСОКОМУ и НИЗКОМУ логическому уровню популярных цифровых семейств. Заштрихованные области выше оси обозначают специфицированный диапазон, соответствующий указанным логическим уровням, куда гарантированно попадает выходное напряжение, а стрелки указывают значения, чаще всего встречающиеся на практике. Заштрихованные области под осью показывают диапазон напряжений на входе, которые будут гарантированно интерпретированы как НИЗКИЙ и ВЫСОКИЙ уровень, а стрелкой указан типичный уровень переключения , т.е. граница между двумя логическими состояниями. Во всех случаях ВЫСОКИЙ уровень более положителен, чем НИЗКИЙ. Дополнительную информацию можно найти в табл. 10.1 и на рис. 12.3 , см. также рис. 12.135

- Достаточное число логических семейств выполняют рекомендации, известные как «ТТЛ уровни» старых биполярных микросхем родом из 1960-х: \( V_{in}\) < 0.8 V однозначно воспринимается как НИЗКИЙ логический уровень, а \( V_{in}\) > 2.0 V - столь же однозначно как ВЫСОКИЙ. Сигналы, подаваемые на такие микросхемы, желательно отодвинуть от указанных границ, чтобы обеспечить должную защиту от помех. Типовой НИЗКИЙ уровень должен быть ниже 0.4 V , а ВЫСОКИЙ - выше +2.4 V . Порог собственно переключения попадает в зону от 1.35 до 1.5 V _4 . В число распространённых логических семейств с ТТЛ уровнями, кроме собственно ТТЛ серий 74F’, 74LS’ и 74AS’, попадают 74HCT’, 74ACT’, 74AHCT’ и 74VHCT’ ( расширение «-T» обозначает чётко обозначенные входные ТТЛ уровни, вместо естественного для КМОП переключения на половине питания, как у серий 74HC’, 74AC’, 74AHC’ и 74VHC’ ). Что интересно, многие современные сложные микросхемы, в частности программируемая логика ( Часть 11 ) и микроконтроллеры ( Часть 15 ), продолжают соблюдать требования ТТЛ спецификации к логическим порогам ( НИЗКИЙ = 0.8 V или ниже, ВЫСОКИЙ = 2.4 V или выше ).

- Варианты не обладающие «ТТЛ совместимостью» имеют порог переключения где-то в районе половины питания \( V_+\)/2 . Это верно и для старых КМОП серий 4000B/74C’, которые работают при напряжениях 3...18 V , и для современных низковольтных разработок 74LVC’, 74AUC’. Здесь следует учитывать, что актуальный уровень переключения таких микросхем, оговоренный спецификацией, может лежать в широком диапазоне от (1/3)\( V_+\) до (2/3)\( V_+\) ( \( V_+\) при этом может называться «Vcc» или «Vdd» ).

12.1.2.B Выходные характеристики

Выходной каскад КМОП логики практически всегда использует комплементарную пару МОП транзисторов, включающихся попеременно ( рис. 12.1 ). Исходно выход виден как сопротивление \(R_{ON}\) канала на землю или V+ . Если нагрузка слишком велика, и напряжение отошло от соответствующего уровня более чем на 1V , выход начинает выглядеть как источник тока. Типичная величина \(R_{ON}\) составляет 30 Ω для 74HC(T)’ при +5V, 12 Ω для 74AC(T)’ при +5V, 10 Ω/15 Ω ( приём/отдача ) для 74LVC’ при +3.3 V и 200 Ω для 4000B при +15 V _5 .

Выходная схема биполярных ТТЛ микросхем ( вымирающий вид ) использует в нижнем плече npn ключ, а в верхнем - npn повторитель ( или схему Дарлингтона ) с ограничительным резистором в коллекторе. Один транзистор насыщен, другой выключен. В результате ТТЛ выход может принимать приличный ток ( 8 mA для 74LS’ и 24 mA для 74F’ ) по НИЗКОМУ уровню с небольшим напряжением насыщения, но на ВЫСОКОМ уровне отдаёт незначительный ток при напряжении не выше ( \( V_+\)–1.5 V ) ( см. графики для 74AS’ и 74LS’ на рис. 12.7 ). Выход, рассчитанный на работу с биполярными ТТЛ или с «ТТЛ совместимыми» микросхемами ( < 0.8 V в состоянии НИЗКИЙ и > 2.0 V в состоянии ВЫСОКИЙ ) имеет нагрузочную способность 10 входов.

==797

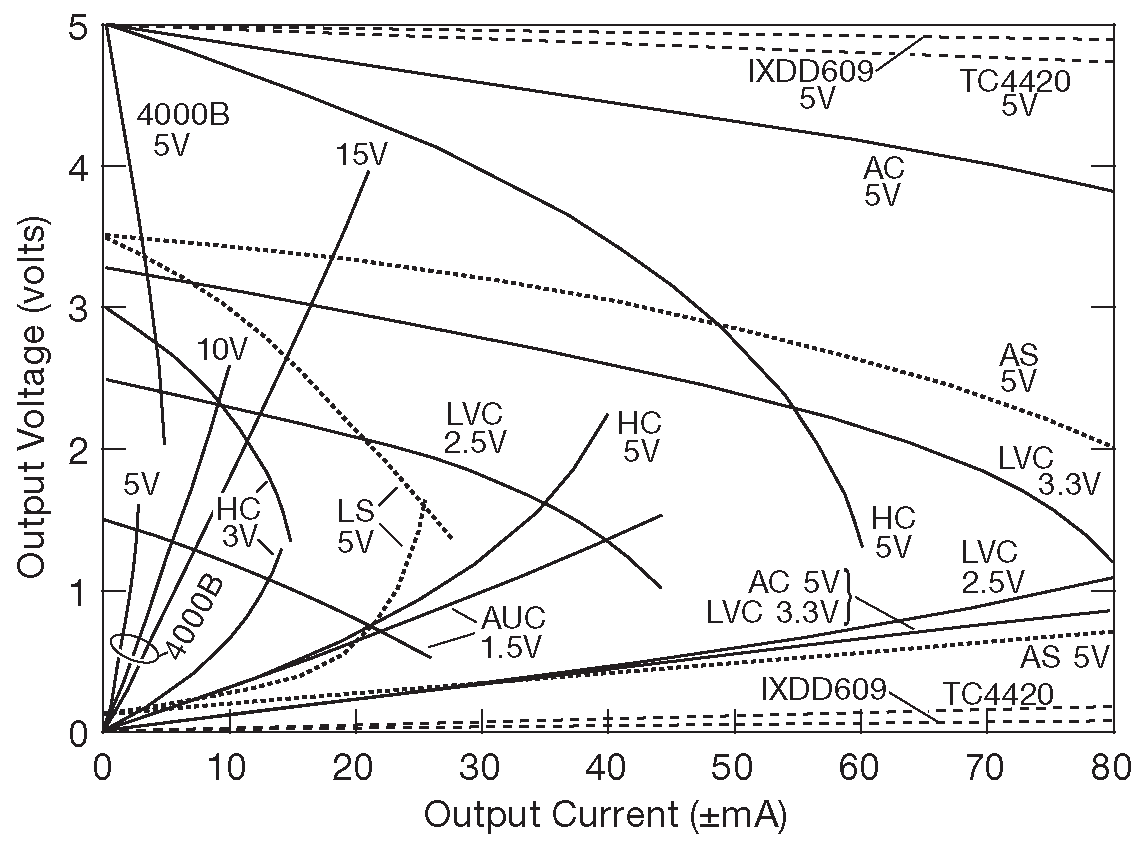

На рис. 12.7 изображены типовые графики нагрузочной способности выходов ( зависимость напряжения на выходе от тока нагрузки ) для ВЫСОКОГО и НИЗКОГО состояния для некоторых логических семейств. Для упрощения картины выходные токи считаются положительными. Отметим, что устройства, относящиеся к КМОП типу, т.е. с выходным каскадом на комплементарной паре из n-МОП и p-МОП транзисторных ключей, выдают наружу полный уровень питания - землю или \( V_+\) , исключая случай низкоомной нагрузки. Таким образом, если в качестве таковой выступают КМОП входы ( с нулевым входным током ) на выходе присутствует полный перепад от земли до \( V_+\) . Иначе выглядят биполярные ТТЛ уровни: +50...+200 mV НИЗКИЙ и +3.5 V или выше ВЫСОКИЙ, если выход нагружен на ТТЛ вход. Если на выходе ТТЛ повешен подтягивающий резистор ( о нём позже ), то ВЫСОКИЙ уровень доходит до +5V . На графике присутствуют выходные характеристики двух МОП драйверов с ТТЛ совместимыми входами. У них на выходе стоят мощные КМОП каскады, позволяющие подавать в нагрузку уровень земли или положительного питания Vdd . Его величину для TC4420 можно выбрать в диапазоне от 4.5 до 18 V , а для IXDD509 - от 4.5 до 30 V _6 .

Рис. 12.7 Нагрузочная способность выходов различных логических семейств. 74LS’ и 74AS’ - биполярные ТТЛ с питанием +5V , npn повторителем в верхнем плече и потому имеют ВЫСОКИЙ выходной уровень ∼3.5 V . Все остальные графики относятся к чистым КМОП микросхемам, имеющим полный размах питания на выходе. NC4420/MC1406 и IXDD609 – «МОП драйвера» с надёжными выходными каскадами, способными переключать токи 6 и 9A соответственно. 80 mA им трудно даже заметить

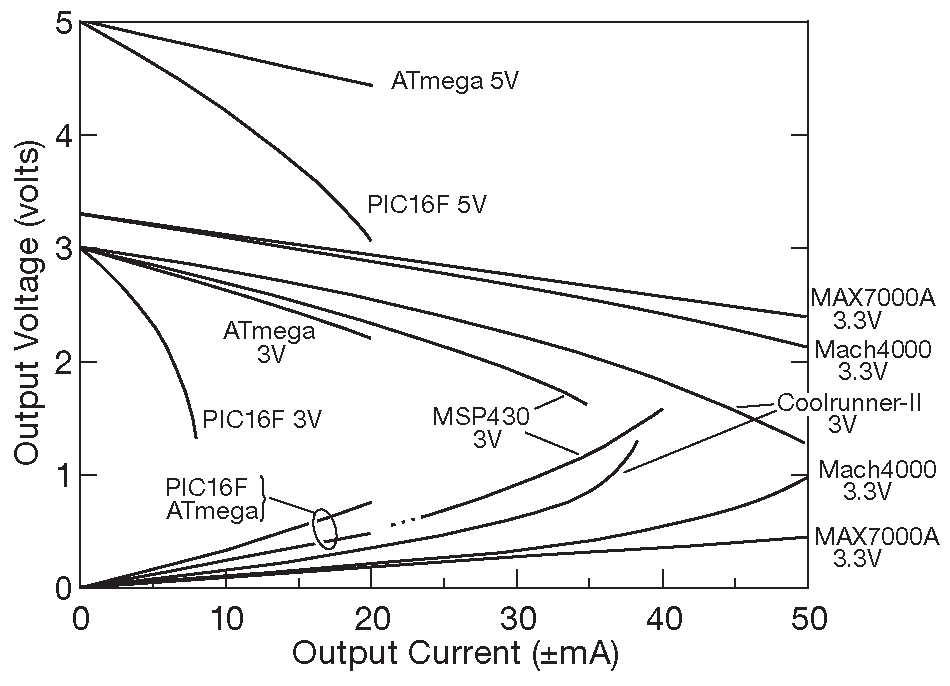

В современной цифровой электронике вовсю используются возможности программируемой логики ( Часть 11 ) и микроконтроллеров ( Часть 15 ), поэтому полезно знать какую нагрузочную способность имеют их выходы. На рис. 12.8 показаны выходные характеристики нескольких семейств программируемой логики ( Altera MAX7000 A [* RIP ] , Lattice Mach 4000, Xilinx Coolrunner-II ) и микроконтроллеров ( Atmel ATmega, Microchip PIC16F, TI MSP430 ). Все они имеют КМОП каскады с полным размахом питания на выходе. Как легко заметить по графикам, не все каскады созданы равными.

Рис. 12.8 Нагрузочная способность ИМС программируемой логики и микроконтроллеров

==798

12.1.3 Сопряжение различных цифровых семейств

Очень важно знать, как заставить различные цифровые микросхемы общаться друг с другом, потому что случаются ситуации, когда в одном устройстве приходится использовать разные семейства или подавать на часть логики иное напряжение питания. Совершенно обычна ситуация, при которой выходной сигнал микроконтроллера с питанием +2.5 V надо подать на 5-вольтовый инвертор, чтобы в итоге управлять контактами реле или зажигать белый светодиод. Существуют и противоположные задачи: переключить 5-вольтовым сигналом состояние 1.8-вольтовой ИМС.

Мешать данным задачам могут:

- несовместимые логические уровни,

- недостаточная нагрузочная способность и

- несовместимые уровни питания.

Чем забивать голову страницами правил и пояснений правильности или неправильности того или иного подхода, авторы подобрали рабочие варианты решения различных проблем и предлагают пройтись по списку.

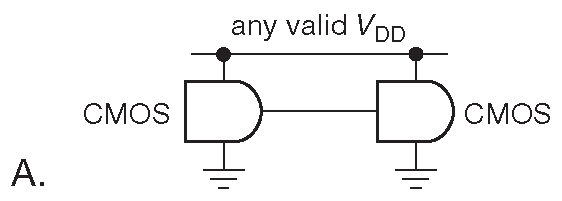

Вариант 12.9A

Рис. 12.9 (A) Сопряжение цифровых микросхем. Ведущий : КМОП логика, ведомый : КМОП логика с таким же напряжением питания

Два цифровых КМОП семейства, запитанные от одного источника, всегда можно соединять между собой. Выходной сигнал имеет полный размах и без каких-либо проблем может управлять входом, независимо от его напряжения переключения.

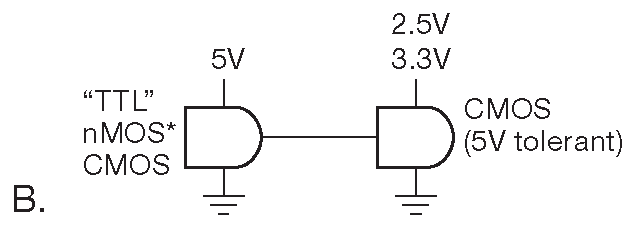

Вариант 12.9B

Рис. 12.9 (B) Сопряжение цифровых микросхем. Ведущий : 5-вольтовая логика, ведомый : низковольтовая КМОП логика

КМОП с питанием 5V может подключаться к «5V-совместимым» микросхемам, например 74LVC’, питающимся от более низкого напряжения. В данном случае и КМОП с полными +5V на выходе, и ИМС с «ТТЛ уровнями» на выходе ( сюда же попадают и биполярные ТТЛ, и микросхемы с n-МОП повторителем в верхнем плече ), имеющие ВЫСОКИЙ уровень порядка +3.5 V , удовлетворяют требованиям ко входному сигналу со стороны «5V-совместимых» КМОП, запитанных от +2.5 или от +3.3 V . Кроме того, есть 74LV1T вентиль, занимающийся преобразованием уровней, которые могут как «передавать вниз», как в данном случае, так и «передавать вверх» ( см. рис. 12.9C ).

==799

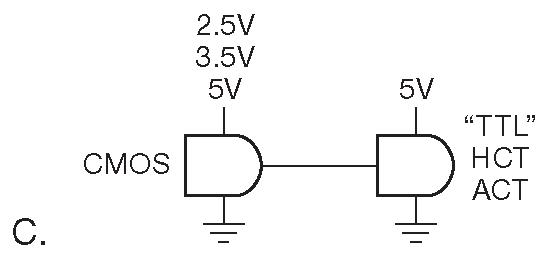

Вариант 12.9C

Рис. 12.9 (C) Сопряжение цифровых микросхем. Ведущий : низковольтовая КМОП логика, ведомый : 5-вольтовая логика

«ТТЛ входами» 5-вольтовой логики ( с пониженным уровнем напряжением переключения ) можно управлять непосредственно с КМОП выходов, чей диапазон переключения не меньше 2.5 V . В число совместимых ведомых попадают биполярные ТТЛ микросхемы, часть 5-вольтовых КМОП семейств ( 74HC’, 74AC’, 74AHC’, 74VHC’ ) и «ТТЛ-совместимые» ( 74HCT’, 74ACT’, 74AHCT’ _7 , 74VHCT’ ). Есть также специальная серия трансляторов логических уровней 74LV1T ( см. рис. 12.9G ).

==800

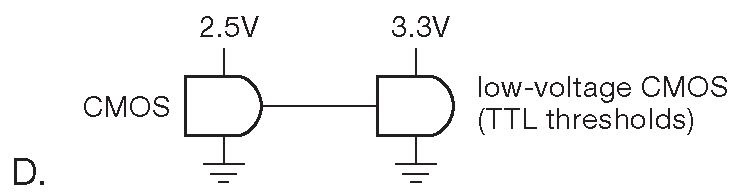

Вариант 12.9D

Рис. 12.9 (D) Сопряжение цифровых микросхем. Ведущий : КМОП логика 2.5 V , ведомый : КМОП логика 3.3 V

Практически все КМОП семейства, способные работать от 3.3 V , имеют ТТЛ совместимые входные уровни ( < 0.8 V воспринимается как НИЗКИЙ, > 2.0 V - как ВЫСОКИЙ ), поэтому подключать их к 2.5-вольтовому КМОП выходу с полным размахом совершенно безопасно.

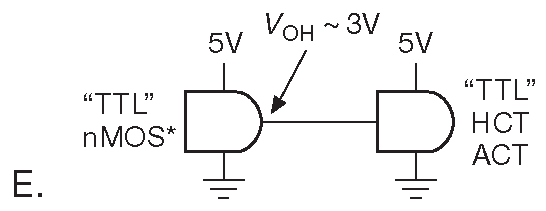

Вариант 12.9E

Рис. 12.9 (E) Сопряжение цифровых микросхем. Ведущий : 5V «ТТЛ выход», ведомый : 5-вольтовая логика с пониженным уровнем переключения

5-вольтовая логика с ТТЛ совместимым выходом имеет НИЗКИЙ уровень, близкий к 0V , а ВЫСОКИЙ - не выше ∼3.5 V ( причём гарантируются, что он будет выше 2.4 V и только ). Её можно подключать только к «ТТЛ-совместимым» входам, в число которых попадают биполярные ТТЛ или 5-вольтовые микросхемы с «ТТЛ-совместимыми» входами ( 74ACT’, 74HCT’, 74AHCT’, 74VHCT’, некоторые микроконтроллеры и cPLD ).

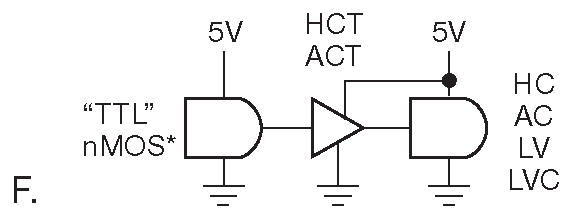

Вариант 12.9F

Рис. 12.9 (F) Сопряжение цифровых микросхем. Ведущий : «ТТЛ выход», ведомый : несовместимая 5V логика

Если в схеме нужен сигнал с КМОП уровнем переключения ( т.е. \( V_+\)/2 или ∼2.5 V ), можно взять КМОП вентиль с «ТТЛ-совместимыми» входами ( 74HCT’ и т.п. ), чтобы привести ТТЛ уровни к 5-вольтовому КМОП. Здесь можно использовать специальные трансляторы уровней, например, 74LVC1T45 ( см. рис. 12.9G ).

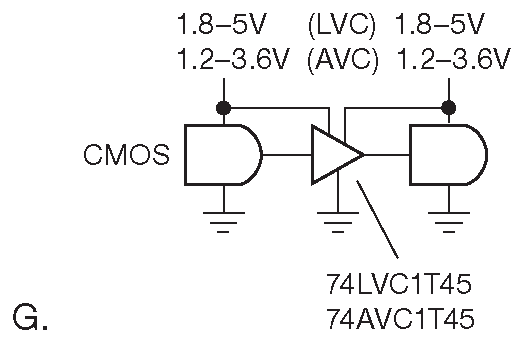

Вариант 12.9G

Рис. 12.9 (G) Сопряжение цифровых микросхем. Трансляторы уровней с двойным питанием от 1.8 до 5V и от 1.2 до 3.6 V

Существуют специальные микросхемы, созданные для передачи сигналов между системами с разными уровнями питания. Так, 74LVC1T45 с двойным питанием позволяет объединять семейства с питанием от 1.8 до 5V на любой из сторон. Это по факту двунаправленный буфер, управляемый выводом «DIR», подобно классическому октальному ’245. Ещё более низковольтная 74AVC1T45 работает от 1.2 до 3.6 V на любой из сторон. Эти микросхемы выпускают и в сдвоенном исполнении ( ’LVC2T45, ’AVC2T45 ). Но, стоит отметить, что LVC’ серия имеет порог переключения на середине питания, и, если она включена на 5V на входной стороне, то с учётом гарантированных уровней НИЗКИЙ < 1.5 V , ВЫСОКИЙ > 3.5 V , не может подключаться к ТТЛ выходу напрямую, т.к. последний гарантирует только уровень ≥ 2.4 V . Здесь подойдёт TXB0101 ( см. рис. 12.9K ).

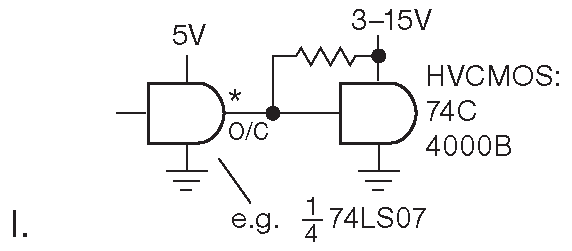

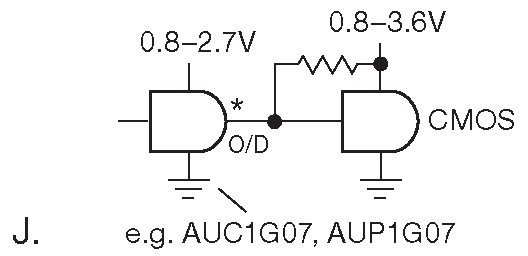

Вариант 12.9HIJ

Рис. 12.9 (H) (I) (J) Сопряжение цифровых микросхем. Ведущий : выход с открытым коллектором или стоком

Если есть буфер с открытым коллектором ( стоком ), можно передавать сигналы вверх или вниз по напряжению. Оплата универсальности скоростью распространения и током покоя через подтягивающий резистор. Величина резистора есть результат компромисса: меньший номинал увеличивает скорость, но и потребление. Рис. 12.9H показывает передачу сигналов при питании от 1.8 до 5V с любой из сторон. Требуется буфер ’07 из семейства с широким диапазоном питания, поддерживающим работу с сигналами 5V на входе и выходе ( 7SZ’, 74LVC’, 74VHC’ ). Если нужен больший диапазон на выходе, можно взять 74LS07 ( рис. 12.9i , который позволяет вешать подтяжку на +15 V . [* А 7407, она же 155ЛН3, и вовсе до +30 V ] . Если нужно передавать очень низковольтный сигнал, можно использовать 74AUC1G07 или 74AUP1G07 ( рис. 12.9J ), которые работоспособны вплоть до уровней 0.8 V .

[* Гляньте ещё схему генератора для наручных часов на стр. 448 ( §7.1.6.D ) ].

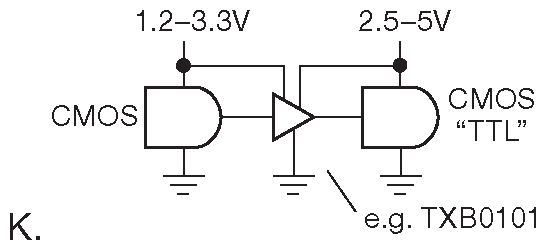

Вариант 12.9K

Рис. 12.9 (K) Сопряжение цифровых микросхем. Ведущий : низковольтная КМОП логика, ведомый : логика от 2.5 до 5V

Кроме трансляторов уровня с двумя питаниями из обычных серий, типа LVC/AVC1T45 ( рис. 12.9G ), есть ещё TXB0101. Но у этой микросхемы целая куча особенностей. Во-первых, «правостороннее» питание VDDB не может быть ниже «левостороннего» VDDA . Во-вторых, буфер двунаправленный, но, в отличие от ’1T45, не имеет вывода «DIR». Вместо прямого управления микросхема отслеживает изменение уровня на обеих сторонах и соответственно меняет состояние противоположного порта. Делается это за счёт кратковременного переключения состояния КМОП драйвера и последующего удержания получившегося уровня слабой положительной обратной связью ( ∼4 kΩ резистор между входом и выходом ). Такое поведение удобно для антидребезговых схем ( рис. 12.16 ).

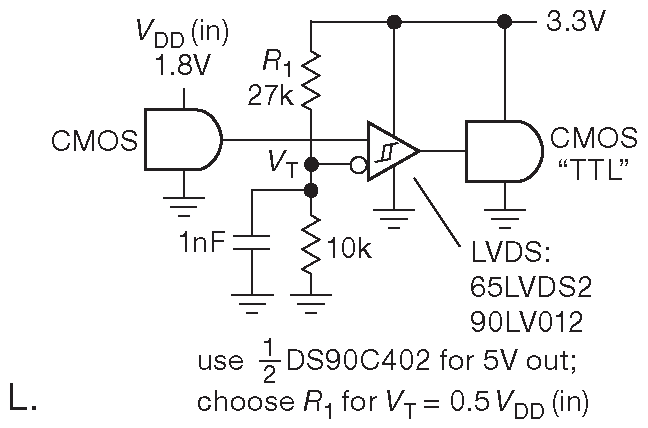

Вариант 12.9L

Рис. 12.9 (L) Сопряжение цифровых микросхем. Ведущий : низковольтовая КМОП, ведомый : 3.3 или 5V логика

Есть красивый трюк. LVDS приёмники принимают дифференциальные сигналы с синфазным уровнем до +2.4 V и гарантируют переключение при разнице между уровнями дифференциальных входов уже 0.2 V . Выходной каскад таких ИМС является стандартным КМОП и имеет отдельное питание от 2.5 до 3.3 V ( 65LVDS2 ) или до 5V ( DS90C402, DS90C032 ). Такой приёмник можно включить в качестве преобразователя уровней, подав опорный «уровень переключения» для нужного логического сигнального диапазона на один дифференциальный вход ( здесь будет уместен небольшой фильтрующий конденсатор ), а входной сигнал на другой. Схема будет работать вплоть до уровней 0.5 V , где не помогут никакие иные варианты. [* Отметим также, что дифференциальность приёмника позволяет выбрать при передаче сигнала любую полярность: достаточно подать опорный уровень на другой вход, и - Опа! ] Такие микросхемы переключаются быстро , часто специфицируются для потоков данных, превышающих 400 Mbps , и имеют задержку распространения < 2 ns .

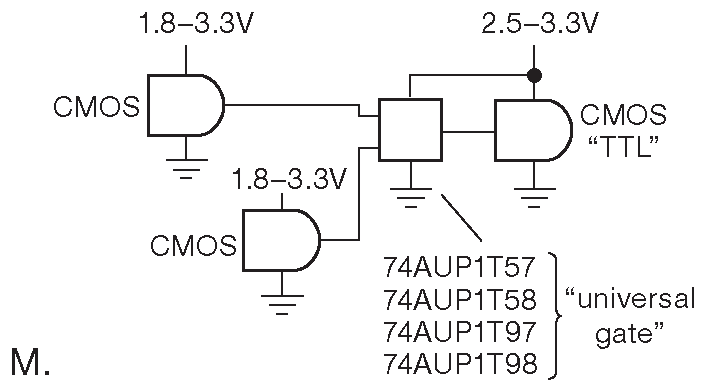

Вариант 12.9M

Рис. 12.9 (M) Сопряжение цифровых микросхем. Ведущий : низковольтный КМОП универсальный логический элемент

Удобные «универсальные» вентили, рассматривавшиеся в Части 10 ( §10.2.1.A ) можно использовать для выполнения логических задач с одновременной трансляцией уровней между группами микросхем с разным питанием. При использовании таким манером на вентиль заводится питание для выходной группы ( диапазон от 2.5 до 3.3 V ), при этом на входе могут присутствовать сигналы с уровнями от 1.8 до 3.3 V . У таких элементов на входах стоят триггеры Шмитта с гистерезисом порядка 0.4 V с уровнем переключения порядка 0.7 V .

==801

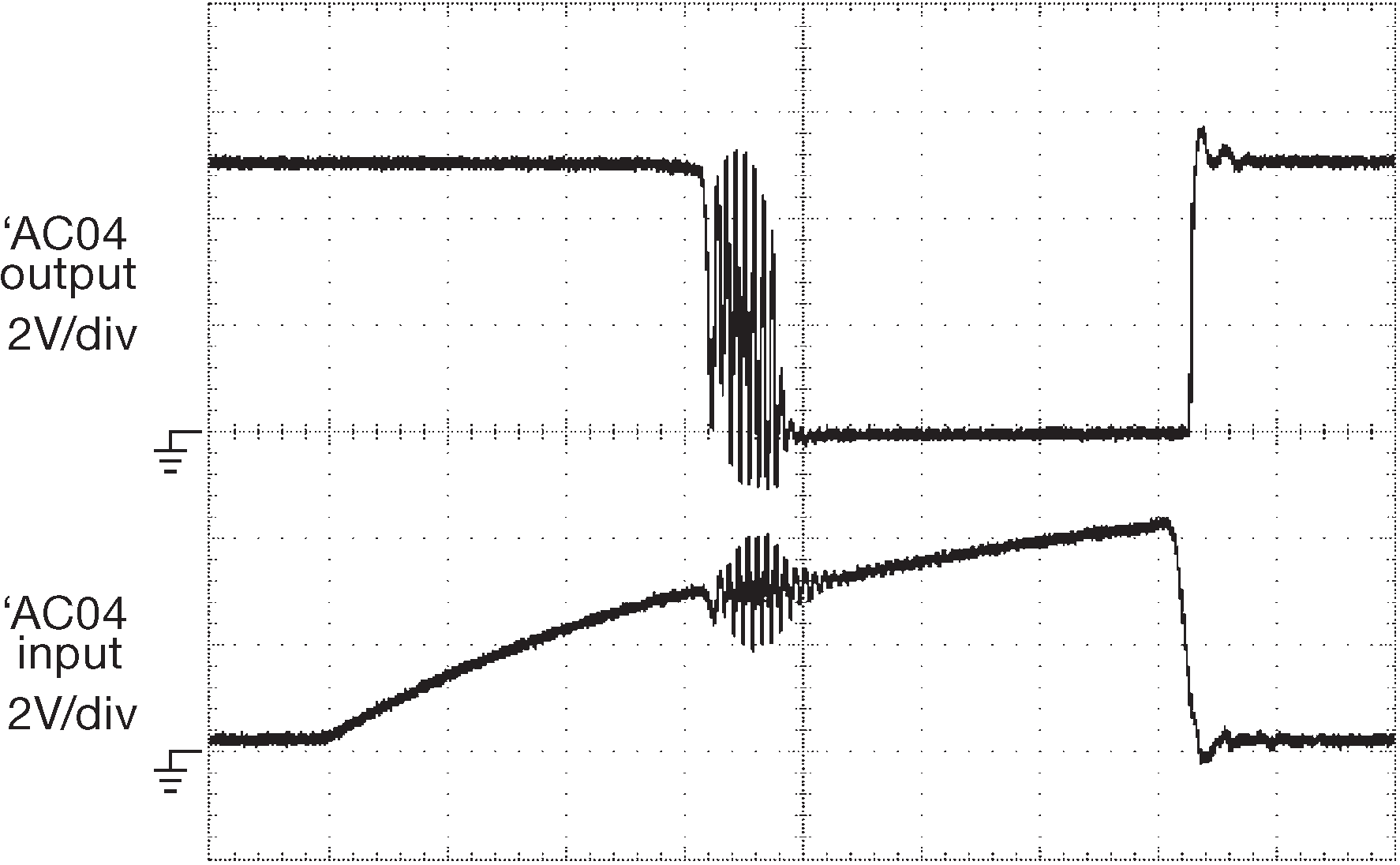

12.1.3.A Динамическая несовместимость: медленные фронты

Если подавать на вход быстрой логической схемы сигнал, пересекающий порог переключения недостаточно быстро, в схеме могут возникать разные необычные глюки. Резкое переключение сигнала на выходе может передаваться обратно на вход ( через шины питания, внутренние цепи или через внешнюю емкостную связь ), вызывая множественные переключения ( см. рис. 12.10 ). Чтобы показать это неприятное явление была составлена заведомо некорректная пара: взят элемент 74LS05 - инвертор с открытым коллектором со слабой подтяжкой 5 kΩ на +5V , который запускал нервный инвертор 74AC04 _8 . На фоне неспешного входного сигнала хорошо видно, как быстрый инвертор бешено щёлкает своим выходом.

Рис. 12.10 Относительно медленный восходящий «фронт» с открытого коллектора ’LS05 с вялой подтяжкой 5 kΩ ( нижний луч ) приходит на быстрый инвертор ’AC04, который начинает беспорядочно переключаться, образуя множественные переходы уровня. На заднем фронте проблем нет, потому что нисходящий фронт в открытом коллекторе быстрый [* и, добавим, формируется насыщающимся транзистором, читай, низкоомной нагрузкой, которая «глотает» наводки. См. также рис. 7.3 и §7.1.2.B ] . По горизонтали 40 ns/div

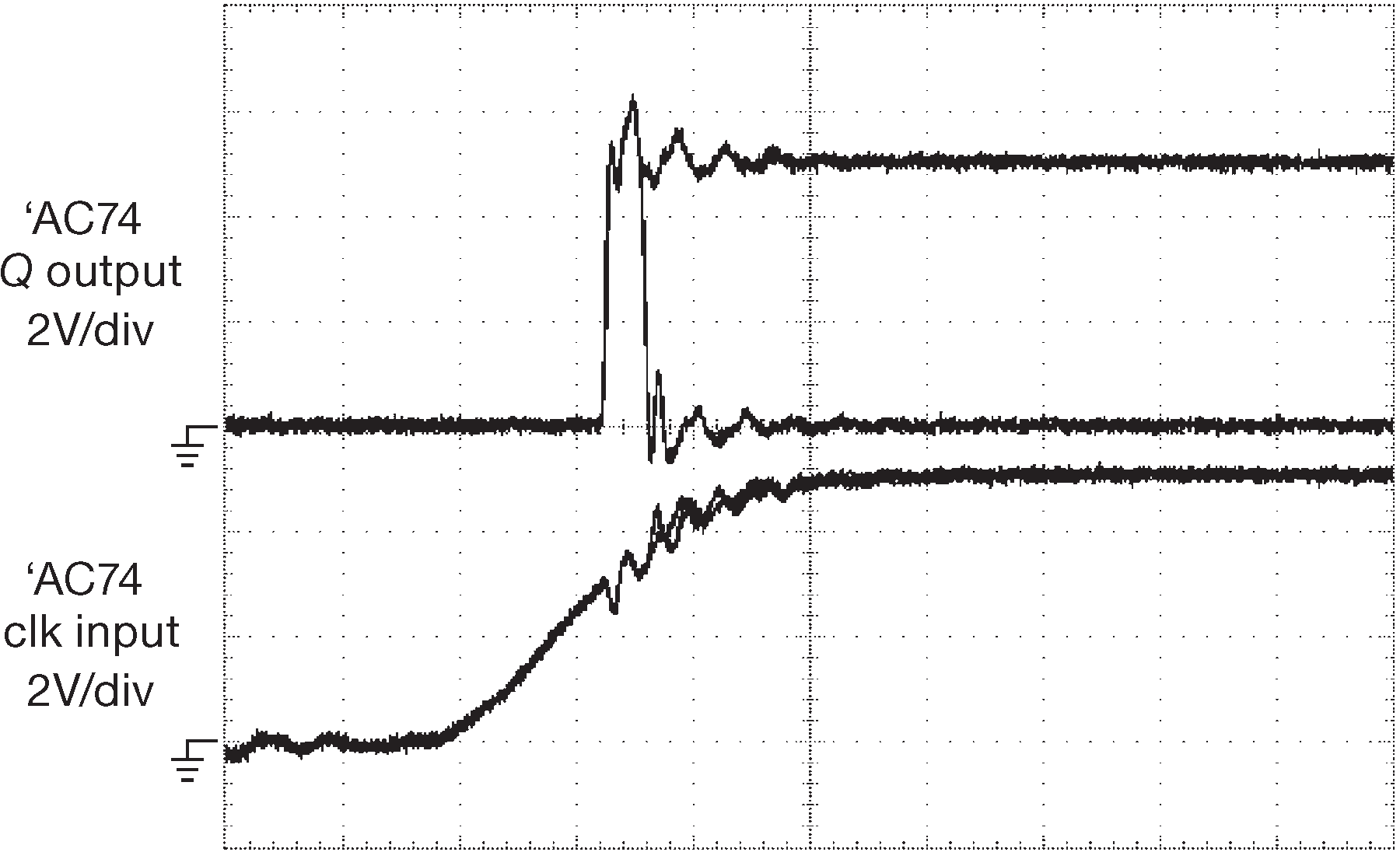

Множественные переключения - штука достаточно неприятная, но медленный фронт превращается в совершенный кошмар, когда нужно подавать сигнал на вход, срабатывающий по фронту ( например, тактовый вход триггера или счётчика ). Триггер может вовсе отказаться перещёлкиваться, а счётчик наоборот будет срабатывать несколько раз на одном фронте. Для иллюстрации эффекта на тактовый вход 74AC74 был подан прямоугольный сигнал с вентиля «ИЛИ-НЕ» CD4001B. Обе микросхемы питались от +5V . Перед приходом каждого такта на сброс триггера подавался активный импульс. Результат показан на рис. 12.11 . Иногда триггер срабатывал нормально, а иногда переключался дважды с очень короткой задержкой.

Рис. 12.11 Медленный фронт с выхода CD4001B, нагруженный на 27 pF ( типовая цифра для ёмкости нагрузки вместе с соединением ) подаётся на тактовый вход быстрого триггера ’AC74. Осциллограф показывает постоянное, хотя и нерегулярное, появление нескольких переключений на одном фронте. По горизонтали 20 ns/div

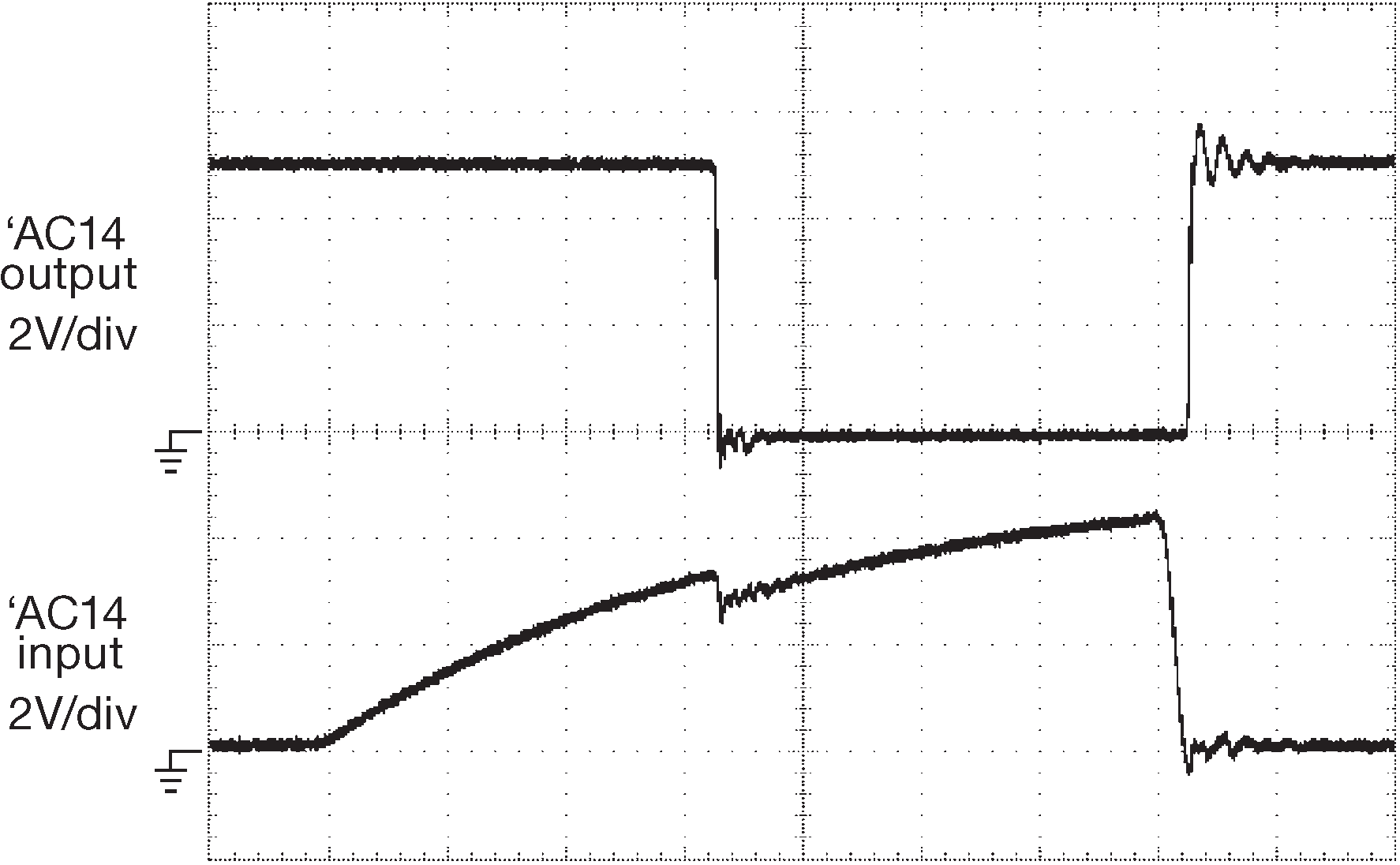

Вывод очевиден: не используйте медленные фронты для запуска быстрой логики. Часто бывает достаточно обострить сигнал триггером Шмитта ’14, который есть во всех логических семейства. Рис. 12.12 показывает сигнал в той же схеме, что и на рис. 12.10 , но обычный инвертор 74AC04 поменян на триггер Шмитта 74AC14. Лучше всего, конечно, избегать работы с медленными фронтами.

Рис. 12.12 Схема как на рис. 12.10 , но инвертор ’AC04 заменён триггером Шмитта ’AC14. Видно, что быстрое переключение выхода возвращается на вход триггера Шмитта, как и ранее, но для перескока через гистерезис логического порога этого уже недостаточно, и помехе не удаётся запустить серию множественных переключений. По горизонтали 40 ns/div

Те же проблемы возникают при передаче цифровых сигналов между печатными платами, в межприборных и кабельных соединениях. Эта важная тема разбирается в §12.9 .

==801

1 Чтобы понять, как это происходит, рассмотрим эффект от линейного сокращения геометрических размеров МОП транзистора с длиной канала L и шириной W в k раз при условии неизменности электрического поля в нём ( т.н. «масштабирование с неизменной напряжённостью поля» ). Если L\(∝\)k и W\(∝\)k , то для неизменности напряжённости поля требуется, чтобы и \( V_{DD}∝\)k . Это ведёт к сокращению толщины оксидной изоляции затвора \( t_{ox}∝\)k . Значит, меняется ёмкость затвора, которая пропорциональна (L×W)/\(t_{ox}\) по закону \( C_G∝\)k . Следствием изменения геометрии будет снижение тока насыщения стока \(I_D∝\)k . С изменением тока стока сигнал на затворе будет меняться с 0V до Vdd за время \(τ≈ ( C_G·V_{DD})/I_D\) , которое также масштабируется \(τ∝\)k . Т.е. быстродействие логического элемента увеличивается пропорционально k , а потребляемая мощность ( \( V_{DD}×I_D\) ) снижается \( P∝\)k² . Но тогда удельная мощность в пересчёте «на мегагерц» снижается уже как k³ . Это объясняет неизменное стремление полупроводниковой промышленности поскорее перейти к следующему технологическому поколению ( за коэффициент сокращения между поколениями принята величина 1/\(\sqrt2\) . <-

2 Для КМОП логики, имеющей нулевой входной ток, чрезмерная нагрузка просто замедляет переключение [* за счёт увеличения ёмкости нагрузки ] , т.е. нагрузочную способность в некотором смысле можно считать «бесконечной». С биполярной логикой такой номер не пройдёт: входной ток ( 1.6 mA для 74LS’ ) жёстко ограничивает максимальную нагрузочную способность на уровне 10 входов. <-

3 Следует особо подчеркнуть отличие биполярных ТТЛ схем. Их вход является источником заметного тока ( от 0.1 до 1 mA ) для НИЗКОГО уровня, а для ВЫСОКОГО - потребителем незначительного тока, никогда не превышающего 20 μA . Чтобы завести ТТЛ вход, необходимо забирать из него миллиампер, другой при уровне не выше 0.4 V . Недопонимание в этом вопросе приведёт к созданию неработающей схемы. <-

4 Авторы проверили пороговое напряжение для некоторых инверторов с «ТТЛ порогом», для чего подали выход обратно на вход. Вот результаты для элемента ’04: 7404 1.37V ; 74ACT04 1.48 V ; 74AS1004 1.49V ; 74F04 1.43V ; 74HCT04 1.34V и 74LS04 1.50 V . <-

5 Будьте бдительны, используя старые КМОП микросхемы ( в основном микроконтроллеры и PLD, рассчитанные на питание +5V ). В них вместо p-канального МОП ключа в верхнем плече стоит n-канальный истоковый повторитель. Для таких микросхем выходной ВЫСОКИЙ уровень не дотягивается до уровня положительного питания, зависая в районе +3V . Такие микросхемы можно узнать по цифрам в разделе «Параметры на постоянном токе» справочных данных. Там написано что-либо подобное «\( V_{OH}(min)=2.4 V\)». Это характерный признак старого «ТТЛ совместимого» выхода ( у ТТЛ верхняя подтяжка сделана на npn повторителе ). <-

6 Здесь надо заметить, что мощные МОП драйвера не могут работать с максимальной рабочей частотой цифровой логики. Их временнЫе характеристики нормируются при больших емкостях нагрузки, свойственных мощным МОП транзисторам и составляют 10...25 ns и более ( сравните со временем распространения для 74LVC’ \( t_{pd}\) ≈ 2 ns ) . <-

7 Скажем, 74AHCT1G125 очень удобна для передачи сигналов между 3.3-вольтовой логикой и устройствами, требующими полных 5V размаха. Вентиль упаковывается в стандартные корпуса SOT23-5 и SC70-5 и стоит менее $0.10. <-

8 74AC’ и 74ACT’ очень беспокойная и «нечёткая» логика, особенно когда упакована в корпус DIP с угловым расположением выводов питания. Держитесь подальше от этих микросхем. Если это невозможно, используйте отдельный слой земли, короткие отводы питания и ставьте развязывающие конденсаторы как можно ближе к корпусу. <-