10.8 Патологии логических схем

==755

Существуют интересных и часто неожиданные ловушки, поджидающие начинающего проектировщика цифровых схем. Некоторые из них, такие как логические гонки или зависание, не зависят от используемого логического семейства. Другие ( «тиристорное защёлкивание» у КМОП ) являются родовыми аномалиями конкретного семейства или технологии. Ниже приводится небольшая коллекция проблем, набранная при практической разработке, в надежде, что это собрание личных анекдотов поможет кому-то избежать проблем.

10.8.1 Проблемы на постоянном токе

10.8.1.A Зависание

Очень легко попасть в ловушку, создав схему, имеющую состояние, не связанное с нормальной последовательностью действий. Допустим, есть некая схема с несколькими триггерами, которые переключаются между набором состояний. И в один прекрасный день она намертво зависает, заставляя выключить и вновь включить питание. Проблемы вызваны «зависанием» - попаданием в состояние из которого нет выхода. Оказаться там можно, например, из-за помехи по питанию. Очень важно находить такие состояния на этапе проектирования [* n триггеров имеют до 2n различных состояний ] и строить связи таким образом, чтобы схема могла восстанавливаться автоматически. Или как минимум организовывать в устройстве сигнал сброса, который будет формироваться автоматически при запуске или вручную и приводить систему в правильное состояние. Иногда такая модификация делается даже без дополнительных компонентов, см. упражнение 10.23 .

10.8.1.B Начальная инициализация

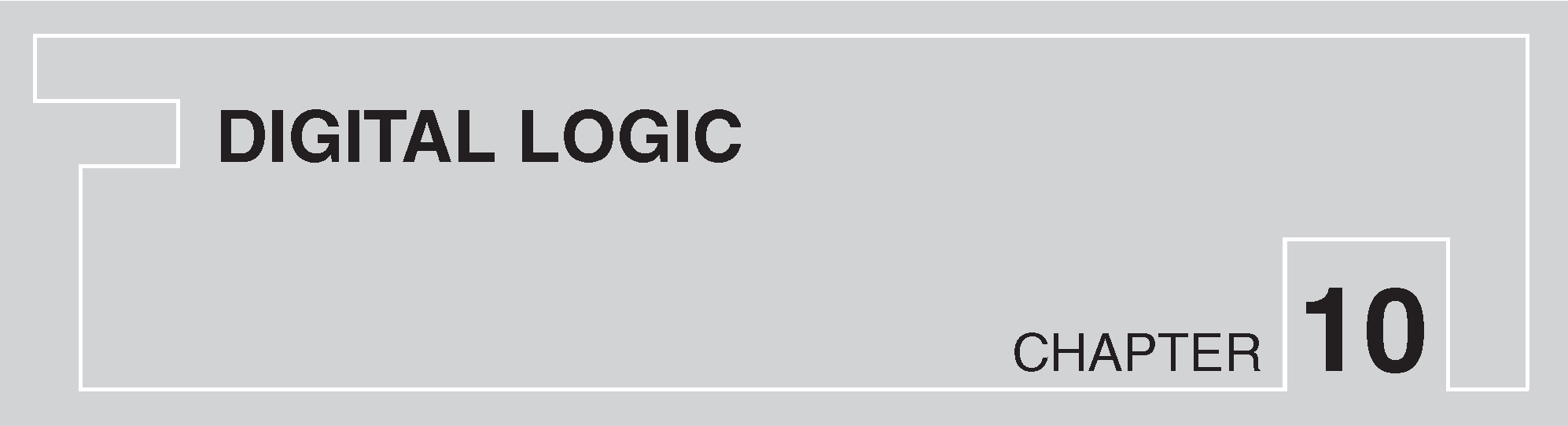

Близко к первой проблеме примыкает вопрос состояния системы при запуске. Наличие какого-то сигнала, приводящего систему в исходное состояние - полезная штука. В его отсутствие устройство может вести себя странно в первый момент после включения [* это может случиться даже с аналоговыми схемами, см. §9.10.1.A ] . Одним из решений может быть задержка на RC цепочке с триггером Шмитта ( рис. 10.94 ). К сожалению, эта схема требует дополнительных компонентов и не реагирует на кратковременную просадку питания.

Рис. 10.94 Схема сброса при включении питания

Более правильный путь - использовать супервизор питания. Выпускаются они в самых разных вариантах. Самые простые - 3-выводные модели выдают импульс при включении. К таким ИМС относится MC34164, которая, помимо поверхностных корпусов, выпускается в транзисторном TO-92. MC34164 держит открытый коллектор на выходе в НИЗКОМ состоянии, покуда напряжение питания не превысит 4.3 V ( или 2.7 V для MC34164-3 ). Имеется внутренний источник опорного напряжения и гистерезис. Больше возможностей предлагает серия MAX700 фирмы MAXIM. Она упаковывается в 8-ногий корпус и имеет комплементарные выводы сброса с активными подтяжками. Внешним резистором можно выбрать пороговый уровень из диапазона от 1.2 до 4.7 V . Также подкручивается гистерезис. Есть вход ручного сброса ( рис. 10.95 ). ИМС MAX823 ( или ADM823 ) имеют в дополнение к сбросу сторожевой таймер . Его требуется регулярно перезапускать, в противном случае он выдаст сигнал сброса. Это удобный способ обнаружения программных сбоев и возврата системы в исходное состояние. В современных микроконтроллерах сторожевой таймер добавляют в набор периферии на кристалл.

Рис. 10.95 Микросхема супервизора питания выдаёт импульс сброса при включении, перебоях с питанием и при нажатии на кнопку. Дополнительные выводы ( пунктирные соединения ) позволяют подправить гистерезис и порог переключения

==756

Многие из этих микросхем выпускаются несколькими производителями и различаются только названиями. Например, MAX809 может иметь префикс APX, ADM, CAT, LM, STM и TCM, а благодаря такой конкуренции стоит почти ничего. Только не забудьте заглянуть в справочные данные перед заменой. Скажем, MCP809 имеет иную разводку, которая совпадает с STM1001. Ошибка в документации? Возможно. Но в любом случае, вы предупреждены.

Продвинутые модели вроде ADM690 позволяют переключать питание на резервную батарею, имеют дополнительный компаратор и логику управления. См. табл. 10.6 с параметрами самых популярных супервизоров.

10.8.2 Проблемы при переключении

10.8.2.A Логические гонки

Здесь таится масса тонких ловушек. Классические логические гонки показаны в схеме синхронизатора импульсов в §10.4.4 . Основное правило: разрешая логический вентиль сигналом с триггера ( или любого иного тактируемого устройства ) надо проверять схему на ситуацию разрешения с мгновенным последующим запрещением через время распространения сигнала в вентиле. Аналогично, убедитесь, что сигнал на входе данных триггера не подгоняется по задержке относительно тактового сигнала ( ещё один плюс синхронных схем ). В общем случае задерживайте тактовый сигнал относительно данных. [* Данные уже должны «устаканиться» к приходу фронта. см. §10.8.2.B ] .

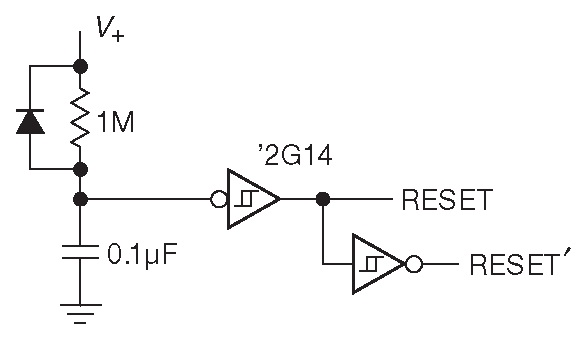

Проглядеть условия для логических гонок очень легко. Классический пример - простой 2-входовой мультиплексор. Если использовать обычную логику Y = S & A | ~ S & B , как на рис. 10.96A , появляется потенциальная проблема. Неприятности возникают, когда на обоих входах «A» и «B» ВЫСОКИЕ уровни, а переключение «S» идёт от ВЫСОКОГО к НИЗКОМУ, т.е. переход идёт от «A» к «B». Задержка в инверторе приводит к запрету нижнего «И» раньше разрешения верхнего, что вызывает кратковременную иголку НИЗКОГО уровня на выходе. Проблема разрешается дополнительным условием A & B ( рис. 10.96B ). Коммерческие ИМС делаются по схеме 10.96B , поэтому опасность возникает только с программируемой логикой 85 , для которой описание на HDL задаёт пользователь. Придётся прямо указать, что проводить «оптимизацию» избыточного терма запрещено. Тем самым вы покажете глупой железке, что не лыком шиты и тоже читаете умные книжки.

Рис. 10.96 Введение избыточной логики избавляет от иголок из-за логических гонок в 2-входовом мультиплексоре

10.8.2.B Метастабильные состояния

В §10.4.2.D объяснялось, что триггер и вообще любое тактируемое устройство легко сконфузить, если изменить состояние входа данных в течение времени предустановки перед приходом активного фронта. До тех пор, пока триггер может сделать какой-нибудь выбор, всё хорошо. Но смена состояния может случиться в плохой момент - прямо в точке принятия решения, и тогда триггер задумается над ситуацией надолго. Его выход может колебаться возле порогового уровня во много раз дольше обычной задержки распространения ( или выдать какой-либо уровень и передумать позднее, см. рис. 10.60 ).

Проблема не возникает в хорошо спроектированных синхронных схемах, в которых удовлетворены все требования по времени предустановки. Для этого надо брать достаточно быструю логику, чтобы входы триггеров были стабильны за \(t_S\) до очередного фронта. Но в таких схемах возникают проблемы синхронизации при передаче сигналов из другой схемы с иным тактированием. В этом случае нельзя гарантировать, что вход не изменится в течение времени удержания. Можно даже подсчитать, как часто это будет происходить 86 . Проблемы метастабильности могут быть причиной странных компьютерных сбоев, но это не точно. Лекарством служит цепочка последовательных синхронизаторов. Иногда можно встретить заявки на «устойчивость к метастабильности», см., например, 5-вольтовую серию «AC(T)».

Table 10.6 Selected Reset/Supervisors Type Pins Package(s) 03 CO Cl) TO 03 -t—¦ ? * TO O ¦o -C o 5 z cd w cd DC o -C TO X cd > -t—> < Supply current (MA) MC34164 3 TO-92, SO-8 2 - - - 12 MAX809 3 SOT-23 7 - - ’810 15 NCP303 5 SOT-23 7 - - ’302 0.5 MAX700 8 SOIC-8 ib - • both 100 ADM811 4 SOT-143 6 - • ’812 5 ADM823 5 SOT-23, SC-70 7 • • ’824 10 Notes: (a) Voltage is specified by a suffix. (b) External adjustment. (c) All have active-LOW output; part numbers listed have active-HIGH output instead; MAX700 has both.

==757

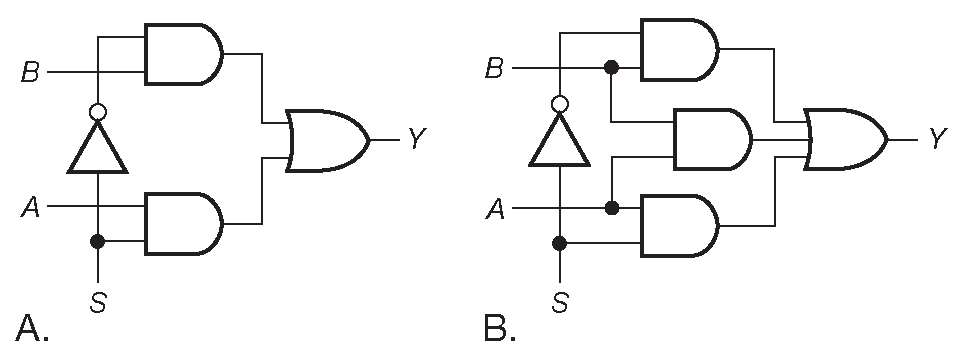

10.8.2.C Фазовый сдвиг фронта

Фазовый сдвиг фронта возникает, когда имеется тактовый сигнал с пологими фронтами, который подаётся на несколько микросхем, сидящих на одной протяжённой тактовой линии ( рис. 10.97 ). В данном случае это 16-битовый регистр, собранный из 8-разрядных сдвиговых регистров ’595. На тактовый вход подаётся сигнал с пологими фронтами. Плавный фронт вызван емкостной нагрузкой на слабом выходе тактового сигнала ( это может быть вывод микроконтроллера ). Проблема в том, что у первого регистра порог переключения может быть ниже, чем у второго ( такая разница имеется всегда и обусловлена допусками при производстве ). Низкий порог приведёт к более раннему сдвигу данных в первом регистре. При этом может быть потерян выходной бит первого регистра. КМОП схемы имеют достаточно большой разброс порогового уровня, что только усложняет ситуацию ( спецификация говорит о разбросе от одной третьей до двух третьих напряжения питания, и она точно отражает действительное положение ). Исправить ситуацию можно, раздавая тактовый сигнал близкорасположенным быстрым буфером с минимальной ёмкостью на выходе. ( Ещё один способ борьбы со сдвигом фазы фронта - добавление задержки на линию данных, связывающую последовательные регистры в цепочке. [* Волнистые проводники на печатных платах видели? Это оно ] . Но такой приём не снимает требования к наличию качественного тактирования ).

Рис. 10.97 Пологий активный фронт может вызвать фазовый сдвиг тактового фронта в микросхемах с отличающимся порогом переключения

В общем случае, любому тактовому входу, срабатывающему по фронту, требуется оказывать должное внимание. Зашумлённые, звенящие тактовые линии обязательно надо чистить буферным элементом, возможно, с гистерезисом на входе, перед подачей на синхронную периферию. Но здесь надо следить за выполнением требований по времени установки/удержания. Очень вероятны проблемы с тактовыми сигналами, приходящими с другой печатной платы или от иного логического семейства. Например, медленная логика «4000B» или «74C» на входе быстрой «HC» или даже «AC», скорее всего, создаст проблемы со сдвигом фронта и неоднократными срабатываниями [* см. §12.1.3.A ] . То же можно сказать о паре «HC» + «LVC» и т.д.

Проблемы со сдвигом фронтов могут возникнуть ( сюрприз! ) даже внутри программируемой логической микросхемы. Скажем, в отличной серии cPLD 9500 отдельные триггеры могут тактироваться или одним из глобальных тактовых сигналов , или от внутренних логических элементов ( такой вариант называется «product terms» ). Но тактовый сигнал от логики, поданный, например, на сдвиговый регистр, может вызвать неправильную работу схемы. Проблема возникает из-за задержек, набегающих при прохождении через несколько триггеров. Работа синхронных схем гарантируется только при тактировании от глобальных линий 87 . Эта ловушка не всегда прямо обозначается в справочных данных.

[* Глобальные линии идут через весь кристалл по выделенным каналам, имеющим специальные средства для выравнивания задержек, причём времена таких задержек указываются в справочных данных. Логические сигналы идут другими путями, задержка в которых зависит от сложности логических термов. Этот вопрос всегда стоит на одном из первых мест в разделе «Типичные ошибки» любого учебника по программируемой логике ].

10.8.2.D Укороченные импульсы

В счётчике «по-модулю-n» из §10.6.1 использовались ИМС с синхронной загрузкой ( ’163 ), а не с управлением прямого действия ( как в ’191 ), потому что последним может потребоваться дополнительная задержка, чтобы на выходе не появился укороченный импульс ( т.к. счётчик сбрасывает сам себя ). Те же проблемы есть и у сдвиговых регистров. Укороченные импульсы превратят вашу жизнь в кошмар, вызывая ложные срабатывания или случайный сбои. Здесь при разработке надо использовать данные по задержкам для наихудшего случая.

10.8.2.E Неписанные правила

Полупроводниковая промышленность нащупывала свой путь медленно и постепенно. Начав с RTL в 1960-х, улучшив её до ТТЛ и Шоттки, она перешла, наконец, к современным КМОП сериям ( с краткой хронологией можно познакомиться в §12.1.1 ). Именно отсюда растут ноги в нелогичности разводки корпусов, в отсутствии спецификаций и у различия в функционировании. Пример: вентили в 7400 ( «И-НЕ» ) направлены выходом к выводу земли, а 7401 ( «ИЛИ-НЕ» с открытым коллектором ) к выводу питания. Это порождало столь серьёзные проблемы, что привело к появлению элемента 7403, функционально идентичного 7401, но с разводкой 7400. Такая же проблема возникала с 7490 ( BCD счётчик пульсаций ) с выводами питания по центру корпуса, а не по его противоположным углам. Примечательно, что центральное расположение выводов питания вновь появилось в скоростных КМОП сериях, причиной чему служила меньшая индуктивность такой разводки.

==758

Важным наследием этой анархии в годы становления является «свод» неписанных правил, которым, тем не менее, надо следовать. Например, D-триггер ’74 есть в любой серии. Если не его входы «S» и «R» одновременно подать активные уровни, то оба выхода «Q» и «/Q» перейдут в ВЫСОКОЕ состояние во всех семействах, кроме «74C», где оба выхода будут НИЗКИМИ. Этот факт не относится прямо к упомянутым неписанным правилам, т.к., если внимательно читать справочные данные, можно найти соответствующее описание. Техническое название для этого явления «особенность поведения». Ещё одна любимая авторами особенность у ’96 - 5-битного сдвигового регистра. В наборе входов управления есть вход установки, но нет сброса!

Настоящим неписанным правилом является очень важное время снятия сигналов. Это время между освобождением входов прямого действия и приходом следующего активного фронта, которое гарантированно позволит корректное переключение. Это время вообще не указывалось производителями до начала 80-х ( притом, что разработчики всегда хотели его знать ). Первое упоминание появилось в справочных данных на Шоттки и КМОП микросхемы. Там, где такое время не указывается, можно пользоваться эмпирическим правилом: время снятия можно считать равным времени предустановки 88 .

10.8.3 Особенности, определяемые технологией изготовления

В этом параграфе перечисляются неочевидные сложности и необычное поведение.

10.8.3.A Неочевидные сложности

ТТЛ микросхемы

Надо напомнить, что ТТЛ входы в НИЗКОМ состоянии являются источниками вытекающего тока ( 0.25 mA для «LS» и 0.5 mA для «F» ). Данное обстоятельство осложняет получение задержек на RC цепочках и т.п. приёмы, потому что источник сигнала для ТТЛ входа должен иметь низкий импеданс. По этой же причине надо проявлять повышенное внимание при подключении линейных схем к ТТЛ входам.

Порог переключения ТТЛ входов и семейств их имитирующих ( например, «HCT» и «ACT» ) расположен слишком близко к земле, уменьшая помехоустойчивость ( тема развивается в Части 12 ). Высокая рабочая частота таких схем делает их чувствительными к иголкам в цепях земли. Сами эти иголки возникают из-за слишком короткого времени переключения выходов, что только осложняет ситуацию.

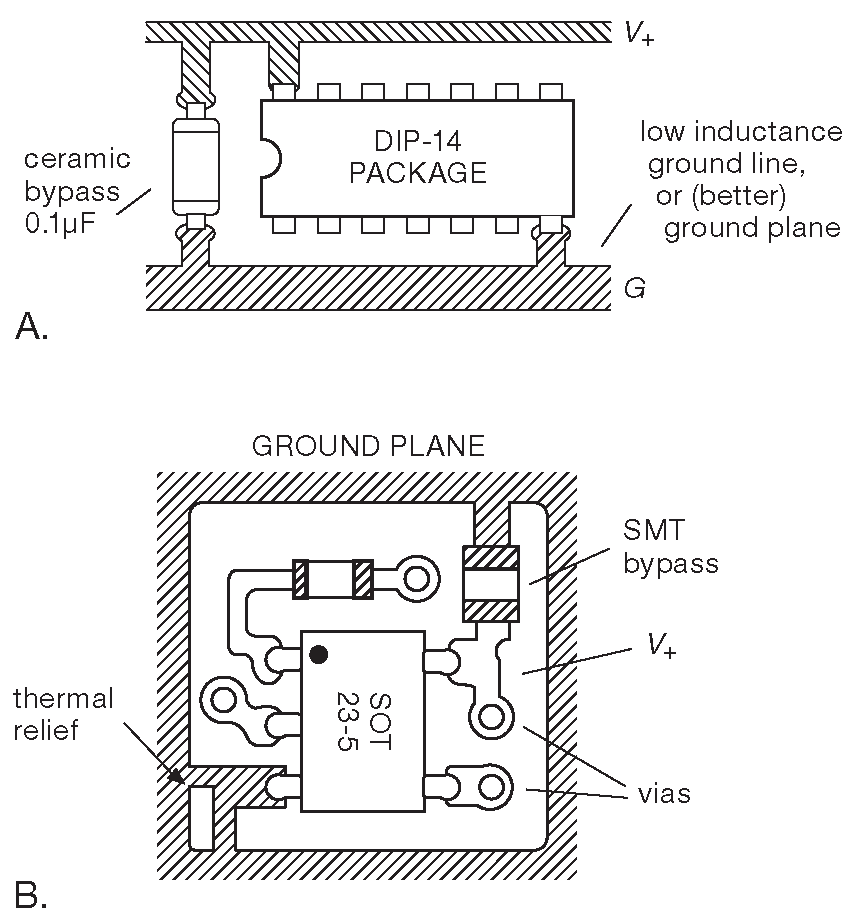

У биполярных ТТЛ серий высокие требования к источникам питания ( +5 V±5% при довольно высокой потребляемой мощности ). Броски и иголки по линии питания, вызванные активными выходными каскадами, требуют щедрого использования развязочных конденсаторов ( в идеале - отдельный конденсатор 0.1 μF на каждую ИМС, см. рис. 10.98 ).

Рис. 10.98 Использование мощных низкоиндуктивных линий земли и активное употребление развязочных конденсаторов - хорошее решение для любых схем. (A) Для недорогих двухслойных плат можно использовать гребёнчатую разводку питания. (B) Ещё лучше потратиться на многослойную плату, отвести сплошной слой земли и ставить конденсаторы в корпусах для поверхностного монтажа. Верхний слой обычно оставляют для сигнальных линий, а слои питания располагают внутри. ( Здесь слой питания расположен в верхнем слое для наглядности, но такой вариант подходит для двусторонних плат )

==759

КМОП

КМОП входы традиционно чувствительны к воздействию статических разрядов. Падёж таких микросхем увеличивается в зимнее время. Современные серии с поликремневыми затворами и цепями защиты стали гораздо устойчивее к повреждению, чем старые ИМС с металлическим затвором. КМОП входы имеют заметный разброс порога переключения, вызывающий сдвиг фронтов тактовых сигналов ( §10.8.2.C ). На выходах можно увидеть множественные переключения, когда на вход подаётся сигнал со слишком пологим фронтом [* см. §12.1.3.A ] . Все неиспользуемые КМОП входы в обязательном порядке необходимо подключать к корректному логическому уровню. То же относится и ко всем входам неиспользуемых логических элементов.

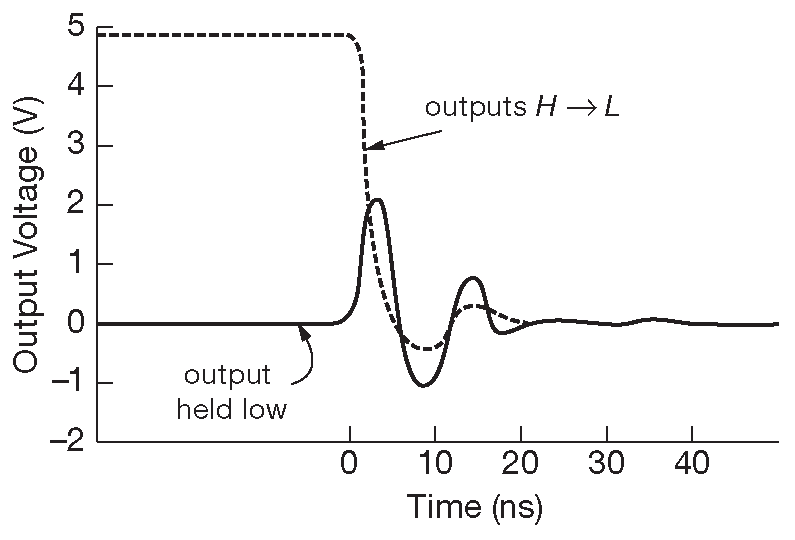

Интересной специфической особенностью КМОП являются выбросы в цепи земли . Быстрые КМОП выходы, нагруженные на большую ёмкость, вызывают сильные переходные токи в земляной шине, приводящие к колебаниям потенциала земляного вывода микросхемы и вместе с ним к колебаниям НИЗКОГО уровня на выходах, влияющие на непричастных соседей по кристаллу. На рис. 10.99 показано, что происходит. Обратите внимание на масштабы явления: выбросы от 1 до 2V не являются чем-то необычным! Если учесть, что длительность фронта 3 ns , то перепад 5V на нагрузке 50 pF требует \(I=C(dV/dt)\) =83 mA тока, а 8-битный буфер может работать на 8 таких нагрузок одновременно ( общий ток 2/3A ! ) такая картина не должна удивлять. Когда первые микросхемы AC(T) только появились, их начали упаковывать в корпуса DIP с традиционной угловой разводкой питания. Проблема выбросов по земле оказалась настолько острой, что её оказалось проще обойти. В итоге появилась новая серия с выводами питания по центру корпуса для снижения индуктивности. Кроме того, производители озаботились снижением скорости нарастания при переключении ( иногда называемой скоростью фронта ), а значит, и снижением тока перезарядки емкостей \(C(dV/dt)\). В семействах «AC(T)Q» ( “Q” - “quiet” ) проблема по большей части преодолена при очень небольшом снижении быстродействия.

Рис. 10.99 Выброс в шине земли. 74AC244 - 8-битный буфер переключает семь нагрузок по 50 pF с ВЫСОКОГО в НИЗКИЙ. Восьмая линия удерживается в НИЗКОМ состоянии. В качестве земли используется сплошной слой фольги ( 1 oz/ft2 ) [* 35 μm ] . Из руководства «TI Advanced CMOS Logic Designer’s Handbook»

Затем был предложен переход на корпуса для поверхностного монтажа ( с меньшей индуктивностью выводов ) и многослойные печатные платы с отдельными слоями земли и питания и развязочные конденсаторы в SMT корпусах. Для современных микросхем теперь указывают уровень создаваемого шума 89 . Большие интегральные схемы с большим количеством выводов иногда имеют десятки выводов земли 90 . Тем не менее, проблема «выбросов по земле» не побеждена, и разработчики должны её учитывать и проводить расчёты, стараясь снизить индуктивность шины земли насколько возможно ( рис. 10.98 ). Правильнее всего использовать печатные платы с отдельными слоями земли и питания и активнее ставить развязочные конденсаторы. Самое лучшее держаться от быстрых логических микросхем подальше, если нет серьёзных требований к скорости.

10.8.3.B Странное поведение

Биполярная логика

ТТЛ не склонна к асоциальному поведению 91 . Тем не менее, некоторые биполярные одновибраторы могут перезапускаться от помех по питанию и вообще слишком беспокойные. Схема, работающая с «LS» ТТЛ, может сбоить при замене микросхемы на «AS» ТТЛ. Последняя работает быстрее, т.е. имеет более резкие фронты и, соответственно, большие токи и звон в цепи земли ( «74F» в этом отношении лучше ). Большая часть проблем ТТЛ вызывается помехами.

ЭСЛ имеет очень малые времена переключения и любые связи длиной более нескольких сантиметров должны рассматриваться как линии передачи ( см. Приложение _H , §X1.1.4.C [* и §12.10 ] ).

КМОП

КМОП способны свести с ума кого угодно. Болтающийся в воздухе КМОП вход может вызывать в схеме случайные сбои. Щуп осциллографа, подключённый к нужной точке, показывает правильный уровень. Несколько минут устройство работает правильно, а затем вновь сбивается! Щуп осциллографа разрядил ёмкость затвора входного транзистора, и обратная зарядка, во время которой вход смещается к пороговому уровню, заняла какое-то время.

Ещё одним необычным явлением является «тиристорное защёлкивание» , вызванное кратковременным выходом напряжения на входе ( или выходе ) за уровни питания. Токовый импульс ( 50 mA или около того ) через защитные диоды включает пару паразитных встречно включённых транзисторов, образующихся на кристалле в качестве побочного элемента в технологии КМОП. Эта структура образует низкоомную связь между \(V_{DD}\) и землёй. Микросхема сильно нагревается, и требуется как можно быстрее снять питание, чтобы вернуть её в рабочее состояние. Если тиристорное защёлкивание продолжится дольше нескольких секунд, микросхему придётся заменить. Для некоторых новых КМОП семейств заявляется отсутствие тиристорного защёлкивания, даже если входы уйдут на 5V за уровни питания , и корректная работа для входных сигналов, уходящих на 1.5 V за уровни питания 92 .

==760

У КМОП микросхем бывает странный трудноуловимый отказ. Один из выходных транзисторов может быть в состоянии “fail open” , создавая чувствительное к сочетанию сигналов ошибочное состояние. Вход может начать потреблять или отдавать ток, а иногда вся микросхема начинает отбирать избыточную мощность. Резистор 1 Ω последовательно с выводом питания каждой микросхемы с развязкой со стороны вывода питания облегчает обнаружение аварийной микросхемы по избыточному потреблению. Для мощных драйверов или микросхем, тянущих много входов, можно ставить шунт 0.1 Ω . В большинстве случаев беспокоиться о таких вариантах не нужно, но для батарейного устройства, где микроамперы имеют значение, эта предосторожность может помочь.

Помимо различий порогового напряжения у разных микросхем, один кристалл может иметь разный уровень переключения на одном входе для разных выполняемых чипом функций. Например, вход «RESET» в CD4013 переводит вывод «/Q» в ВЫСОКОЕ состояние раньше, чем «Q» в НИЗКОЕ. Это означает, что снимать импульс сброса, опираясь на состояние «/Q» нельзя, потому что получившийся укороченный импульс может не сбросить триггер.

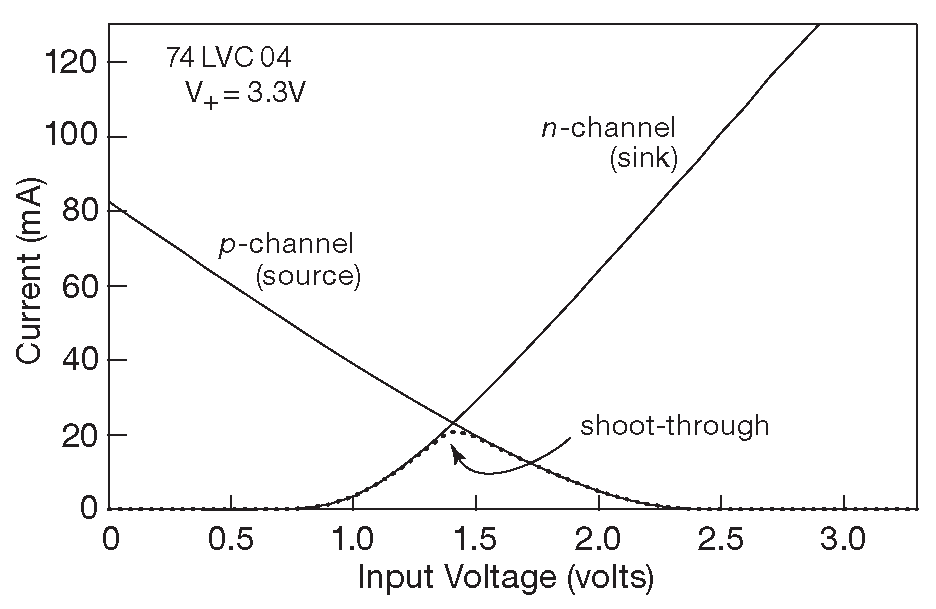

Висящие в воздухе входы - очень неприятная штука, даже если они относятся к неиспользуемому вентилю. Болтающийся вход смещается к середине питания, открывая p- и n-канальный транзистор одновременно. Появляется ток «класса-A», который превращается в ток покоя микросхемы ( у КМОП нулевой ток покоя, не забыли? ), а иногда просто выводит её из строя. Свободный вход может вызвать генерацию. Что происходит, видно на рис. 10.100 , где показаны результаты независимого измерения принимаемого и отдаваемого тока у одной секции 74LVC04 при +3.3 V . Если потенциал на входе оказывается ближе 0.7 V к любой линии питания, соответствующий МОП транзистор полностью закрывается. Но в промежутке между этими точками есть какая-то сквозная проводимость. На рисунке показана пиковая величина 20 mA при \(V_{IN}\) ≈ 1.4 V или 28 mW на один инвертор. Если в таком положении будут все шесть вентилей, то корпус начнёт рассеивать ∼200 mW . При питании +5V нагрев может разрушить кристалл.

Рис. 10.100 Ток, потребляемый одним элементом сшестерённого инвертора ’LVC04 ( пунктир ), как функция напряжения на входе. «Сквозной ток» - синоним для состояния одновременной проводимости ( короткого замыкания ) каналов обоих транзисторов, вызванного промежуточным уровнем сигнала на входе

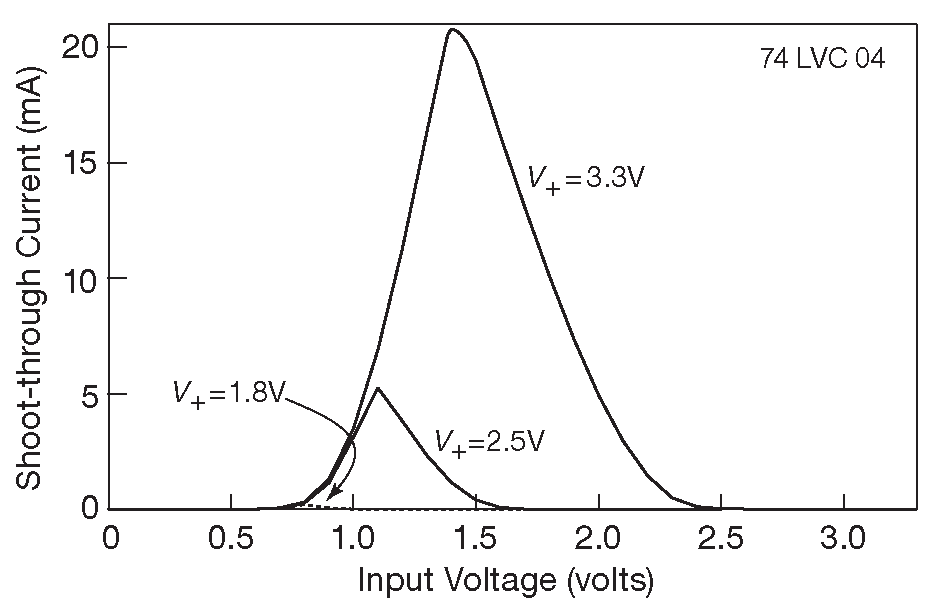

Максимальный сквозной ток жёстко связан с напряжением питания, что показывает рис. 10.101 . При очень низком напряжении просто нет уровня, при котором оба транзистора одновременно будут в проводящем состоянии.

Рис. 10.101 Сквозной ток ( ток короткого замыкания ) как функция уровня сигнала на входе для нескольких уровней питания

И, наконец, самая странная особенность. Если забыть подсоединить вывод питания КМОП микросхемы, то она будет работать! Питание начнёт поступать по одному из логических входов через защитный диод с вывода на шину питания. Такая ситуация может сохраняться довольно долго, пока в один прекрасный момент все логические входы не перейдут в НИЗКОЕ состояние. Микросхема лишится питания и забудет своё состояние. Ситуация плохая в любом случае. Выходные каскады не получают нужной мощности и не могут тянуть штатную нагрузку. Проблема в том, что проявляться такая неисправность будет случайно и при отладке можно сделать по схеме не один круг, прежде чем станет понятно, в чём дело.

==760

86 Шанс попасть на «интервал переключения» \(Δt\) более быстрого тактового сигнала ( промежуток, равный \(t_S\) до и \(t_H\) после фронта ) равен \(Δt/t_{CLKF}\) , где \(t_{CLKF}=1/f_{CLKF}\) - период более быстрого сигнала в паре асинхронных тактовый сигналов. Это значит, что медленный сигнал, тикающий с \(t_{CLKS}\) попадает в метастабильный интервал с частотой \(f_{CLKS}f_{CLKF}Δt\) в секунду. <-

87 Который, к сожалению, нельзя подключить к выходу внутренней логики. Правда можно вывести логический сигнал на внешний вывод и подать его на вход общего тактирования . <-

88 Оно обычно меньше. Например, для 74HC74 указывается минимальное время снятия от «/R» или «/S» до «CLK» 5 ns , а минимальное время предустановки 20 ns . <-

89 Его иногда называют «уровень тихого вывода» или «обратный звон» . Цифра показывает уровень наводки на выводе со стабильным логическим уровнем в момент, когда все остальные выходы переключаются. <-

90 Иногда и сотни. В FPGA Virtex-7 фирмы Xilinx в корпусе с 1761 выводом под землю отведено 423. <-

91 Циник заметил бы, что и хорошего в них мало. <-

92 Тиристорное защёлкивание возникает, когда входной ток превышает некоторый порог. Производители часто пишут, что защёлкивания не будет, если входной ток \(I_{IN}\) будет меньше, чем некоторый максимальный «уровень ограничения тока» , например, 20 mA . В справочных данных часто можно найти фразу о том, что «напряжение на входах и выходах могут превышать максимальные значения, если входные и выходные токи остаются в указанных пределах». Это хорошее известие, означающее, что можно использовать последовательные токоограничивающие резисторы для предупреждения тиристорного защёлкивания и расслабиться по поводу некоторого выхода напряжения за установленные рамки. <-