10.6 Типичные цифровые конструкции

==748

Благодаря заботам полупроводниковой индустрии разработка цифровых устройств сильно упростилась и стала очень удобной. Теперь практически никогда не требуется макетирование цифровых схем, по крайней мере, так же часто, как аналоговых. Грубо говоря, задержать могут только серьёзные сложности с временами и шумом. Тема разбирается в Части 12 .

Настал удобный момент для разбора нескольких цифровых схем последовательного действия. Некоторые из них можно собрать на микросхемах большой степени интеграции и программируемой логике, но предлагаемые варианты достаточно эффективны, наглядны и относятся к схемам, которые легко собрать из доступных компонентов без привлечения программных средств и формальных языков.

10.6.1 Счётчик «по-модулю-n»: разбор времён и задержек

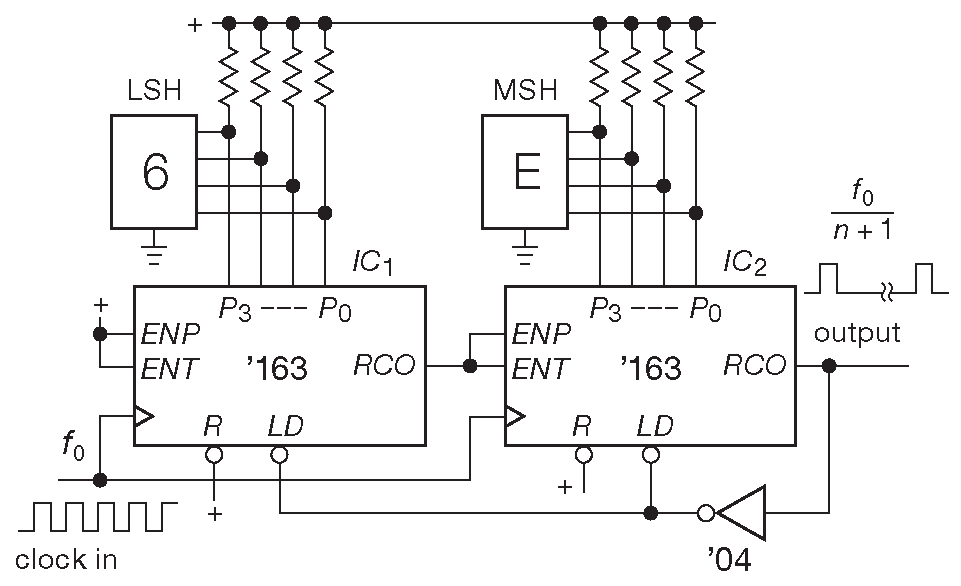

Схема 10.88 выдаёт один импульс на n+1 импульс на тактовом входе, где n - 8-разрядное число, выставляемое на паре дисковых переключателей. ’163 - синхронный 4-разрядный счётчик с синхронной загрузкой через входы «Pn» ( при НИЗКОМ «/LD» ). Требуется загружать в счётчик дополнение до нужного числа и досчитывать до 0xFF , производя перезагрузку при следующем тактовом импульсе. Входные уровни на линиях загрузки формируются подтяжками на шину питания ( переключатели подключены к земле ), т.е. сигналы для цифр на переключателях активные низкие. Если рассматривать их как активные высокие, то цифровые значения оказываются числами в виде дополнения до 1 [* побитовой инверсией ] для показаний переключателей.

Рис. 10.88 Счётчик «по-модулю-n» с коэффициентом пересчёта, устанавливаемым дисковыми переключателями

Упражнение 10.28

Покажите, что это правильное утверждение, выписав значения для активной высокой формы данных на ключах ( рис. 10.88 ).

Работа схемы очевидна. Для каскадирования синхронных счётчиков надо запараллелить их тактовые входы и подключить вывод «RCO» ( «счёт окончен» ) первого счётчика по входу разрешения счёта второго. Для считающего ’163 выход «RCO» переходит в ВЫСОКОЕ состояние, когда на триггерах появляется максимальное значение ( \(1111\space_2\) или \(1001\space_2\) ), разрешая работу следующего счётчика через выводы «ENT» или «ENP» [* на 1 такт ] . Таким образом, показания \(IC_1\) меняются в каждом такте, а \(IC_2\) один раз [* за 16 тактов ] , когда \(IC_2\) находится в состоянии 0xF . Такая пара будет считать до 0xFF и в этот момент будет активирован вход «/LD», что вызовет параллельную загрузку счётчиков на следующем такте. Для примера выбраны ИМС с синхронной загрузкой, чтобы избежать логических гонок ( и обрубленного импульса на выводе «RCO» ), которые неизбежно возникнут в счётчике с загрузкой прямого действия . К сожалению, в итоге получается схема, которая считает до n+1 , а не до n .

Упражнение 10.29

Объясните, что произойдёт, если ’163 с синхронной загрузкой заменить на ’191 с загрузкой прямого действия. Покажите механизм образования укороченного импульса. Покажите, что предложенная схема делит на n+1 , а асинхронный вариант, если заработает, будет делить на n .

10.6.1.A Временная диаграмма

С какой скоростью может работать счётчик «по-модулю-n»? Будем использовать семейство «LV» с питанием +3.3 V . Для 74LV163A указана гарантированная частота \(f_{max}\) =70 MHz 75 . Но в схеме есть две дополнительные задержки. Они обусловлены каскадным соединением, которое позволяет передать \(IC_2\) разрешение на счёт и временем передачи сигнала параллельной загрузки при переполнении. Чтобы найти максимальную рабочую частоту, на которой схема гарантированно будет работать, следует добавить задержки для наихудшего случая и убедиться, что результат не заходит за время предустановки данных. ВременнАя диаграмма для максимальной скорости счёта показана на рис. 10.89 .

Рис. 10.89 Расчёты максимальной частоты переключения для схемы 10.88

==750

Переход НИЗКИЙ-ВЫСОКИЙ на любом из выходов «Q» отстаёт от фронта «CLK» на 15 ns max. Это интересно, но не более, т.к. сигнал загрузки использует другой путь - через «RCO». В \(IC_1\) «RCO» отстаёт от фронта «CLK» на 16 ns max. [* это уже опускает частоту до 60 MHz c хвостиком ] . Далее он проходит в \(IC_2\) через «ENT»/«ENP» и добирается до «RCO» за 14.5 ns ( предполагаем, что максимума она уже досчитала ). [* Осталось менее 30 MHz ] . LVC1G04 формируя «/LD» добавляет ещё 3.3 ns . Он должен попасть на входы \(IC_1\) и \(IC_2\) , не позднее чем за 9.5 ns до очередного фронта. Таким образом, получаем 1/\(f_{max}\) =(16+14.5+3.3+9.5)=43.3 ns, а \(f_{max}\) =23.1MHz . Цифра существенно меньшая, нежели гарантированная скорость работы одиночного счётчика 74LV163A - 70 MHz .

Упражнение 10.30

Проведите такие же расчёты и покажите, что максимальная скорость синхронно каскадированных 74LV163A без использования загрузки составляет 40 MHz . Справочные данные на сайте TI.

Безусловно, если требуется больше скорости, можно поискать микросхемы и побыстрее. Расчёты для «74F» ( скорость одиночного 74F163 100 MHz ) даёт \(f_{max}\) =29 MHz . Вот тут-то ЭСЛ логика отыгрывается по полной. MC100E016 - 8-разрядный синхронный счётчик с загрузкой имеет скорость \(f_{max}\) =700 MHz (!). А какова будет скорость счётчика «по-модулю-n»? Для имеющихся 8 разрядов каскадирования не требуется, тем не менее, выход окончания счёта ( «/TC» ) - активный низкий, и такой же активный низкий вход параллельной загрузки «/PE». Задержка «CLK»→«/TC» менее 0.9 ns , а время предустановки «/PE»→«CLK» 0.6 ns , что даёт в формате «по-модулю-n» скорость 667 MHz . Неплохо. Но можно чуть подтянуть. Счётчик проектировался с учётом такого рода задач и имеет специальный вход «загрузка по окончании счёта». Переведя его в разрешённое состояние [* активировав внутренние связи ] можно убрать всякую задержку и получить гарантированные 700 MHz ( типичное значение 900 MHz ) для режима деления «по-модулю-n». Это в 30 раз лучше, чем вполне приличная схема на КМОП элементах.

Поклонникам счётчиков «по-модулю-n» стоит обратить внимание на ’HC40103 - 8-разрядный обратный счётчик с двумя типами загрузки: и с синхронной, и с асинхронной ( прямой ), выходом окончания счёта ( =0 ) и входом установки на максимум.

==751

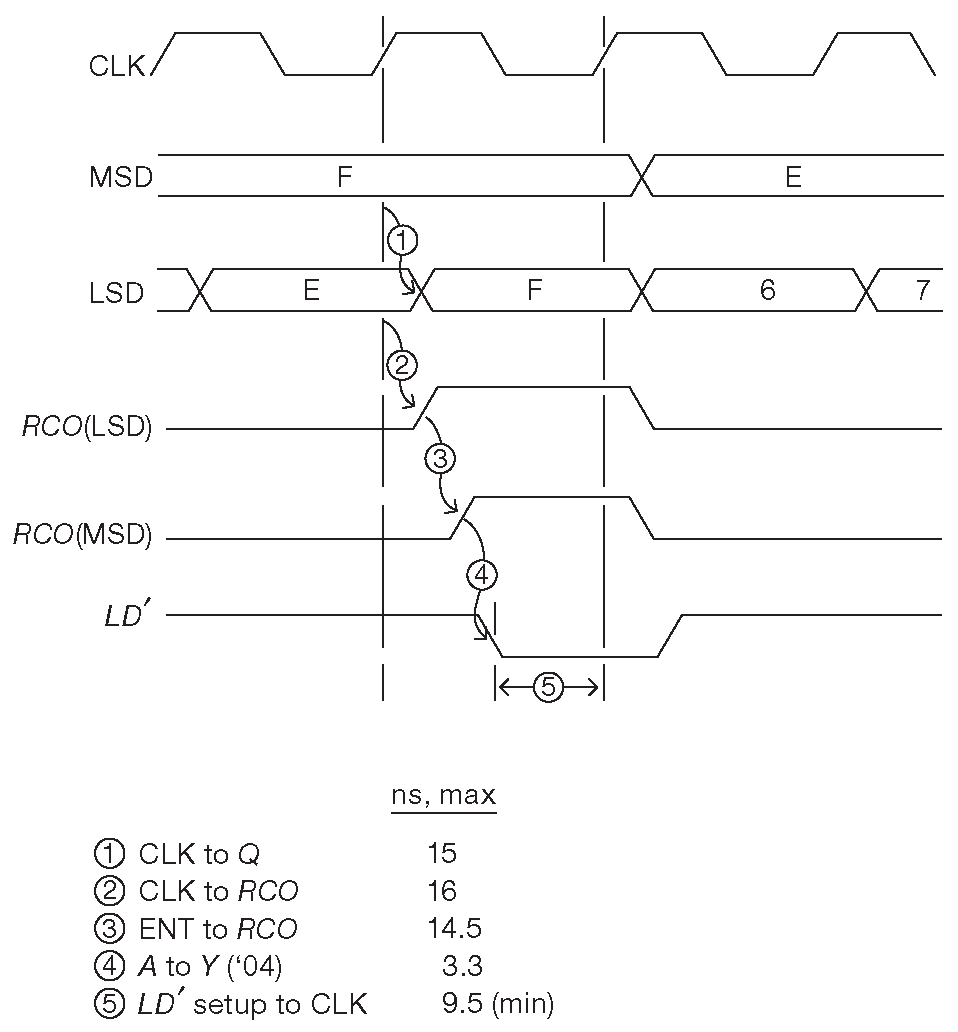

10.6.2 Многопозиционный мультиплексированный дисплей

Пример объясняет технику мультиплексирования символьных индикаторов. Число из n символов можно отображать, кратковременно выводя один знак за другим на соответствующее знакоместо индикатора. Мультиплексирование позволяет уменьшить число связей и упростить схему. Представьте только, постоянное отображение символа требует отдельный драйвер, декодер и токоограничительные резисторы на каждое знакоместо, полный набор соединений между этими компонентами. Плюс соединения между декодером и регистром. Ужас сколько всего!

При мультиплексировании есть только один декодер/драйвер и один набор токоограничивающих резисторов. Более того, светодиодные индикаторы выпускаются в виде многоразрядных линеек с запараллеленными сегментами разных цифр. В такой конфигурации число связей сильно уменьшается. Скажем, 8-символьный 7-сегментный мультиплексированный индикатор требует всего 15 линий ( 7 проводов от сегментов и по одной индивидуальной линии от каждого знакоместа ), вместо 57 ( 7×8+1 ), которые понадобятся при статическом управлении. Кроме того, многоразрядные индикаторы выпускаются только в мультиплексированном исполнении.

Схема показана на рис. 10.90 . Отображаемые цифры хранятся в регистрах ( нижняя линейка прямоугольников ). Это могут быть счётчики ( если речь идёт о частотомере ) или регистры, фиксирующие данные от процессора, или информация с АЦП и т.д. В любом случае требуется последовательно выводить цифры на внутреннюю 4-разрядную шину ( в данном случае через буфера с третьим состоянием ’HCT244 ), декодировать и отображать через ’HC4511 - преобразователь BCD в 7-сегментный код и драйвер для индикатора.

Рис. 10.90 Мультиплексированный дисплей на 4 символа

==752

На паре инверторов собран классический КМОП генератор ( рис. 7.2 ), выдающий частоту 1 kHz на десятичный счётчик/декодер ’HC4017. Активные высокие выходы ’HC4017 выводят на шину нужную цифру и одновременно переводят в НИЗКОЕ состояние вывод соответствующего катода. Здесь задействован популярный сильноточный драйвер ULN2003 на парах Дарлингтона. ’HC4017 закольцован на самосброс в состоянии «4» после прохода через состояния «0»...«3». RC цепь добавлена, чтобы гарантировать полный сброс. Мультиплексирование хорошо работает с большим числом цифр и повсеместно используется в приборах с многоразрядными индикаторами. Если быстро скользить взглядом вдоль ряда цифр, можно заметить свечение отдельных разрядов.

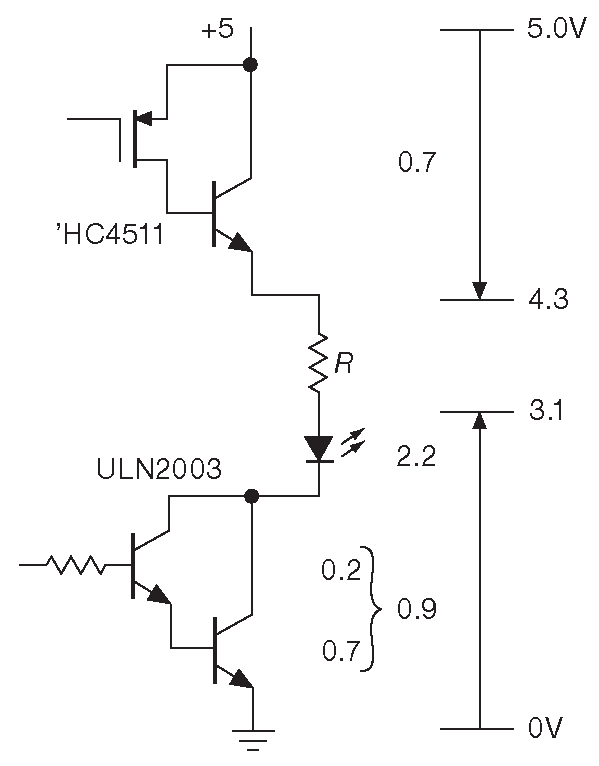

В ходе разработке требуется разобраться с «бюджетом светодиода». Имеется источник +5V и индикатор с падением напряжения на зажжённом сегменте ∼2.2 V при 10 mA . Казалось бы, никаких проблем, но внимательное рассмотрение показывает узкое место ( рис. 10.91 ). Выходной драйвер анодов в ’HC4511 относится к гибридному типу p-МОП + npn и имеет падение 0.7 V ( \(V_{BE}\) ), а драйвер ULN2003 на паре Дарлингтона, забирающий 70 mA имеет ещё одно \(V_{BE}\) плюс напряжение насыщения - всего около 0.9V . Если добавить светодиод ( 2.2 V падения 76 ), то на токоограничивающий резистор останется только 1.2 V . Для 10 mA через сегмент понадобится резистор 120 Ω . С этой стороны проблем нет, но нельзя забывать о некотором разбросе прямого падения на светодиодах. Чем меньше напряжения приходится на резистор, тем сильнее процентное изменение этого напряжения от вариаций прямого падения на светодиоде, что в свою очередь ведёт к сильной разнице яркости сегментов. Если и сейчас непонятно, то подсчитайте эффект от 10%-разницы падений при общем питании +5V . Кроме того, ’HC4511 вообще не работает при +3.3 V 77 .

Рис. 10.91 Бюджет напряжения драйвера светодиода

В светодиоде максимально допустимый ток через переход ограничивается только нагревом, поэтому в многоразрядных индикаторах можно использовать большие пиковые токи, пока средний ток через сегмент остаётся в допустимых пределах. В этом вопросе требуется аккуратность, потому что температурная постоянная времени для мелких светоизлучающих кристаллов лежит в районе миллисекунды. Поэтому для сколь-нибудь продолжительного времени протекания ток не может существенно превышать допустимый средний ток. Ещё один способ сжечь светодиод - завесить драйвер во включённом состоянии, например, из-за программного сбоя при отладке дисплея с управлением от микроконтроллера 78 .

Многие БИС, ориентированные на задачи отображения, которые ставят в бытовую технику ( часы, телевизоры и т.п. ) имеют в своём составе схемы мультиплексирования, а часто и драйверы. Можно найти старый драйвер- мультиплексор на 6 цифр 74C912, но это непросто 79 . Он принимает 4-битовые слова в нужной последовательности и требует наличия внешнего драйвера разрядов.

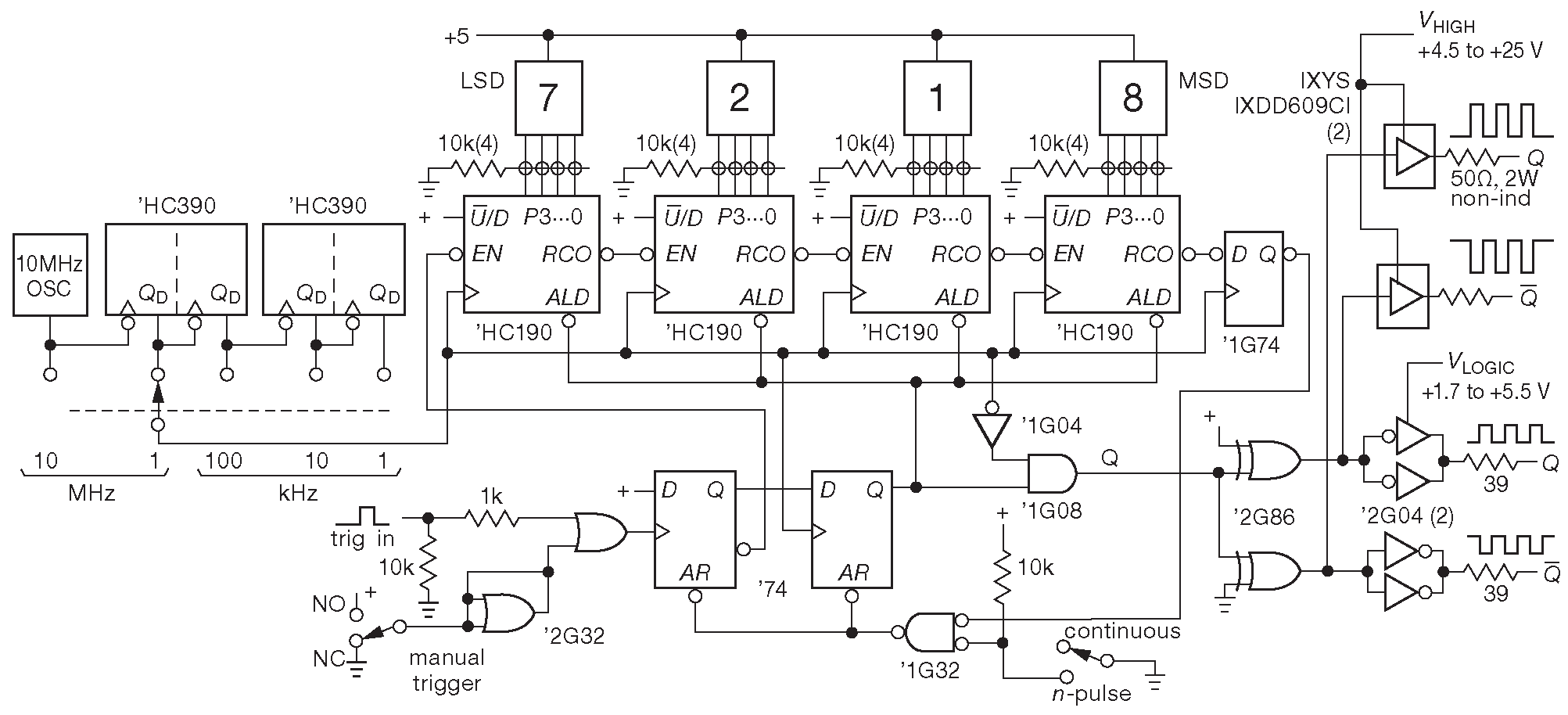

10.6.3 Генератор последовательности из n импульсов

Генератор последовательности импульсов довольно удобный инструмент. В ответ на запускающий сигнал ( или нажатие кнопки ) он выдаёт n импульсов с регулируемой частотой следования. Схема показана на рис. 10.92 80 . ’HC190 - десятичный реверсивный счётчик, включённый для счёта вниз. На него постоянно подаётся частота, получаемая делением исходного генератора на 10 MHz . Исходно счёт выключает активный вход асинхронной загрузки «/ALD» и одновременно пассивный сигнал разрешения счёта «/EN». Когда приходит запускающий импульс, первый триггер [* асинхронно ] разрешает счёт, а второй синхронизирует снятие сигнала параллельной загрузки с восходящим фронтом тактового импульса. Импульсы проходят через схему «И», пока счётчик не досчитает до нуля. В этот момент активируется выход «/RCO», который защёлкивается на один такт внешним триггером 81 и сбрасывает оба триггера запуска. Это событие вызывает запрет счёта и параллельную загрузку в счётчики значения «n–1», выставленного на дисковых переключателях 82 в ожидании следующего запускающего события. Отметим использование прямого, а не дополнительного, как на схеме 10.88 , кода ( и подтягивающих к земле резисторов ). Кроме того, кнопка ручного запуска должна защищаться от дребезга, т.к. линия идёт на тактовый вход триггера [*] . Для переключателя «n импульсов/непрерывно» такая защита не нужна.

Рис. 10.92 Идеальный генератор последовательности из n импульсов. Где не указано иное используется серия «LVC». Питание +5V

[*]

[* Дело не в тактовом входе триггера. Это как раз хороший способ защиты от дребезга: триггер перебросился один раз и больше на активный фронт не реагирует. Но проблема в том, что, если тактовая частота велика, а импульсов мало, то между сменами уровней на дребезге может быть достаточно времени для отработки полного цикла генератора с возвратом в ждущий режим. Тут-то триггер и переключится снова ].

==753

На выход идут сигналы обеих полярностей, которые формируются элементами «ИСКЛЮЧАЮЩЕЕ-ИЛИ» и имеют одинаковую задержку. Запараллеленые инверторы ’LVC2G04 выдают сигнал с полным размахом от 0 до \(V_{LOGIC}\) и могут меняться от +1.7 до +5.5 V через внешний блок питания. Два параллельных инвертора позволяют получить ток до 32 mA , не отходя при этом более чем на 0.5 V от уровней питания ( при \(V_{LOGIC}\)=+3V ). Резисторы 39 Ω в паре с выходным сопротивлением драйвера ( ∼10 Ω ) образуют цепь последовательного согласования для 50-омного кабеля.

Кроме того, добавлена пара мощных выходов. Здесь стоят сильноточные «драйверы затворов», предназначенные для быстрого переключения затворов мощных МОП транзисторов, имеющих большую ёмкость. Указанные микросхемы тянут до 8A и имеют среднее время переключения ∼10 ns . Драйверы неинвертирующие и управляются сигналами 5-вольтовой логики. На выходах стоят последовательные согласующие резисторы 50 Ω 2W с низкой индуктивностью 83 .

==753

75 Вентиля ’1G04 в серии «LV» нет, поэтому взят 74LVC1G04. <-

76 Это данные для использованного индикатора жёлтого цвета. Прямое падение на светодиодах зависит от цвета их свечения, см. рис. 2.8 . <-

77 Или с +5V и синими светодиодами, у которых прямое падение \(V_f\) ≈ 3.5 V . <-

78 См. §7.2.3 , где показан способ борьбы с этой напастью. <-

79 У Jameco их можно найти за $2 в розницу. <-

80 Загадка: почему схема названа «идеальной»? <-

81 Это выход асинхронного сигнала завершения счёта , который для обратного счётчика, как здесь, отмечает состояние 0000 . Особенностью ’190 является «/RCO», появляющийся только когда на тактовом входе НИЗКИЙ уровень. <-

82 Из-за защёлки на выходе «/RCO» схема выдаёт на один импульс больше, чем показывают переключатели. Если фиксацию убрать, то логический недостаток превратится в схемотехнический , т.е. появится укороченный импульс в конце последовательности. Разберитесь, почему это происходит. Исключение инвертора убирает обрезанный импульс, но сильно укорачивает импульс параллельной загрузки, оставляя один лишний импульс в серии. Сигнал загрузки, длительность которого определяется только временем распространения, криминалом не является, но просто неудобен . Фиксированный «/RCO» для асинхронной загрузки красив и отлично виден на осциллографе. [* Все слова про инвертор после предложения разобраться относятся к схеме на рис.8.92 на стр.551 во втором издании, изображающей предыдущую версию генератора ] . <-

83 Читателям, возжелавшим повторить схему, следует учесть, что есть очень приятная альтернатива набору ’190 ( или ’192 ). Это ’HC4059 - 16-битный обратный счётчик с перезагрузкой, который в одиночку перекроет всю цепочку. Но он двоичный ( или шестнадцатеричный ) и похож на ’191. <-