11.1 Краткая история вопроса

==764

Первым программируемым логическим устройством ( 1975 ) была «интегрированная логика на пережигаемых перемычках» фирмы Signetics. Она представляла собой набор вентилей и матрицу предохранителей ( в буквальном смысле ), которые надо было пережигать по определённой процедуре, оставляя только нужные соединения. «Программировались» такие микросхемы составлением таблицы нужных соединений. Позднее такая таблица строилась уже на экране компьютера. В ходе доработки технологии Signetics добавила в набор триггеры, что позволило строить логику последовательного действия. Monolithic Memories предложила упрощённое семейство с торговым названием «Программируемая матричная логика» ( PAL ) с более удобным для использования языком описания схем PALASM. В середине 80-х появились «Универсальная матричная логика» ( GAL ) фирмы Lattice, в которых использовалась память с электрическим стиранием-программированием и специальные выходные ячейки, для которых можно было выбрать функцию регистра или простого вентиля. Появились и улучшенные языки программирования CUPL и ABEL. Они и все их последователи объединяются собирательным названием «языки описания аппаратуры» ( HDL ).

Примерно в то же время фирма Xilinx представила «программируемые пользователем вентильные матрицы» ( FPGA ). Это была альтернатива с более мелкой структурой: гораздо большее количество вентилей и регистров объединялись в более крупные логические блоки. По периметру кристалла располагались блоки ввода-вывода. Все элементы ИМС были связаны между собой многочисленными каналами передачи. Полная информация о связях между элементами хранилась во внешней микросхеме памяти ( последовательная «конфигурационная» память ) и загружалась в FPGA после подачи питания.

PLD постоянно усложнялись и улучшались со временем и сейчас входят в обязательный набор разработчика. Современные cPLD ( c - complex ) имеют от 32 до 2000 макроячеек с десятками тысяч вентилей, работают на скоростях сотни мегагерц. Их конфигурационная память находится внутри кристалла и может перезаписываться внутрисхемно через последовательный порт JTAG. Есть варианты с нулевым статическим током потребления _2 . cPLD имеют хорошо предсказуемое быстродействие.

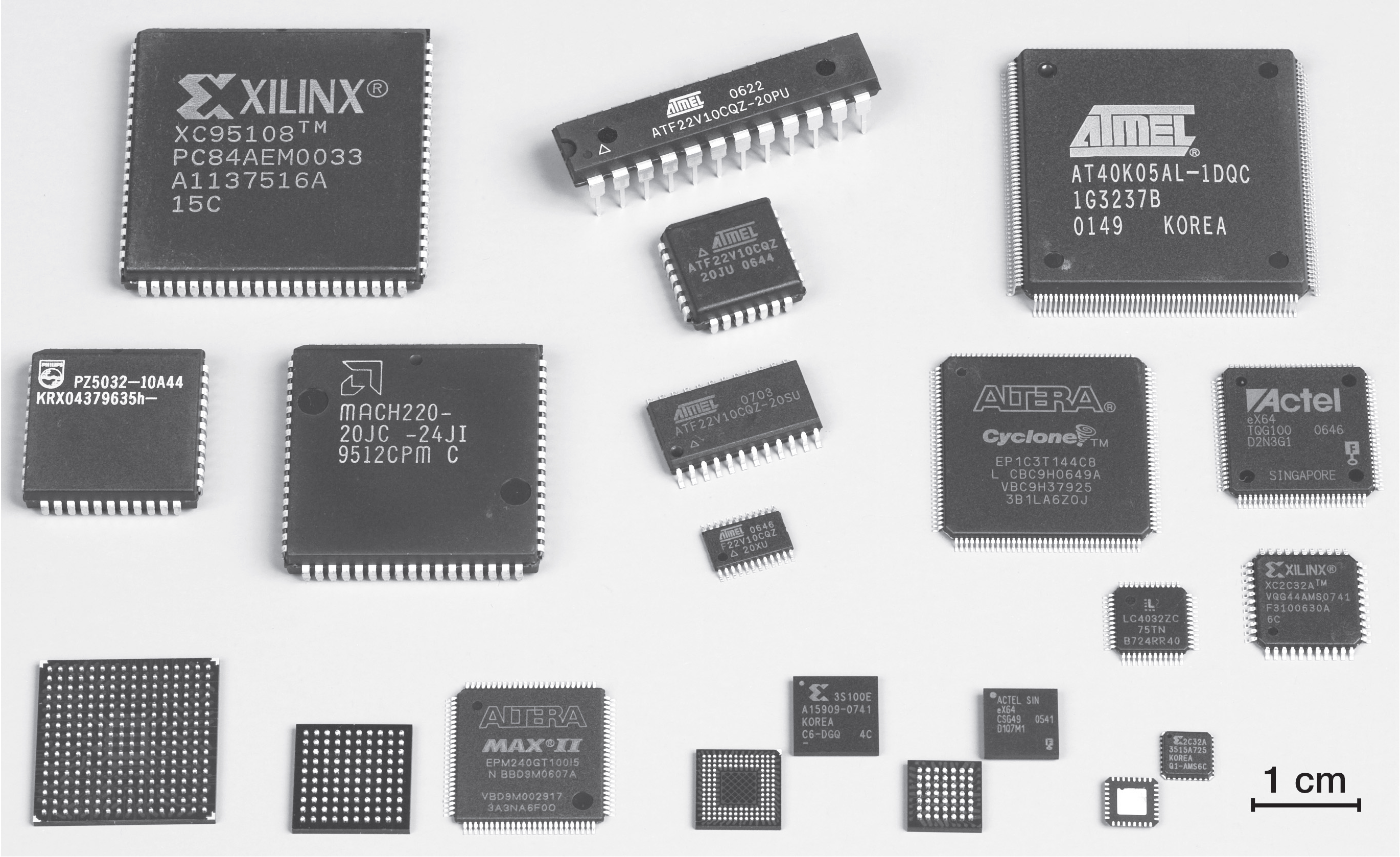

Гораздо более ёмкие FPGA далеко шагнули за границу миллион триггеров на корпус ( рис. 11.1 ), в котором, кстати, могут быть тысячи (!) выводов. В состав могут входить блоки дополнительной памяти, поддержки вычислений, интерфейсов и специальных функций. Столь широкие возможности породили новый стиль проектирования, когда активное использование типовых периферийных блоков, например, видео процессоров, контроллеров PCI, Bluetooth и даже законченных микропроцессоров превратилось в рутинную процедуру. Всё вместе называется «системой-на-кристалле» ( SOC ), а законченные отлаженные программные блоки - «IP» - интеллектуальной собственностью, на использование которой требуется лицензия. Если в проекте используется IP микропроцессора, то такой µC называется «программным ядром» [* как противоположность «аппаратному ядру» в обычном контроллере ] _3 . Существует альтернатива в виде гибридной FPGA, содержащей на кристалле настоящий аппаратный процессор и периферию _4 .

Рис. 11.1 Некоторые примеры корпусов программируемой логики. Вверху слева три PLCC ( 84, 68 и 44 вывода ), а в правом углу напротив них - более многоногие собратья. По часовой стрелке с самого большого: PQFP-208, TQFP-100, VQFP-44, TQFP-48 и TQFP-144. В центре сверху вниз представлены cPLD 22V10: DIP-24, PLCC-28, SOIC-24 и TSSOP-24. Нижний ряд слева направо : FTBGA-256, FBGA-100 ( и та же ИМС в TQFP-100 ), BGA-132, BGA-49 ( CSP-49 ) и QFN-32 ( три последних корпуса с обеих сторон )

==765

Для столь сложных компонентов прежние языки программирования CUPL и ABEL, рассчитанные на небольшие кристаллы cPLD совершенно бесполезны _5 . Сейчас разработчики используют или графический ввод, или один из современных языков описания аппаратуры ( Verilog или VHDL ). Чуть позже оба будут использоваться в примерах. Для большей части цифровых схем программируемая логика удобнее стандартной, потому что одна микросхема заменяет горсть корпусов. В итоге получается меньше внешних связей, компактнее плата, удобнее складской учёт и ниже цена. Кроме того, схемы на таких ИМС проще менять: достаточно изменить прошивку, и вот уже исправлена ошибка, или появилась новая функция.

==765

2 Особенно серия CoolRunner™ ( Xilinx, изначально Philips ) и ispMACH™4000Z ( Lattice ). <-

3 Примеры: MicroBlaze ( Xilinx ), Nios-II ( Altera ), Mico ( Lattice ) и ARM ( Actel ). <-

4 Примеры: PowerPC ( Xilinx ), AVR ( Atmel ) и ARM ( Altera ). <-

5 Классические малые sPLD ( s - simple ) 16V8, 20V8, 22V10 и 26V12, для которых CUPL и ABEL вполне адекватны, по-прежнему производятся и продаются. <-